介紹

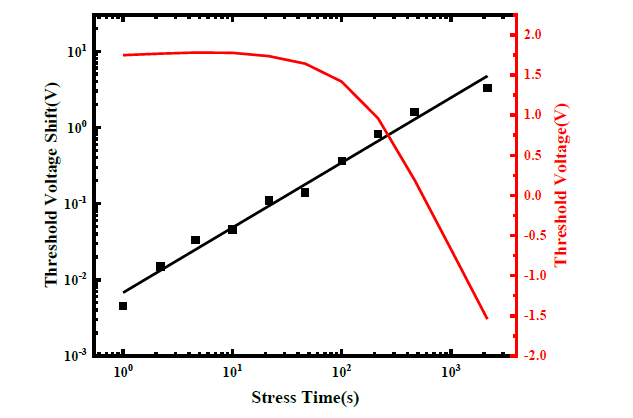

閾值電壓 (Vth)是 MOSFET (金屬氧化物半導體) 的一種基本的電學參數(shù)。閾值電壓 (Vth) 為施加到柵極的最小電壓,以建立MOSFET漏極和源極端子之間的導電溝道。有幾種方法可以確定閾值電壓:根據(jù)器件的傳輸特性、漏極電流 (ld) 與柵極電壓 (Vg) 曲線。在測試碳化硅 (SiC) MOSFET時,正向柵極電壓掃描和反向柵極電壓掃描都表現(xiàn)出滯后效應。這種效應主要是由于陷阱引起的,并導致閾值電壓的偏移。這種閾值電壓的差異會影響一些器件參數(shù),如漏電流和導通電阻。

為了減小或降低閾值電壓的滯后性,JEDEC (Joint Electron Device Engineering Council,聯(lián)合電子器件工程委員會)引入了JEP183A標準為測量SiC MOSFET的閾值電壓提供了指導。這個標準描述了如何確定閾值電壓的方法,即:在產(chǎn)生漏極電流和柵極掃描電壓之前用調(diào)節(jié)脈沖。

從Clarius+ V1.14軟件套件發(fā)布開始,基于JEP183A標準的SiC MOSFET閾值電壓測試已包含在4200A-SCS參數(shù)分析儀中。這些測試使用兩個源測量單元 (SMU),通過Clarius軟件執(zhí)行。

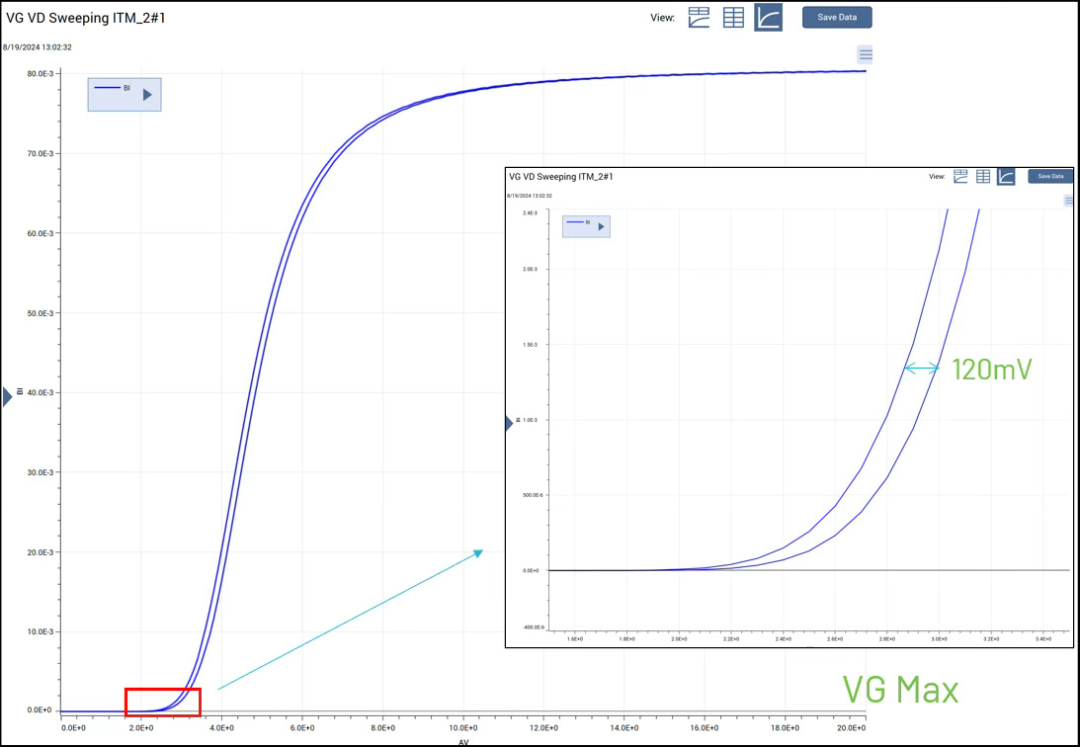

圖1. 硅碳化物MOSFET的ld與Vg曲線表現(xiàn)出滯后效應

本應用說明討論了:根據(jù)JEDEC JEP183A標準,使用4200A-SCS參數(shù)分析儀,對SiC MOSFET進行精確的閾值電壓測量。

JEDEC JEP183A標準

JEDEC JEP183A標準“SiC MOSFET 閾值電壓 (Vt)測量指南”解決了硅MOSFET上使用的傳統(tǒng)測試方法所表現(xiàn)出的滯后效應。遲滯是由于SiC器件中SiC/SiO2界面中的陷阱數(shù)量增加引起的,這導致正向和反向掃描之間的傳輸曲線發(fā)生偏移。

可以通過將柵極電壓從0V掃描到最大柵極電壓,然后再掃描回0V來觀察遲滯。圖1所示的SiC MOSFET漏極電流與柵極電壓曲線證明了這種效應。在本例中,觀察到正向曲線和反向曲線之間存在約120mV的差異。這些掃描是使用Clarius交互式軟件生成的。

為了解決滯后效應,將調(diào)節(jié)脈沖施加到柵極,以幫助在向下柵極電壓掃描之前釋放陷阱。JEDEC JEP183A標準建議將調(diào)節(jié)脈沖設置為最大柵極電壓。

JEP183A標準描述了SiC MOSFET閾值電壓測量的三種不同方法。所有方法最初都在柵極上輸出調(diào)節(jié)脈沖,但隨后施加柵極和漏極電壓的方式不同。這三種推薦的測試方法是:

■掃描柵極電壓和固定漏極電壓法

■掃描柵極和漏極電壓法

■固定柵極和漏極電壓方法

這些方法的詳細信息在JEP183A標準中進一步描述。Clarius庫包括用于執(zhí)行前兩種方法以提取閾值電壓的測試。以下段落解釋如何使用這些Clarius庫測試。

使用4200A-SCS進行SiC MOSFET閾值電壓測量

設置和執(zhí)行閾值電壓測試涉及到器件的硬件連接并使用Clarius軟件配置和執(zhí)行測試。

硬件連接

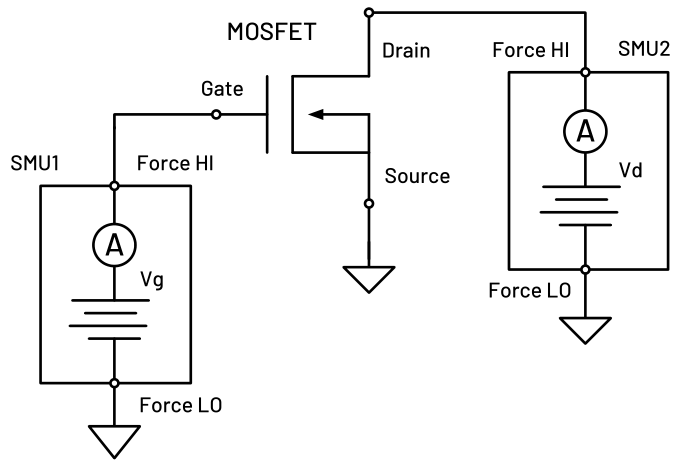

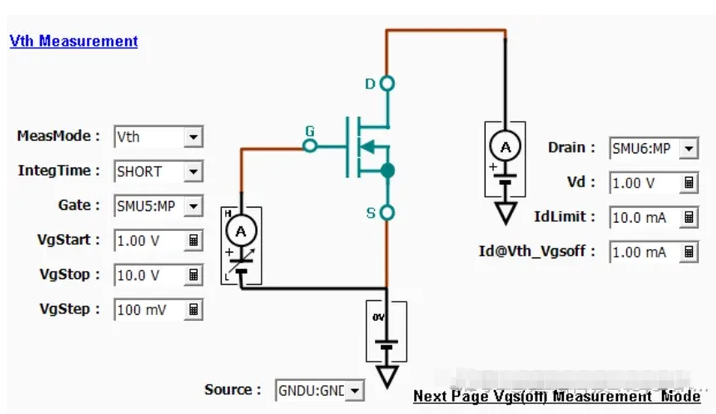

兩個SMU和接地單元 (GNDU) 用于執(zhí)行閾值電壓測試,如圖2中的基本電路圖所示。兩個SMU都處于施加電壓和測量電流模式。一個SMU (SMU1) 的Force HI端子連接到MOSFET的柵極端子,并施加柵極電壓 (Vg),包括調(diào)節(jié)脈沖和向下電壓掃描。第二個SMU (SMU2) 施加固定或掃描漏極電壓 (Vd) 并測量漏極電流 (Id) 。Force LO (GNDU) 連接到MOSFET的源端。

電路示意圖圖中未顯示連接到MOSFET的SMU和GNDU Sense HI和LO端子。同時使用施加(Force)和感測(Sense)端子可以與DUT進行四線(或開爾文)連接,以消除引線電阻影響測量精度。

圖2. 功率MOSFET的柵極和漏極上SMU的連接示意圖

使用 Clarius軟件進行SiC MOSFET閾值電壓測量

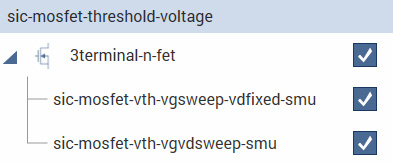

用于進行SiC閾值電壓測量的測試在測試庫和項目庫中都有,可以通過搜索短語“SiC MOSFET”在Clarius界面的“選擇”視圖中找到。在測試庫中找到測試后,可以選擇它們,然后將其添加到項目樹中。測試庫包括兩種方法的測試 (sic-mosfet vth-vgsweep-vd?xed-smu和sic-mosfet-vth-vgvdsweep-smu)。如圖3的項目樹所示,這兩個測試也包含在項目庫中的項目sic-mosfet-threshold-voltage中。這些測試將在以下段落中進一步描述。

圖3. SiC MOSFET閾值電壓項目樹

掃描柵極電壓和固定漏極電壓法

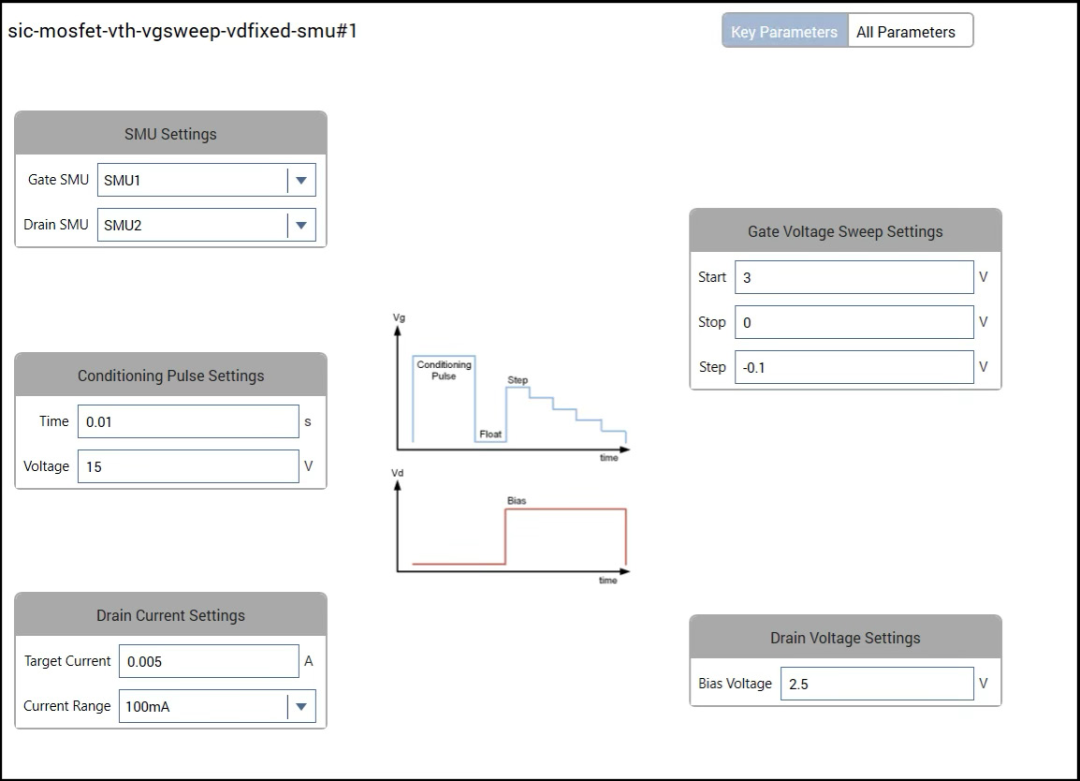

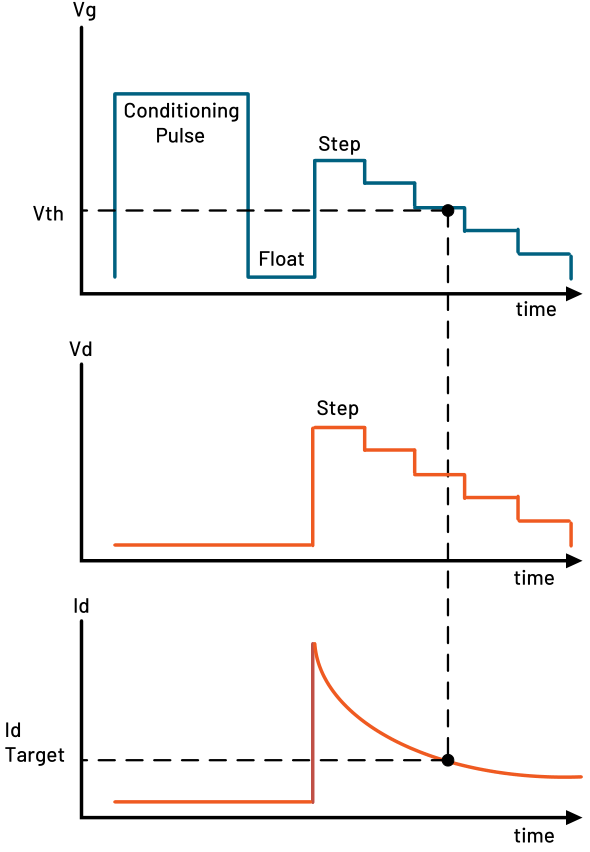

第一個測試是sic-mosfet-vth-vgsweep-vd?xed-smu,它使用掃描柵極電壓和偏置漏極電壓方法,該方法使用SMU1向柵極 (Vg) 施加調(diào)節(jié)脈沖,然后向下掃描柵極電壓 (SMU1),同時固定漏極A電壓 (SMU2)。漏極電流由SMU2測量,并繪制為柵極電壓的函數(shù)。該測試的柵極電壓 (Vg)、漏極電壓 (Vd) 和漏極電流 (Id) 時序圖如圖4所示。

時序圖中還顯示了Vg圖上的閾值電壓 (Vth) 和Id圖上的目標漏極電流(Id目標)。根據(jù)用戶定義的目標漏極電流 (Id Target),使用線性插值計算閾值電壓 (Vth)。

圖4.sic-mosfet-vth-vgsweep-vd?xed-smu測試項的柵極電壓,漏極電壓和漏極電流的時間曲線

測試的輸入?yún)?shù)在Clarius的“配置”視圖中設置,如圖5所示。該測試具有配置調(diào)理脈沖、目標漏極電流、漏極電流測量范圍、柵極電壓掃描和漏極電壓偏置的設置。此測試的所有輸入和輸出參數(shù)都列在附錄A的表格中。

圖5.sic-mosfet-vth-vgsweep-vd?xed-smu測試項的配置視圖

JEDEC JEP183A標準建議將調(diào)節(jié)脈沖的幅度設置為最大柵極電壓。電壓掃描的步長應保持較小(0.1 V),以進行準確的閾值電壓計算。

該測試方法中的時間參數(shù)要求調(diào)節(jié)脈沖設置在1到100ms之間,并且用戶可調(diào)。浮動時間是調(diào)節(jié)脈沖結(jié)束和反向掃描開始之間的時間,不可調(diào)節(jié)。

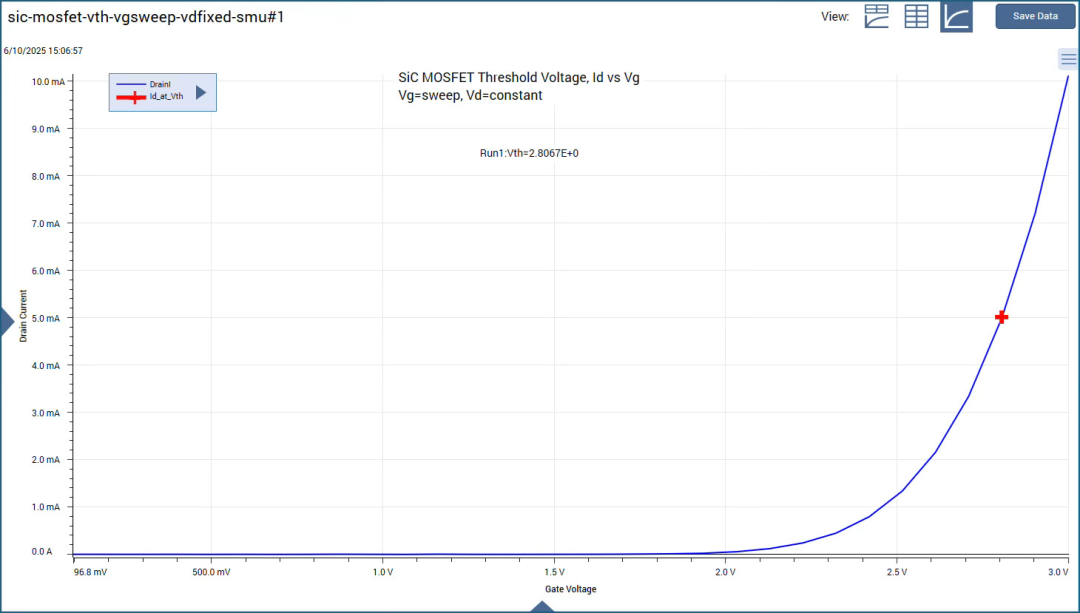

執(zhí)行測試時,漏極電流在分析視圖圖中繪制為柵極電壓的函數(shù),如圖6所示。導出的閾值電壓在圖表上表示為紅叉。

圖6.sic-mosfet-vth-vgsweep-vd?xed-smu測試項的Id-Vg曲線中顯示Vth

圖7顯示了泰克MSO5B系列示波器從兩個SMU輸出的柵極電壓(黃色)和漏極電壓(藍色)的屏幕截圖。

圖7.sic-mosfet-vth-vgsweep-vd?xed-smu測試的示波器捕獲圖

所有測量值以及導出的閾值電壓都顯示在分析視圖的圖表中。工作表的第一個單元格還顯示執(zhí)行后的錯誤代碼。這兩項測試的所有錯誤代碼都可以在附錄C中找到。

此測試是使用wbg_ulib用戶庫中的SMU_vgsweepvd?xed用戶模塊創(chuàng)建的。

掃描漏極和柵極電壓法

第二個測試是sic-mosfet-vth-vgvdsweep-smu,使用SMU1向柵極 (Vg) 施加調(diào)理脈沖,然后兩個SMU向漏極(SMU2) 和柵極 (SMU1) 端輸出相同幅度 (Vg=Vd) 的向下電壓掃描。該測試的柵極電壓 (Vg)、漏極電壓 (Vd) 和漏極電流 (Id) 時序圖如圖8所示。與之前的測試一樣,閾值電壓 (Vth) 是使用目標漏極電流的線性插值計算的。

圖8.sic-mosfet-vth-vgvdsweep-smu測試的柵極電壓 (Vg)、漏極電壓 (Vd) 和漏極電流 (Id) 時序圖

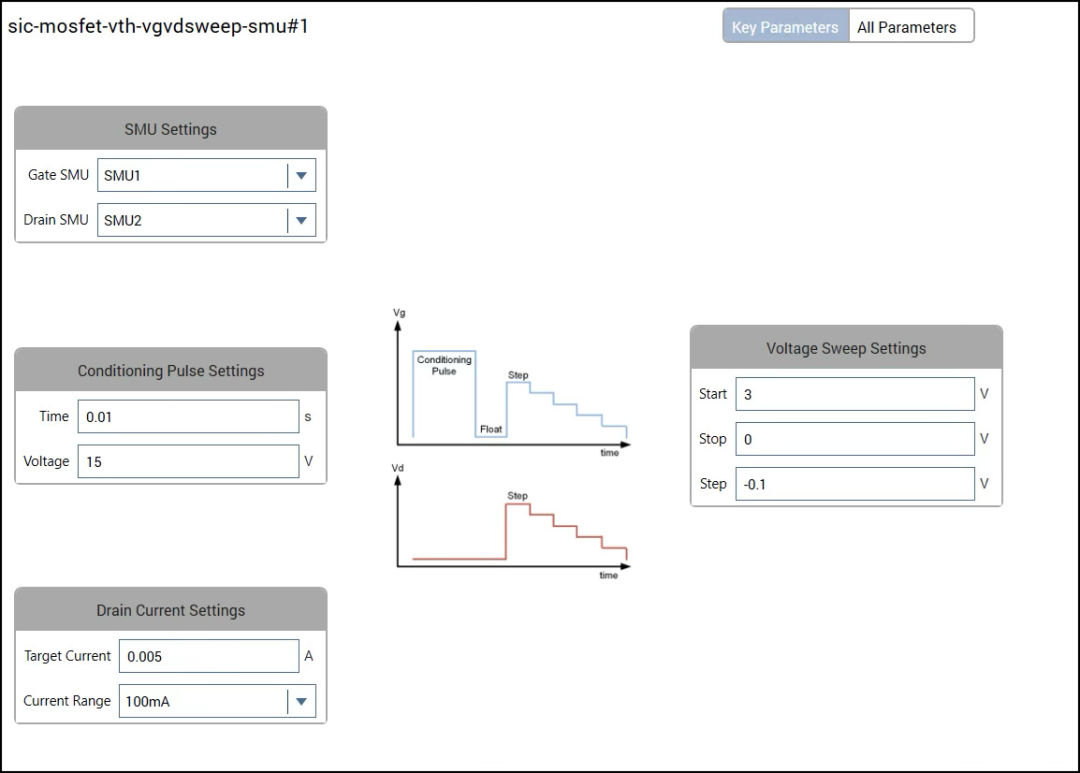

該測試的輸入?yún)?shù)在“配置”視圖中設置,如圖9所示,與第一次測試中的輸入?yún)?shù)類似,但沒有漏極電壓偏置設置。輸入和輸出參數(shù)及其描述列在附錄B中。

圖9.sic-mosfet-vth-vgvdsweep-smu測試的配置界面

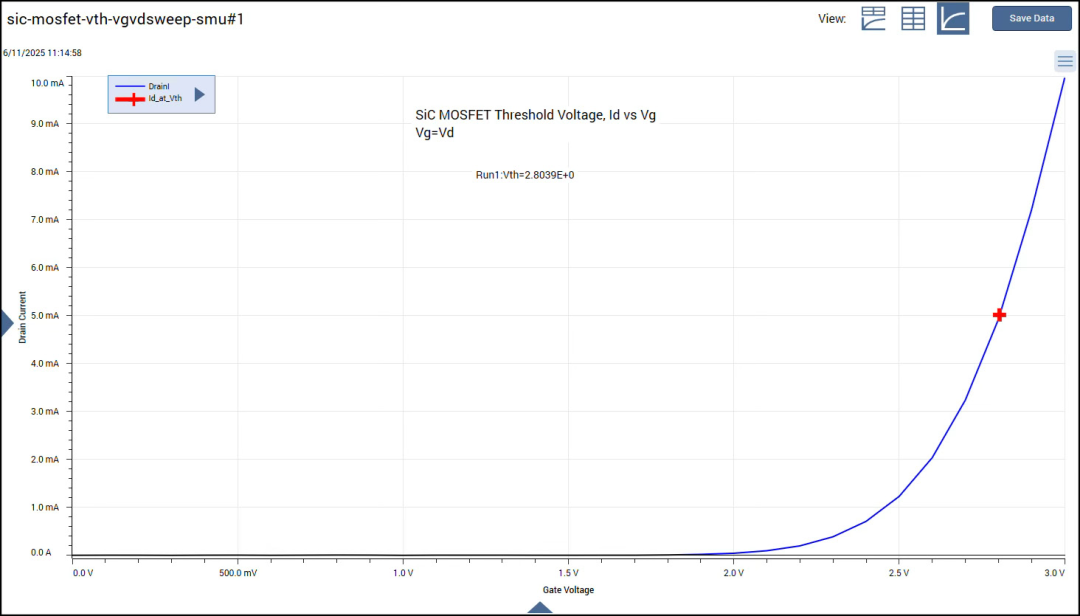

執(zhí)行此測試的結(jié)果如圖10所示。與第一個測試一樣,外推的閾值電壓在傳輸曲線上顯示為紅叉。

圖10.sic-mosfet-vth-vgvdsweep-smu測試的Id-Vg圖中顯示Vth

示波器柵極和漏極電壓的波形捕獲如圖11所示。請注意柵極和漏極電壓掃描重疊,因為兩個掃描同時輸出。

圖11.sic-mosfet-vth-vgvdsweep-smu測試的示波器捕獲圖

此測試是使用wbg_ulib用戶庫中SMU_vgvdsweep用戶模塊創(chuàng)建的。

結(jié)論

4200A-SCS參數(shù)分析儀與Clarius+軟件套件和兩個SMU配合使用,使用基于JEDEC JEP183A標準的測試方法,可以對SiC MOSFET進行精確的閾值電壓測量。這些方法通過施加調(diào)節(jié)脈沖來釋放陷阱來減輕滯后效應。憑借其內(nèi)置的測試和項目庫,Clarius軟件使4200A-SCS成為SiC器件表征的強大工具。Clarius V1.14版本中添加了另一項SiC MOSFET測試,可在SiC器件上進行準靜態(tài)C-V測量。

-

MOSFET

+關注

關注

150文章

9280瀏覽量

228812 -

半導體

+關注

關注

336文章

29866瀏覽量

256832 -

SiC

+關注

關注

32文章

3444瀏覽量

67888 -

閾值電壓

+關注

關注

0文章

98瀏覽量

52353

原文標題:基于JEDEC JEP183A標準的SiC MOSFET閾值電壓精確測量方法(含直播回放)

文章出處:【微信號:泰克科技,微信公眾號:泰克科技】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

MOSFET的重要特性–柵極閾值電壓

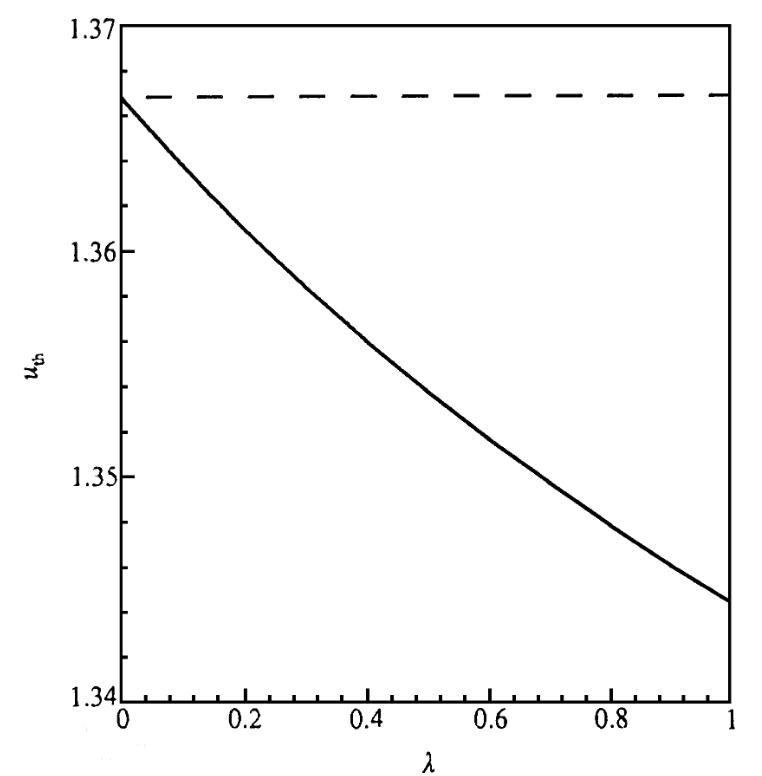

閾值電壓的計算

MOS管閾值電壓與溝長和溝寬的關系

EDA探索之控制閾值電壓

控制閾值電壓

影響MOSFET閾值電壓的因素

什么是MOS管亞閾值電壓?MOSFET中的閾值電壓是如何產(chǎn)生的?

淺談影響MOSFET閾值電壓的因素

MOSFET閾值電壓是什么?影響MOSFET閾值電壓的因素有哪些?

基于JEDEC JEP183A標準的SiC MOSFET閾值電壓精確測量方法

基于JEDEC JEP183A標準的SiC MOSFET閾值電壓精確測量方法

評論