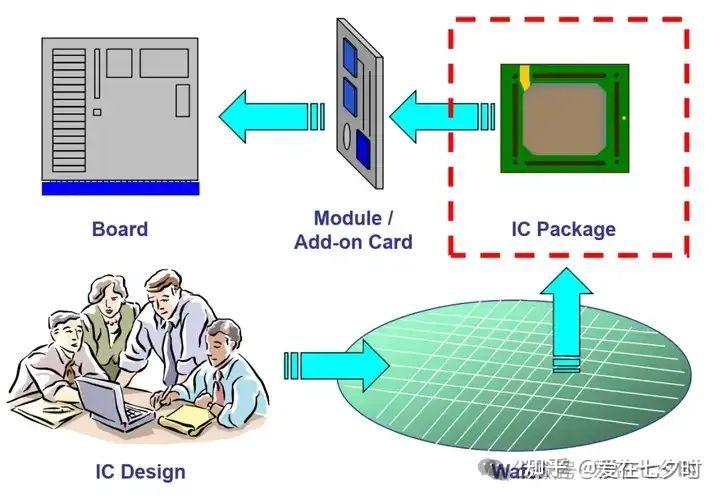

【博主簡介】本人系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵,如有需要可留意文末聯系方式,當前在網絡平臺上均以“愛在七夕時”的昵稱為ID跟大家一起交流學習!

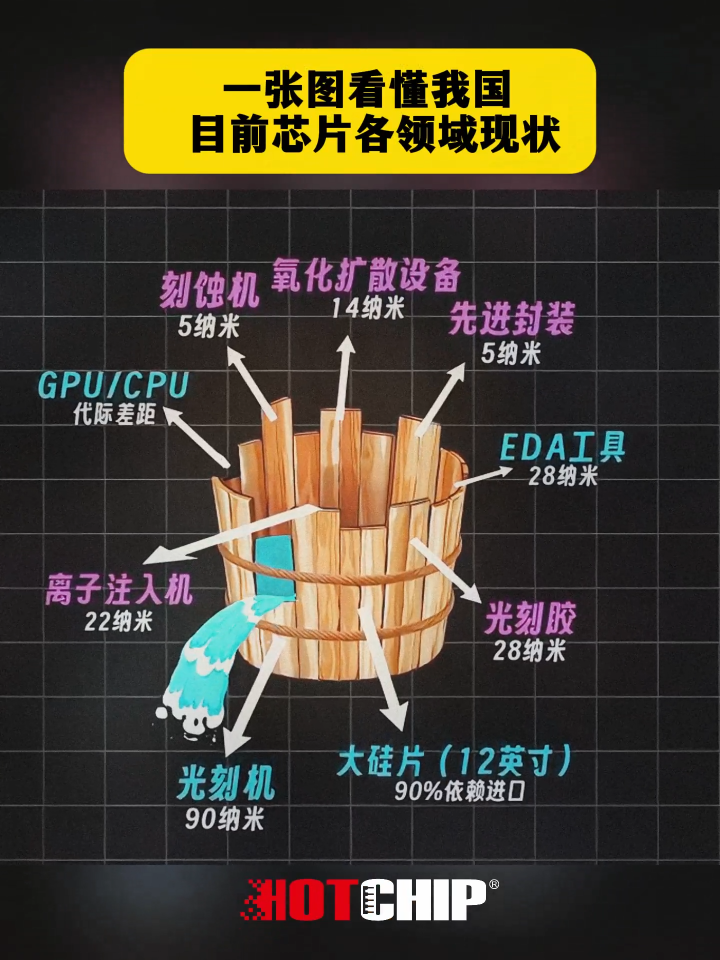

相信在半導體封裝工序工作的朋友,肯定對“芯片裂紋”(也有的叫芯片開裂或是裸片裂紋)這種非常典型的失效模式并不陌生。隨著集成電路(IC)技術的發展,芯片尺寸不斷縮小,厚度持續降低。這在提升單位晶圓產出、降低封裝高度的同時,也帶來了新的挑戰。硅片的易碎特性使其在組裝和測試過程中,即便受到中等強度的應力,也可能發生開裂。

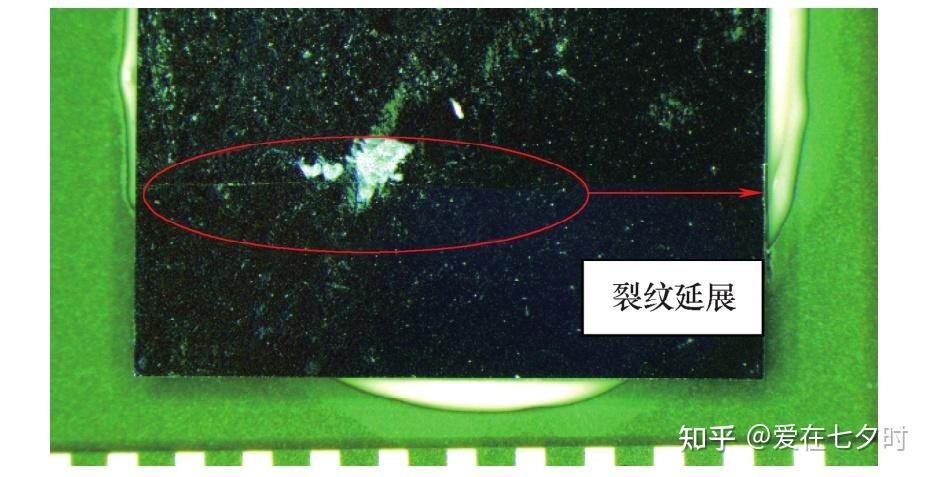

而且更讓人疑惑的是:DB、WB和Molding乃至后面的Final Test都沒啥問題,Test Yield也可能會達標。但是,一經過可靠性的高低溫循環測試,突然就可能有比較大量的芯片失效,拆開塑封料一看,硅片上全是從邊緣延伸的裂紋。這種 “電測看不破,循環現原形” 的缺陷,堪稱封裝環節的 “隱形殺手”,也是一種導致災難性的產品失效,每年能給行業造成的損失超十幾億,甚至更多。

所以,本章節想要跟大家分享的就是芯片封裝中典型失效之一的“芯片裂紋”模式。會從硅芯片的 “先天脆弱性” 入手,拆解裂紋產生的工藝誘因、檢測難點,再給出行之有效的工藝改進方案等等。

一、芯片裂紋的定義

芯片裂紋,英文常常稱作:Die Crack,中文定義也可稱作:裸片裂紋或是芯片開裂。它是指在半導體集成電路封裝過程中或使用過程中,芯片表面或內部產生的開裂(裂紋)的一種現象。

二、芯片裂紋(Die Crack)的分類

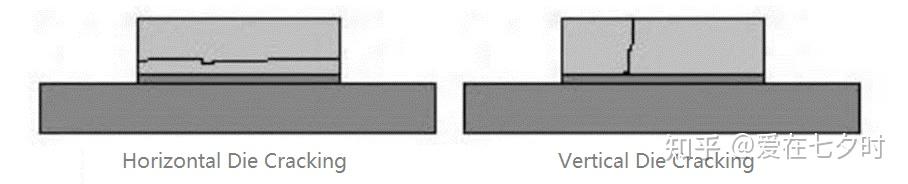

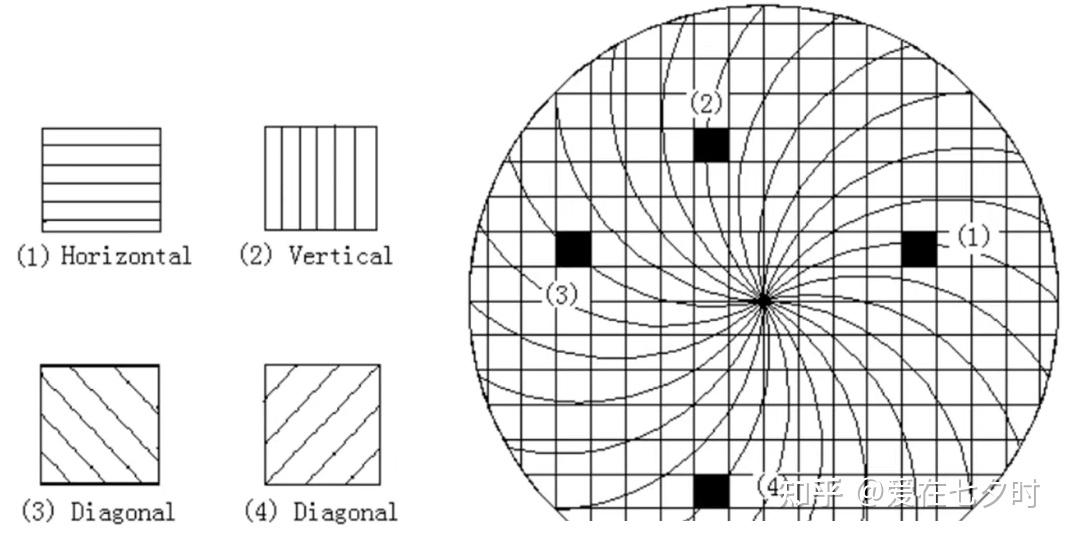

當前按開裂(裂紋)方向去定義的話,主要分為以下兩大類:

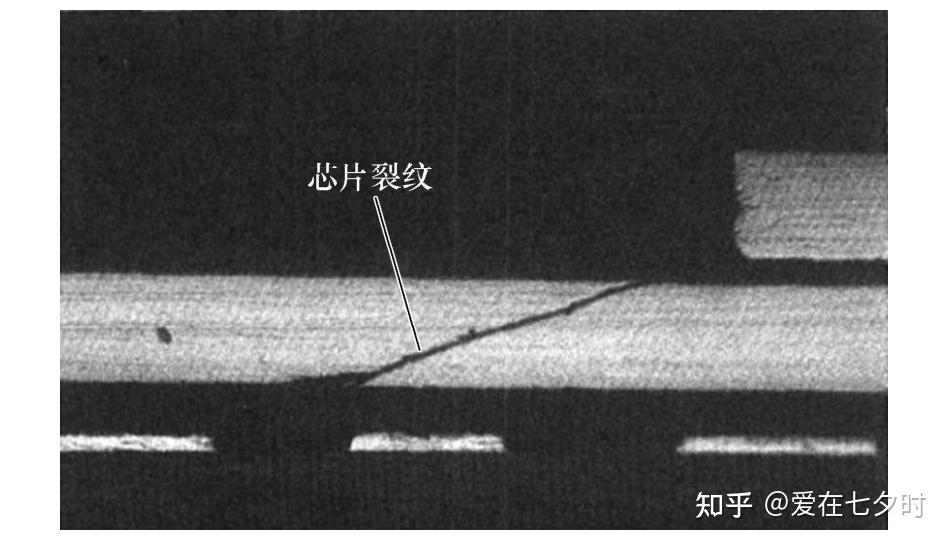

1、垂直方向裂紋

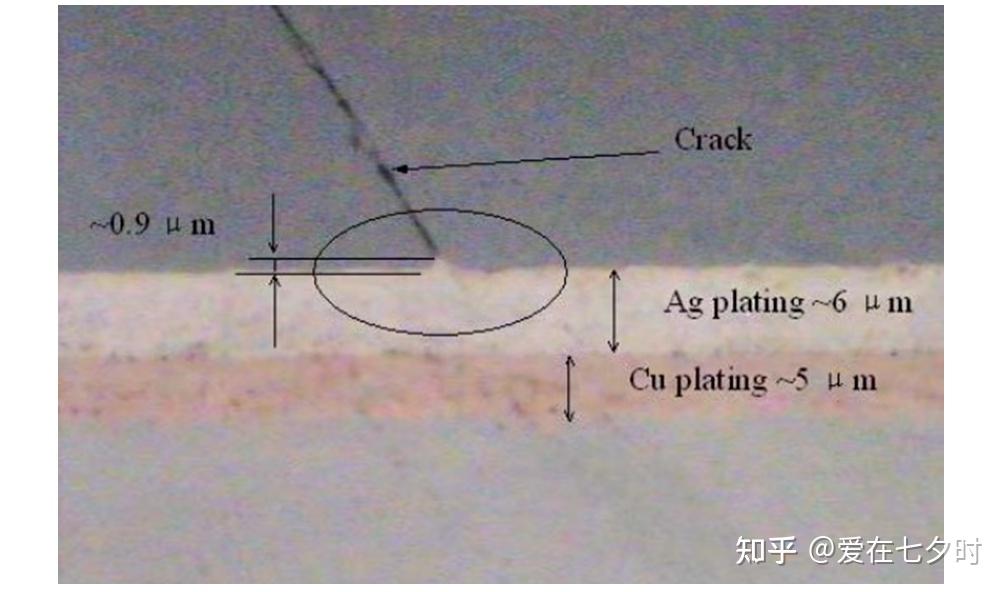

起源于芯片背面,通常由芯片彎曲,導致其背面受到拉伸應力而產生。裂紋從背面缺陷處(如研磨劃痕)開始,并向芯片表面擴展。這種模式需要較大的應力才能觸發。

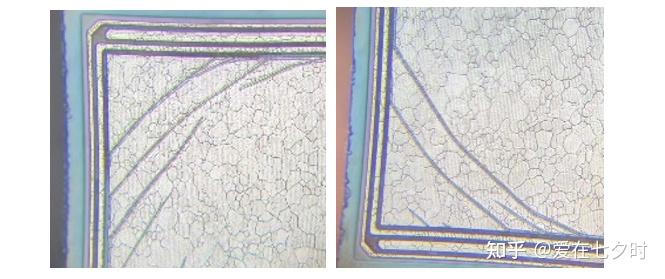

2、水平/邊緣裂紋

多由晶圓切片過程中形成的邊緣缺陷引發,裂紋從邊緣向芯片內部擴展,常見于倒裝芯片(PBA)封裝中,也是較為常見的模式。

三、芯片裂紋(Die Crack)產生的原因

芯片裂紋(Die Crack)的根源,首先在于硅本身的 “材質特性”—— 咱們常說單晶硅是 “硬而脆” 的典型,這可不是隨口說的,而是由它的晶體結構和力學性能決定的。

1、芯片裂紋(Die Crack)的失效機理

從晶體結構來看,單晶硅是金剛石型面心立方結構,原子間通過強共價鍵結合,這種結構讓它硬度極高(莫氏硬度 7,僅次于藍寶石),但也導致它 “缺乏塑性”—— 一旦受到外力或應力,原子沒辦法通過滑移來緩解,只能在應力集中處形成裂紋,而且裂紋會沿著原子結合力較弱的 “解理面”(比如 {111} 晶面)快速擴展,最后導致脆斷。就像玻璃一樣,哪怕只是表面有個微小劃痕,稍微受力就會碎。

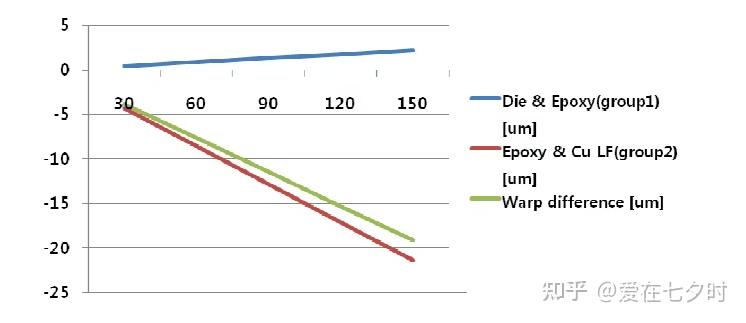

從力學性能來看,硅的關鍵指標 “斷裂韌性(KIC)” 極低,僅 0.7-1.0 MPa?m^1/2,而金屬銅的斷裂韌性是它的 50 倍以上。這意味著,硅芯片只要表面存在微米級的微裂紋(比如減薄后留下的 1μm 劃痕),在很小的應力(比如 100MPa)作用下,裂紋就會瞬間擴展。更麻煩的是,硅的熱膨脹系數(CTE)僅 3.5×10^-6/℃,和封裝里的環氧塑封料(12-18×10^-6/℃)、引線框架銅(17×10^-6/℃)差異巨大,溫度變化時產生的熱應力,會成為裂紋擴展的 “助推器”。

簡單來說,因為IC 裸芯片的制造原料通常均為單晶硅,因為特殊特性,在遭受外力作用或表面存在瑕疵時,極容易出現破裂情況。在晶圓減薄、晶圓切割、芯片貼裝和引線鍵合等一系列需要施加應力的工藝操作過程中,芯片開裂的風險大幅增加,這一問題已成為致使 IC 封裝失效的重要因素之一。

若芯片裂紋(Die Crack)未蔓延至引線區域,通過常規手段很難發現;更有部分存在裂紋的芯片,在常規工藝檢查與電學性能檢測時,其性能表現與正常芯片并無明顯差異,使得裂紋問題極易被忽略。然而,這些隱藏的裂紋會對封裝后器件的穩定性與使用壽命造成嚴重威脅。由于常規電學性能測試無法有效識別芯片裂紋(Die Crack),因此需要借助高低溫熱循環實驗進行檢測。在加熱和冷卻交替過程中,材料間產生的熱應力會促使裂紋逐步擴展,直至芯片徹底破裂,最終在電學性能上呈現出異常狀態。

鑒于外部應力是引發芯片裂紋(Die Crack)的主因,一旦檢測到芯片存在裂紋,就必須立即對芯片封裝的工藝流程和參數進行優化,最大程度減少工藝環節對芯片產生的應力影響。例如,在晶圓減薄工序中,采用更為精細的加工方式,提高芯片表面的平整度,以此消除潛在應力;晶圓切割時,運用激光切割技術替代傳統方法,降低切割過程對芯片表面造成的應力損傷;在引線鍵合環節,精準調控鍵合溫度和壓力參數,確保鍵合過程平穩安全。

因此,硅芯片表面不能有瑕疵,也經不起劇烈的溫度變化 —— 這是它容易開裂的先天因素,也是我們后續工藝控制的核心依據。

2、芯片裂紋(Die Crack)的影響

芯片裂紋(Die Crack)的失效模式多種多樣,所以,失效的影響也各有不同,主要包括:

a.電性能失效

當裂紋穿過結區時,可能導致短路或者漏電,這是最常見的失效表現。例如在表面貼裝MOSFET產品中,經過SMT工藝后發現的D、S間漏電和短路現象,超過50%的失效比例都是由芯片內部裂紋引起的。

b.電路中斷失效

裂紋也可能全部或者部分截斷電路,造成器件功能完全喪失。

c.潛在性失效

最為致命的是,裂紋引起的這些效應只有當有熱或者電流通過時才會顯現,而標準的電性能測試則根本無法檢測到這些失效。 從統計數據來看,芯片碎裂在早期失效中約占1%的比例,而對于使用薄/超薄芯片的器件(如IC卡),芯片碎裂則占其失效總數的一半以上。裂紋形狀多為"十"字、"T"字型,亦有一部分為橫貫芯片的單條裂紋,約50%以上的碎裂芯片,其裂紋位于芯片中央附近并垂直于邊緣;其余芯片的裂紋則靠近芯片邊緣或集中于芯片一角。

四、芯片裂紋(Die Crack)的來源

芯片裂紋(Die Crack)不是單一環節導致的,而是從晶圓減薄到引線鍵合,每個需要施加應力的環節,都可能埋下 “裂紋種子”。所以,芯片裂紋(Die Crack)的產生是多種因素共同作用的結果,可以歸納為內在因素和外在因素兩大類。內在因素主要指芯片自身的強度特性,而外在因素則包括制造工藝和環境應力等方面的影響。

1、工藝過程中的應力源

a.晶圓減薄(Wafer Thinning)

為了適配薄型封裝(比如手機芯片的 0.8mm 封裝),晶圓需要從原始的 775μm 減薄到 50-100μm,這個過程中最容易產生微裂紋。傳統的 “機械研磨”(用金剛石砂輪打磨),會在硅片表面留下深度 1-5μm 的 “機械損傷層”—— 這里面全是微小的劃痕和晶格畸變,就像給芯片表面劃了無數道 “隱形傷口”。

有測試數據顯示,用 800 目砂輪機械減薄的晶圓,表面微裂紋密度能達到 100 個 /cm2,而后續工藝只要施加輕微應力(比如切割時的 20MPa 壓力),這些微裂紋就會擴展成肉眼可見的大裂紋。更隱蔽的是,有些微裂紋在硅片內部(亞表面裂紋),減薄后根本看不出來,要到后續熱循環時才會爆發。

b.晶圓切割(Wafer Dicing)

晶圓切割是把整片晶圓切成單個芯片,這個環節的應力最直接。目前主流的切割方式有兩種,都有開裂風險。

c.機械刀片切割(mechanical blade cutting)

高速旋轉的金剛石刀片(轉速 30000rpm)在切割時,會對芯片邊緣產生 “擠壓應力” 和 “摩擦熱應力”。如果刀片磨損(刃口變鈍),或者切割壓力過大(超過 50N),很容易在芯片邊緣形成 “崩邊”(邊緣缺角),進而引發裂紋;

d.激光切割(Laser cutting)

雖然沒有機械接觸,但高功率激光(比如 UV 激光)會在硅片表面產生局部高溫(瞬間達 1000℃以上),冷卻后形成 “熱應力梯度”—— 表面收縮、內部膨脹,導致微裂紋產生。尤其是激光能量控制不當(比如能量過高),會在切割路徑兩側留下深度 2-3μm 的熱損傷層。

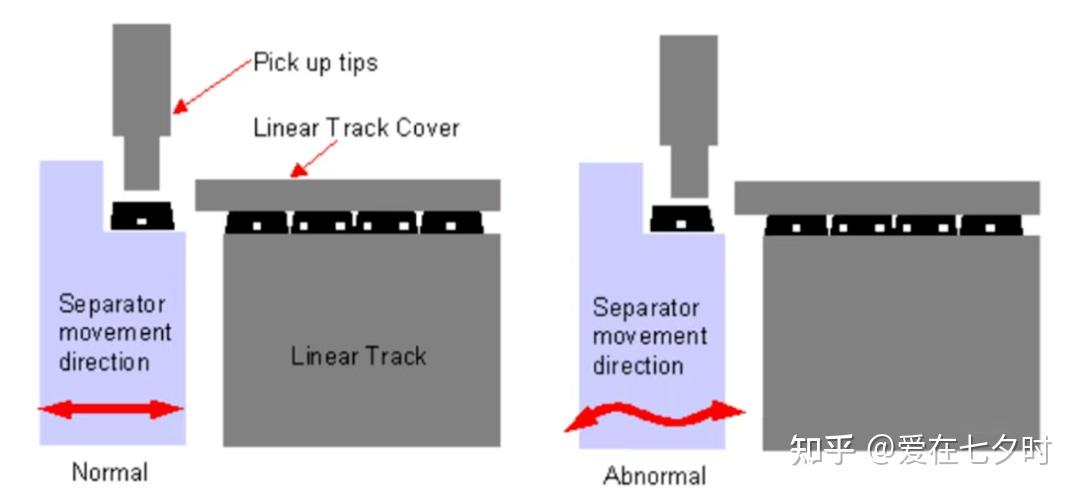

e.芯片粘貼(Die Bonding)

芯片粘貼是把芯片粘在引線框架或基板上,這個環節的應力來自 “導電膠 / 絕緣膠的固化收縮”。比如環氧導電膠,在 150℃固化時會有 2-3% 的體積收縮,這種收縮會對芯片產生 “拉扯應力”—— 如果膠層不均勻(比如局部膠厚差超過 10μm),應力會集中在膠層薄的區域,導致芯片邊緣開裂。

更危險的是 “空心粘貼”,膠層里有氣泡(直徑>50μm),固化時氣泡受熱膨脹,冷卻后收縮,會在氣泡上方的芯片區域產生局部應力集中,形成 “隱形微裂紋”,這種裂紋在電測時完全看不出來,只有熱循環時才會擴展。

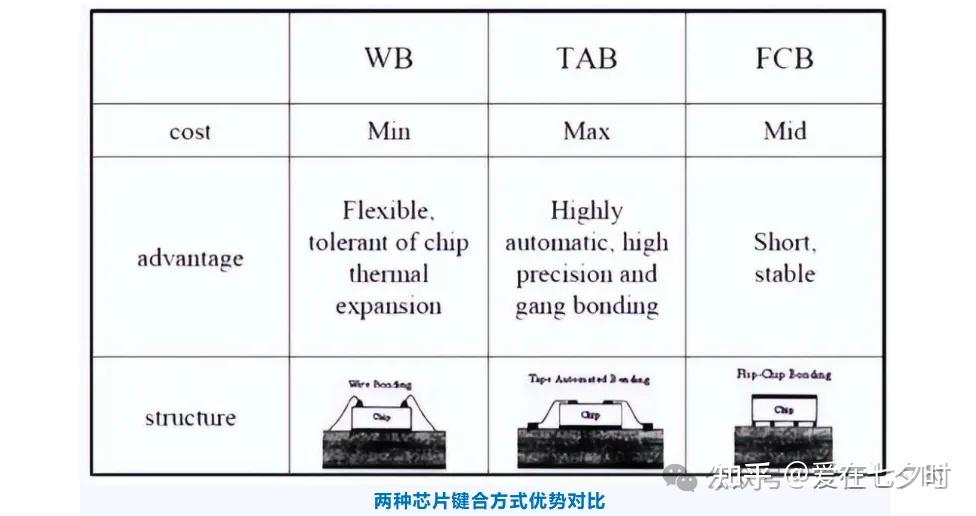

f.引線鍵合(Wire Bonding)

引線鍵合(比如金絲鍵合)需要在芯片焊墊上施加壓力(10-50gf)和超聲波能量,同時加熱(150-250℃)。這個過程中,三個因素會導致開裂。

(1)鍵合壓力過大

比如把 25gf 的壓力調成 40gf,超過了薄芯片(50μm)的承載極限,會在焊墊下方形成 “壓痕裂紋”;

(2)溫度不均勻

鍵合臺局部溫度過高(比如溫差超過 10℃),芯片上下表面形成熱應力梯度,導致翹曲開裂;

(3)焊墊邊緣應力集中

如果鍵合點靠近芯片邊緣(距離<50μm),壓力會傳遞到芯片邊緣,引發邊緣裂紋。

2、材料與設計因素

芯片強度是研究芯片碎裂的最重要參數。芯片強度各不相同,只有強度最低的才最容易碎裂失效。強度分布范圍很廣,那些最"脆弱"的芯片碎裂時的強度只相當于芯片平均強度的幾分之一。因此只需設法將最"脆弱"芯片的強度提高或者予以剔除,就能從根本上提高芯片整體強度。 材料缺陷也是導致芯片裂紋(Die Crack)的重要原因,包括:

a.晶格缺陷

在晶體生長過程中產生的不完美結構;

b.雜質污染

制造過程中引入的雜質原子;

c.表面劃痕

工藝處理過程中造成的機械損傷 設計方面的因素也不容忽視,如果半導體芯片的設計出現問題,比如結構過于復雜、焊點設計不合理等,都可能導致芯片更容易發生裂紋。

3、環境應力因素

外界環境因素會加劇芯片裂紋的產生和擴展:

a.溫度變化

劇烈的溫度變化會導致材料熱脹冷縮,產生熱應力。

b.機械振動

運輸或使用過程中的振動可能引發裂紋擴展。

c.濕度影響

封裝樹脂耐濕性差會導致產品吸濕,當封裝體在環境溫度劇變時,內部水分急劇汽化,當蒸汽壓力大于封裝樹脂與芯片、載片以及框架表面之間的粘接力時,就會使它們的界面之間出現剝離現象,嚴重時還會導致封裝樹脂或芯片出現裂紋。

五、芯片裂紋(Die Crack)分析檢測難點

在做芯片裂紋(Die Crack)失效分析時最讓人頭疼的就是芯片裂紋(Die Crack)在電性能測試(ICT、FT 測試)中根本查不出來 —— 只要微裂紋沒延伸到焊墊或引線區域,不影響電流通路,電測就會判定為 “合格”。但這些 “看似合格” 的芯片,在客戶端使用時,一旦經歷溫度變化,就會瞬間失效。

這背后的核心原因是熱應力導致裂紋擴展。在高低溫循環測試(比如 - 40℃~125℃,100 次循環)中,封裝里的不同材料因 CTE 差異,會產生周期性的膨脹和收縮:塑封料膨脹時會擠壓芯片,收縮時會拉扯芯片;引線框架的形變也會傳遞應力到芯片上。這些反復的熱應力,會讓原本的微裂紋以 “每天 1-2μm” 的速度擴展,直到裂紋貫穿芯片,切斷電流通路,電性能才會失效。

六、解決芯片裂紋(Die Crack)不良的方法

通過上面第四大點分析出的芯片裂紋(Die Crack)的來源,我們可以有針對性地調整工藝,把芯片裂紋(Die Crack)率壓到最低。結合之前在“安世半導體”做失效分析時的一些實踐,分享幾個經過驗證的有效方案給大家參考:

1、晶圓減薄(Wafer Thinning)

把傳統的 “純機械研磨” 改成 “機械研磨 + 化學機械拋光(CMP)”:先用粗砂輪把晶圓減薄到目標厚度 + 20μm,再用 CMP(研磨液含二氧化硅顆粒和化學試劑)去除表面 20μm 的損傷層。這樣處理后,硅片表面粗糙度能從機械研磨的 50nm 降到 1nm 以下,微裂紋密度直接從 100 個 /cm2 降到 0.1 個 /cm2 以下。某大廠的實踐顯示,改用 CMP 后,后續切割環節的開裂率從 8% 降到了 0.5%。

2、晶圓切割(Wafer Dicing)

對薄晶圓(<100μm),優先用 “激光半切 + 機械分離” 工藝:用 UV 激光在晶圓表面切出深度為晶圓厚度 1/2 的槽(比如 50μm 厚晶圓切 25μm 深),然后用機械推桿輕輕分離芯片。這種方式既沒有機械刀片的擠壓,也沒有激光全切的熱損傷,芯片邊緣崩邊率能控制在 0.1% 以內。如果必須用機械切割,要定期更換金剛石刀片(每切割 50 片晶圓換一次),并把切割壓力控制在 30N 以下。

3、芯片粘貼(Die Bonding)

選擇 “低模量環氧膠”(模量<5GPa,傳統膠模量 10-15GPa),模量越低,固化收縮時產生的拉扯應力越小;同時,粘貼前對膠層進行真空脫泡(真空度 - 95kPa,保持 10 分鐘),確保膠層氣泡率<1%。某封裝廠用這種方案后,粘貼環節的開裂率從 3% 降到了 0.2%。

4、引線鍵合(Wire Bonding)

鍵合前要校準鍵合壓力(用壓力傳感器校準,誤差<±1gf),并根據芯片厚度調整壓力(50μm 厚芯片用 15-20gf,100μm 厚芯片用 25-30gf);同時,定期校準鍵合臺溫度(溫差控制在 ±2℃),避免局部過熱。另外,把鍵合點距離芯片邊緣的距離控制在≥100μm,避開邊緣應力集中區。

七、芯片裂紋(Die Crack)失效分析流程

因為芯片裂紋(Die Crack)不良問題是一個比較典型的失效模式,所以我們在分析過程中是需要系統而全面的,確保每一個細節都不被忽視,以下分析流程用一個實例給大家展示:

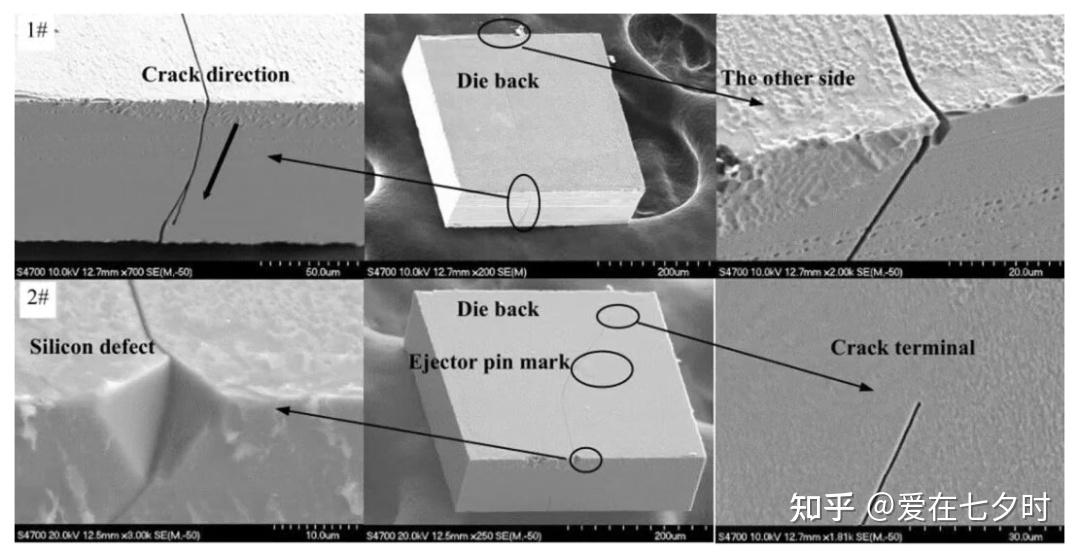

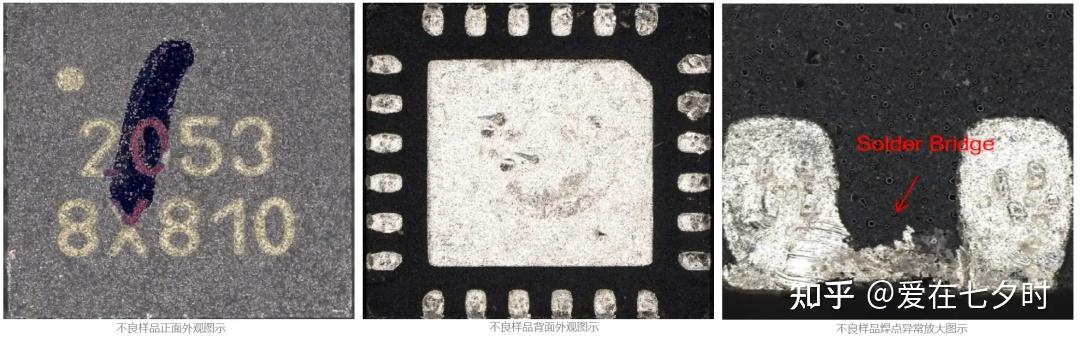

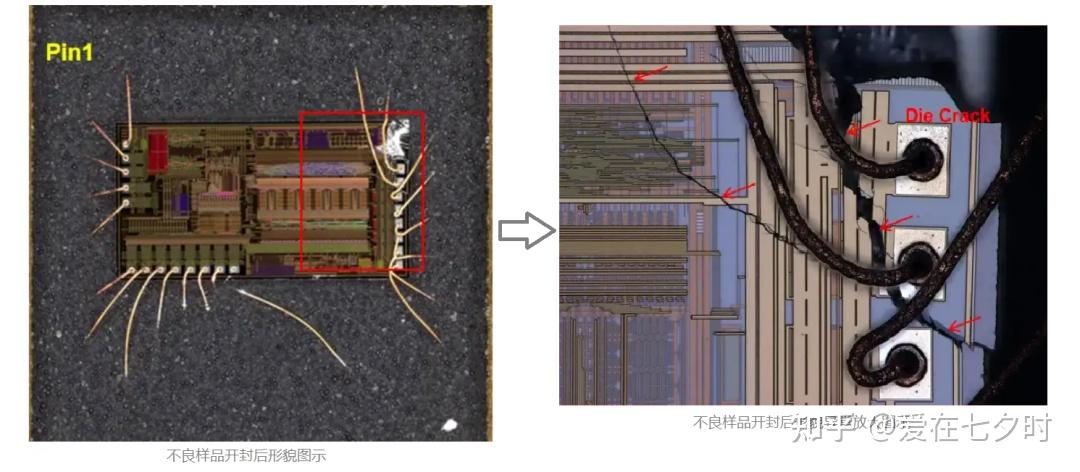

1、外觀檢查

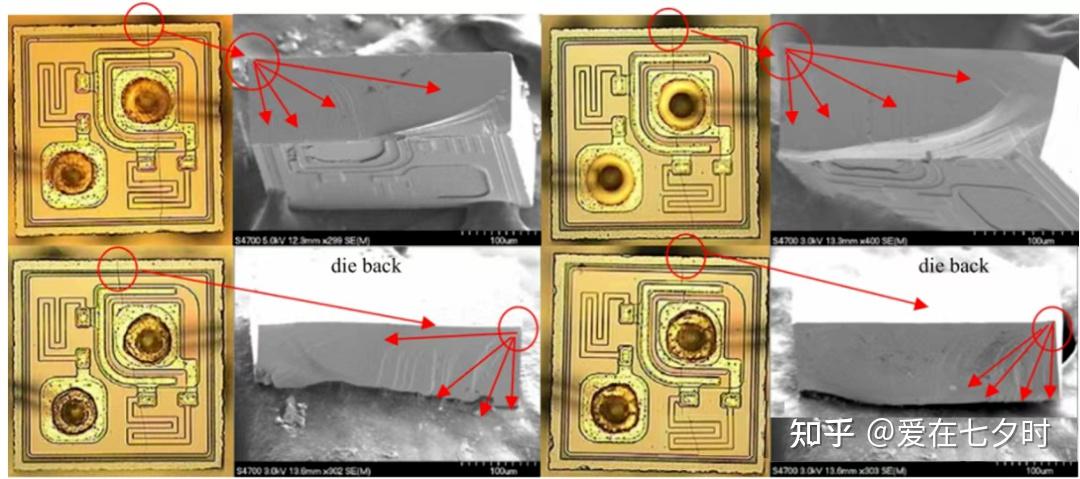

利用高倍顯微鏡對樣品的正反面進行了細致的外觀檢查,發現背面焊點存在異常,而其他表面未見異常。這一發現就會給出一個提示信號,問題可能出在焊接過程中或材料本身的缺陷。

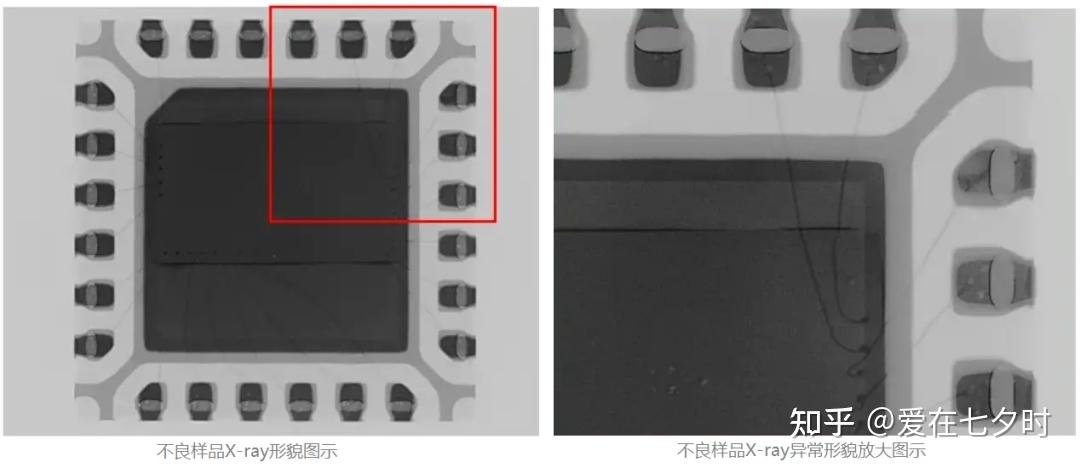

2、X-Ray分析

剛開始先做一些無損分析,初步確認問題點。通過X-ray檢查,可以發現樣品頂部金線有異常凹陷,這是導致焊點異常的直接原因。X-Ray分析能夠穿透材料表面,揭示內部結構的異常,這對于確定失效模式至關重要。

3、電性能測試

不良樣品的電性能測試結果顯示Pin8與Pin9之間存在短路,通過這一步就可證實在第一步做”外觀檢查“時的初步判斷:短路可能是由于焊接不良或材料缺陷導致的電連接異常。

4、開封檢查

從這一步開始,就是做的有損分析了。不良樣品開封后,進一步發現芯片本身存在開裂現象,這是導致測試異常的根本原因。開封檢查是失效分析中的關鍵步驟,它允許我們直接觀察到芯片內部的物理損傷。

5、微觀分析

利用掃描電子顯微鏡(SEM)對開裂區域進行了微觀分析,觀察到裂紋的形態和分布,以及可能的裂紋起源點。SEM分析能夠提供高分辨率的圖像,幫助我們理解裂紋的形成機制。

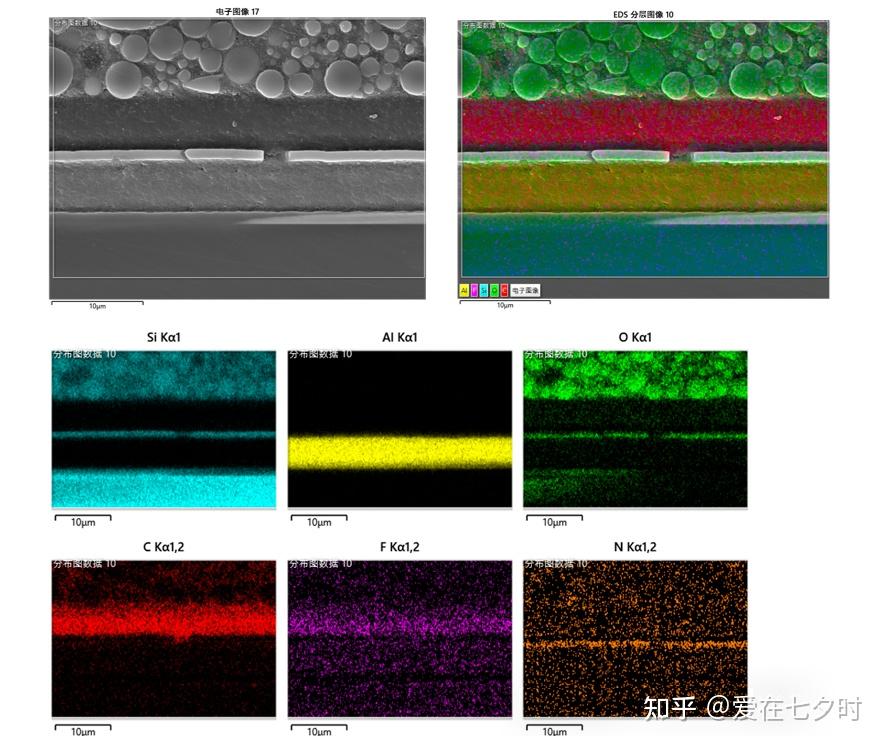

6、材料分析

對芯片材料進行了化學成分分析,以確定是否存在材料不純或成分不均勻的問題。這些因素都可能導致材料的脆性增加,從而引發開裂。

7、熱力學分析

通過熱力學分析,我們評估了芯片在不同溫度下的膨脹和收縮行為,以及這些熱力學特性如何影響芯片的機械穩定性。

8、力學性能測試

對芯片進行了力學性能測試,包括拉伸、壓縮和彎曲測試,以評估其抗裂性能。這些測試有助于我們了解芯片在實際使用條件下的力學響應。

9、環境應力篩選(ESS)

通過環境應力篩選,我們模擬了芯片在實際使用中可能遇到的各種環境條件,以評估其在極端條件下的可靠性。

通過這一單芯片裂紋(Die Crack)失效分析,可總結出:芯片開裂是導致測試異常的根本原因。這一發現不僅為客戶解決了眼前的問題,也為其后續的產品改進提供了方向。

八、芯片裂紋(Die Crack)失效的建議

為了有效的避免此類失效會流入市場,導致在客戶端發生客訴問題,我們應該從以下四個方面著手進行干預,以避免或是減少芯片裂紋(Die Crack)失效的不良案例,從而提升產品品質:

1、加強原材料質量控制

從源頭上確保芯片材料的均勻性和可靠性,減少因材料缺陷導致的芯片裂紋(Die Crack)風險。

2、優化封裝工藝

調整封裝過程中的溫度、壓力等參數,減少熱應力和機械應力對芯片的影響。

3、增強設計強度

在芯片設計階段考慮更多的應力因素,增強芯片結構的抗裂性能。

4、定期進行可靠性測試

通過定期的可靠性測試,及時發現潛在的失效風險,減少產品在市場中的失效率。

九、寫在最后面的話

因為“芯片裂紋(Die Crack)”失效模式它是與單晶硅的脆性本質直接相關,其失效可能隱匿于晶圓減薄、切割、貼裝及鍵合等應力工藝環節。由于裂紋初期可能不顯著影響電學性能,需通過高低溫熱循環實驗加速裂紋擴展——不同材料熱膨脹系數差異產生的熱應力,會促使微裂紋擴展至可見程度,最終影響器件可靠性。當前行業正探索激光切割、化學機械拋光(CMP)等低應力工藝,以及通過離子注入增強硅片機械強度的新技術,以減少工藝損傷。

所以,半導體封裝中芯片裂紋(Die Crack)的不良是一個復雜的多物理場耦合問題,根源在于機械應力和熱應力。解決這一問題需要一個系統性的工程方法,貫穿于產品設計、材料選型、工藝制程和可靠性驗證的全過程。通過綜合運用先進的分析工具(如SAM)和科學的實驗設計,可以有效地定位根本原因并實施改進,最終提升產品的良率和長期可靠性。

免責聲明

我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時聯系(一三七 二八三五 六二六五),我們將第一時間跟蹤核實并作處理,謝謝!

審核編輯 黃宇

-

半導體

+關注

關注

339文章

31115瀏覽量

265991 -

封裝

+關注

關注

128文章

9309瀏覽量

148975

發布評論請先 登錄

芯片越先進,越離不開失效分析:半導體失效分析是做什么的?

85頁PPT,看懂芯片半導體的封裝工藝!

半導體芯片封裝中引線框架的概念和工藝

芯片失效故障定位技術中的EMMI和OBIRCH是什么?

一文了解什么是功率半導體器件產品的失效

半導體芯片制造技術——“芯片鍵合”工藝技術的詳解;

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

半導體后道制程“芯片鍵合(Die Bonding)”工藝技術的詳解;

DAF膠膜(Die Attach Film)詳解

半導體芯片封裝典型失效模式之“芯片裂紋(Die Crack)”的詳解;

半導體芯片封裝典型失效模式之“芯片裂紋(Die Crack)”的詳解;

評論