CDCE706是當今最小、功能最強大的PLL合成器/乘法器/分頻器之一。盡管它的物理輪廓很小,但CDCE706非常靈活。它能夠從給定的輸入頻率產生幾乎獨立的輸出頻率。

輸入頻率可以來自LVCMOS、差分輸入時鐘或單晶。可以通過SMBus數據接口控制器選擇合適的輸入波形。

為了實現獨立的輸出頻率,每個PLL的基準分壓器M和反饋分壓器N可以設置為M分頻器的1至511,N分頻器的值為1至4095。PLL-VCO(壓控振蕩器)頻率被路由到自由可編程輸出開關矩陣,到六個輸出中的任何一個。開關矩陣包括一個額外的7位后分頻器(1至127)和每個輸出的反相邏輯。

*附件:cdce706.pdf

較深的M/N分頻比允許從任何基準輸入頻率(例如,27 MHz)生成零ppm時鐘。

該CDCE706包括三個 PLL,其中一個支持 SSC(擴頻時鐘)。PLL1、PLL2 和 PLL3 設計用于高達 300 MHz 的頻率,并針對具有寬分頻因子的零 ppm 應用進行了優化。

PLL2還支持中心擴頻和下擴頻時鐘(SSC)。這是減少電磁干擾的常用技術。此外,壓擺率可控 (SRC) 輸出邊沿可最大限度地降低 EMI 噪聲。

根據PLL頻率和分頻器設置,內部環路濾波器組件將自動調整,以實現PLL的高穩定性和優化的抖動傳輸特性。

該器件支持非易失性EEPROM編程,便于定制應用。它采用出廠默認配置進行預編程(見圖 13),可以在進入 PCB 之前重新編程為不同的應用配置,或通過系統內編程重新編程。通過串行 SMBus 接口對不同的設備設置進行編程。

兩個自由可編程輸入 S0 和 S1 可用于控制每個應用要求最苛刻的邏輯控制設置(輸出禁用至低電平、輸出 3 態、斷電、PLL 旁路等)。

CDCE706有三個電源引腳,V CC , VCCOUT1和 V CCOUT2 .VCC是設備的電源。它采用 3.3V 單電源電壓供電。VCCOUT1和 VCCOUT2是輸出的電源引腳。VCCOUT1為輸出 Y0、Y1 和 V 供電CCOUT2提供輸出 Y2、Y3、Y4 和 Y5。兩種輸出電源的電壓均為 2.3 V 至 3.6 V。在輸出電壓低于3.3 V時,輸出驅動電流受到限制。

該CDCE706的特點是在 -40°C 至 85°C 范圍內工作。

特性

- 基于高性能 3:6 PLL 的時鐘合成器/乘法器/分頻器

- 用戶可編程PLL頻率

- EEPROM編程,無需施加高編程電壓

- 通過SMBus數據接口輕松進行在線編程

- 寬 PLL 分壓比允許 0 ppm 輸出時鐘誤差

- 時鐘輸入接受晶體或單端LVCMOS或差分輸入信號

- 接受 8 MHz 至 54 MHz 的晶體頻率

- 接受高達 200 MHz 的 LVCMOS 或差分輸入頻率

- 兩個可編程控制輸入 [S0/S1、A0/A1],用于用戶定義的控制信號

- 六個LVCMOS輸出,輸出頻率高達300 MHz

- LVCMOS 輸出可針對互補信號進行編程

- 通過可編程輸出開關矩陣 [6x6] 自由選擇輸出頻率,包括每個輸出的 7 位后分頻器

- 集成 PLL 回路濾波器組件

- 低周期抖動(典型值 60 ps)

- 具有用于降低系統 EMI 的擴頻時鐘 (SSC) 功能

- 可編程輸出壓擺率控制 (SRC),用于降低系統 EMI

- 3.3V 器件電源

- 工業溫度范圍 -40°C 至 85°C

- 用于輕松進行 PLL 設計和編程的開發和編程套件 (TI Pro-Clock?)

- 采用 20 引腳 TSSOP 封裝

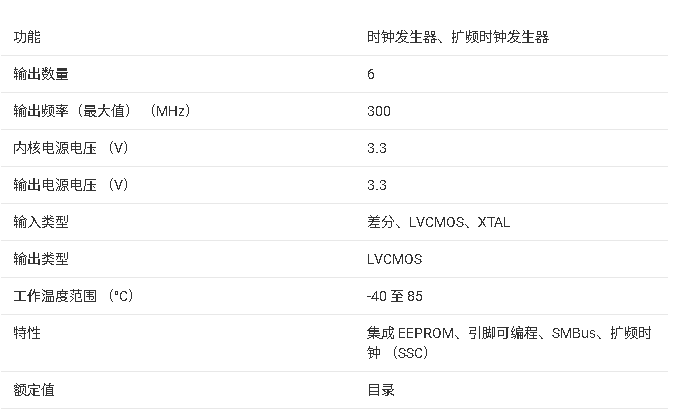

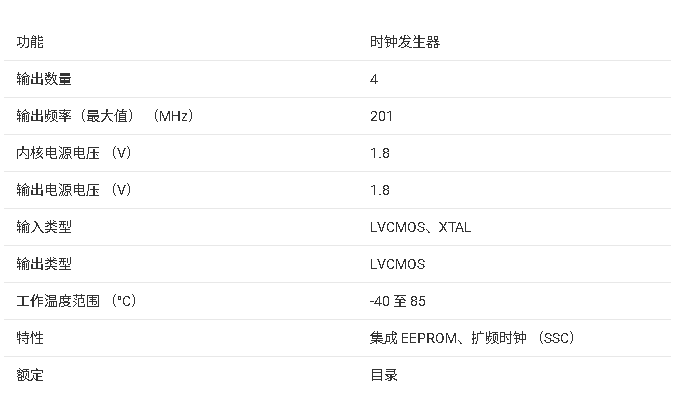

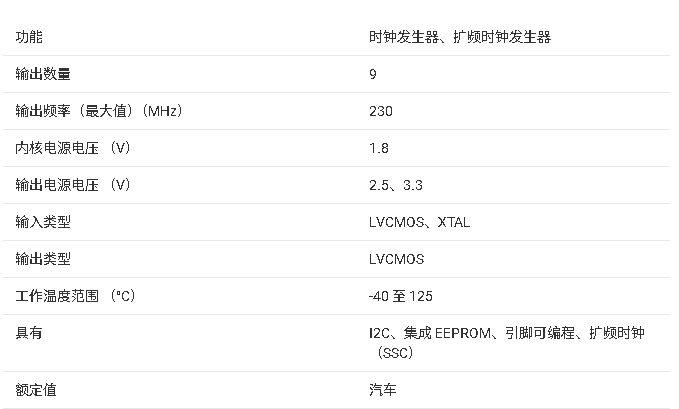

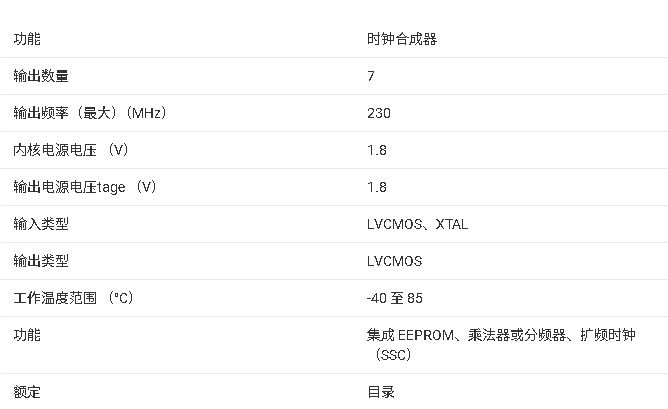

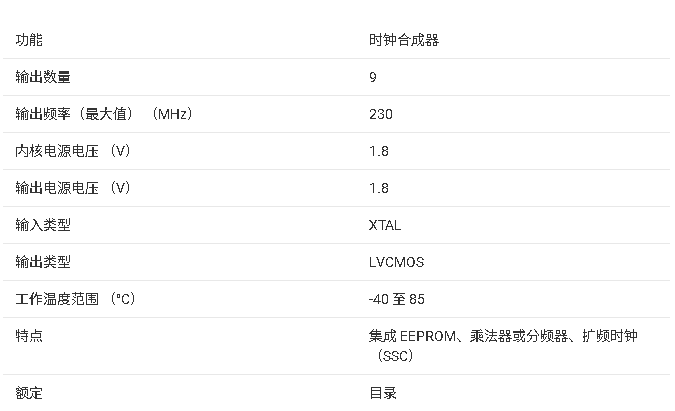

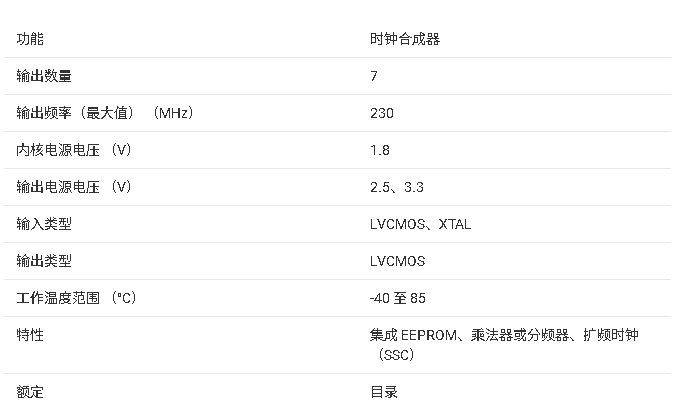

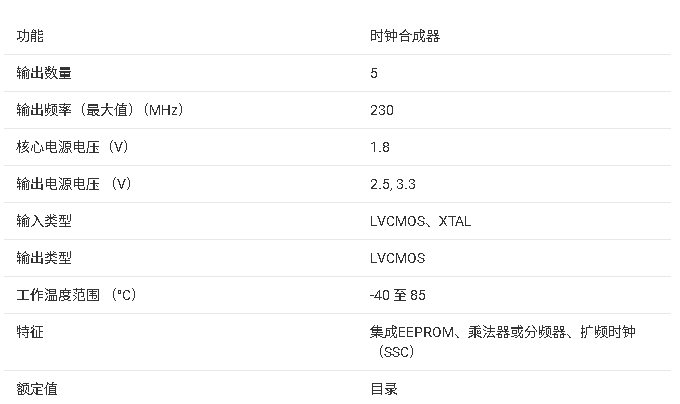

參數

?1. 產品概述?

CDCE706是德州儀器(TI)推出的高性能3-PLL時鐘合成器/乘法器/分頻器,具有以下核心特性:

- ?靈活編程?:支持通過SMBus接口進行電路內編程,無需高壓編程電壓,內置EEPROM存儲配置。

- ?多輸入支持?:兼容晶體(8 MHz至54 MHz)、單端LVCMOS或差分輸入信號(最高200 MHz)。

- ?輸出能力?:6路LVCMOS輸出(最高300 MHz),可編程為互補信號,支持可調輸出擺率控制(SRC)以降低EMI。

- ?低抖動性能?:典型周期抖動60 ps,支持擴頻時鐘(SSC)功能進一步降低系統EMI。

- ?寬工作范圍?:3.3 V供電,工業級溫度范圍(-40°C至85°C),20引腳TSSOP封裝。

?2. 關鍵功能模塊?

- ?PLL架構?:集成3個獨立PLL,支持寬分頻比(M:1-511,N:1-4095),實現零ppm時鐘誤差。

- PLL2支持擴頻時鐘(SSC),可選中心/下擴頻模式。

- ?輸出矩陣?:6×6可編程開關矩陣,每路輸出含7位后分頻器(1-127)和反相邏輯。

- ?控制接口?:

?3. 電氣特性?

- ?電源管理?:

- 工作電流:典型90 mA(全輸出激活時),待機電流50 μA。

- 輸出電源獨立(VCCOUT1/2:2.3 V至3.6 V),支持低電壓驅動。

- ?時序性能?:

- 輸出延遲:3.3 V模式下典型1.7 ns,2.5 V模式下2.2 ns。

- 周期抖動:50 MHz輸出時典型60 ps(單PLL)。

?4. 應用設計?

- ?默認配置?:出廠預編程為27 MHz晶體輸入,6路27 MHz輸出(分頻比8:1)。

- ?SMBus配置?:提供24字節寄存器映射,控制分頻比、PLL選擇、輸出使能等參數。

- ?熱管理?:θJA熱阻66.3°C/W(無氣流),需注意功耗限制(TSSOP封裝最大600 mW)。

?5. 文檔結構?

- ?功能框圖?:詳述PLL、開關矩陣、控制邏輯的互聯關系。

- ?寄存器說明?:包括分頻器設置、輸出配置、SSC控制等位域定義。

- ?時序圖與參數表?:涵蓋SMBus通信協議、抖動特性、絕對最大額定值等。

?6. 典型應用場景?

適用于需高精度時鐘生成的通信設備、嵌入式系統及測試儀器,尤其適合EMI敏感環境。開發工具鏈包含TI ClockPro軟件,簡化PLL設計與編程。

?注意?:具體參數需結合實際配置(如VCO頻率模式、分頻比)計算,文檔提供了詳細公式(如輸出頻率fout = fin × N/(M×P))及示例。

-

可編程

+關注

關注

2文章

1330瀏覽量

41537 -

分頻器

+關注

關注

43文章

537瀏覽量

53679 -

pll

+關注

關注

6文章

985瀏覽量

138326 -

時鐘合成器

+關注

關注

0文章

115瀏覽量

8906

發布評論請先 登錄

TI發布可定制編程的3-PLL時鐘合成器乘法器除法器

CDC906可編程3-PLL時鐘合成器/乘法器/分頻器數據表

?CDCE706 可編程3-PLL時鐘合成器/乘法器/分頻器技術文檔總結

?CDCE706 可編程3-PLL時鐘合成器/乘法器/分頻器技術文檔總結

評論