當前,人工智能正以前所未有的深度重塑半導體產業鏈的核心環節,而作為芯片設計的“引擎”,EDA(電子設計自動化)領域正經歷著從傳統規則驅動向數據智能驅動的范式遷移。主流 EDA 廠商紛紛加大 AI 工具研發的投入,通過引入 AI 技術賦能 EDA 工具,助力芯片設計,這場由 AI 引發的技術變革,不僅在重構芯片設計的效率邊界,更在重新定義 EDA 工具的核心競爭力。

在日前舉行的 CadenceLIVE 中國用戶大會上,Cadence 全球研發副總裁兼三維集成電路設計分析事業部總經理 Ben Gu(顧鑫),圍繞 AI 時代算力需求催生 EDA 領域的變革,分享了 Cadence 在 3D-IC 以及 AI 領域的創新實踐。

AI 推動 EDA 工具進化

近年來, AI 引發的算力革命,在對人們的工作和生活產生影響的同時,也為半導體行業帶來機遇和挑戰。IDC 的研究數據顯示,由于 AI 的驅動,2030 年半導體市場規模將突破 1 萬億美元。

AI 不僅驅動了芯片設計的進步,在算力需求下,也讓芯片設計變得更加復雜。更多的晶體管堆疊,更復雜的 3D 集成電路系統,以及領先的晶圓代工廠推動更先進的工藝節點和制造方案等,都對芯片設計系統帶來巨大的挑戰。

在 Ben 看來,過去二三十年 EDA 行業發展迅速的重要的原因之一在于受到摩爾定律驅動,而 AI 對于推動芯片設計流程的重塑將具有同樣的效能。新的 EDA 工具用來發展新一代的 AI 芯片,提升新一代的 AI 性能。同樣,新的 AI 技術也會被用于發展下一代的 EDA 技術提升 EDA 的性能。如此往復,推動整個行業健康加速向前發展。

“據我們統計,2025 年,已經有超過一半的客戶在使用 Cadence 提供的不同形式的 AI 工具來進行芯片設計。預計到 2030 年,AI 在芯片設計流程中的占比將超過 80%,從而使整個設計流程大幅自動化。其中,AI 智能體將發揮重要作用。未來兩三年,除了為客戶提供 EDA 工具,我們更希望能夠提供 EDA 的 AI 智能體。” Ben 表示。

應對算力挑戰的 3D-IC

人工智能的發展,特別大型神經網絡模型的訓練和推理,對算力提出極高要求。傳統的二維集成電路(2DIC),逐漸顯現出局限性,面臨 “內存墻”“互連瓶頸” 和 “散熱極限” 等多重阻力,無法滿足人工智能對高密度計算與高帶寬內存的緊耦合要求。

因此,3D-IC 成為行業在應對 AI 時代算力挑戰時的突破方向,通過 2.5D、3D 或 3.5D 的堆疊來進一步提高芯片算力和芯片之間的帶寬。比如,臺積電一直在積極推進 CoWoS 等堆疊技術的創新演進。而其下一代系統級芯片封裝技術 SoW-X(System-On-Wafer),通過在 Wafer 上集成數十個芯片,實現 RDL 互聯,將能夠非常顯著地提升整體芯片算力。

在 Ben 看來,3D-IC 將成為未來五到十年非常熱門的話題并帶來革命性的創新。同時,由于系統的復雜性,比如多個芯片堆疊在極小的芯片上將產生巨大功耗等,也為 3D-IC 設計帶來更多挑戰。為了讓 3D-IC 的設計符合需求,需要解決包括散熱、時序(Timing)、壓降分析(IR drop)等一系列問題。

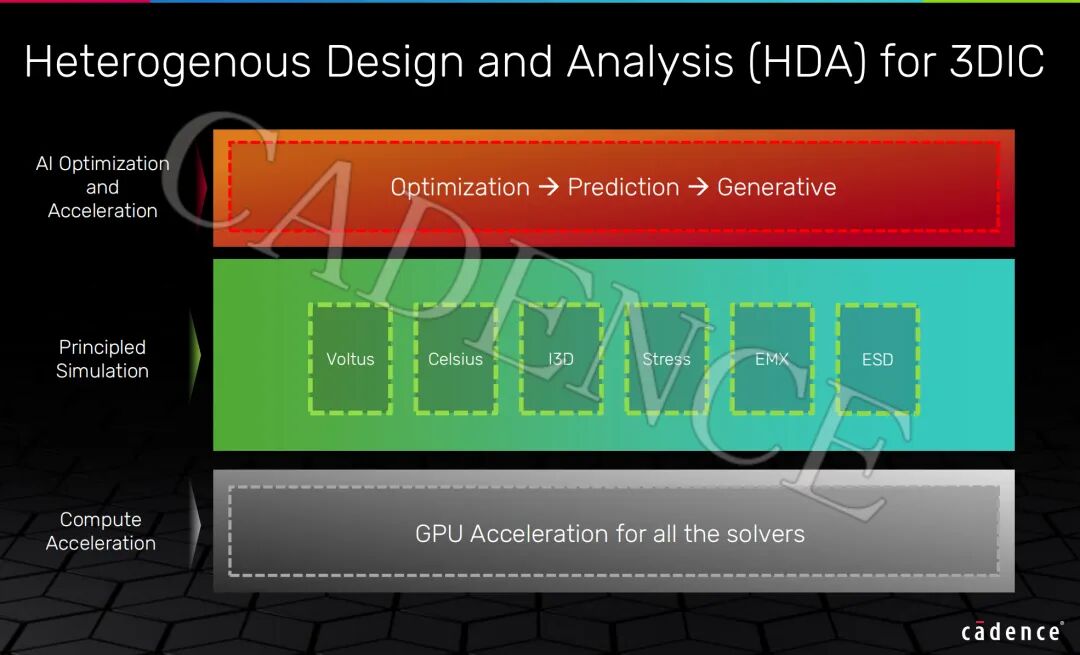

據 Ben 介紹,今年 3 月,Cadence 將與 3D-IC 相關的設計分析產品重新組合在一起,成立了全新的事業部 HDA(Heterogeneous Design Analysis),通過三個層面的創新工作,應對 3D-IC 所帶來的高速發展機遇和挑戰。

HDA 通過集成各種 3D-IC 需要的分析工具(電、磁、熱、力等),并與 Cadence 的設計平臺整合在一起。此外,我們還計劃將所有分析產品都移植到 GPU 上,實現大規模的性能加速,進而訓練 AI 模型實現進一步加速,幫助設計工程師可以用 AI 模型來探索設計空間并得到最優化的設計結果。

IntegrityTM:助力 3D-IC 設計

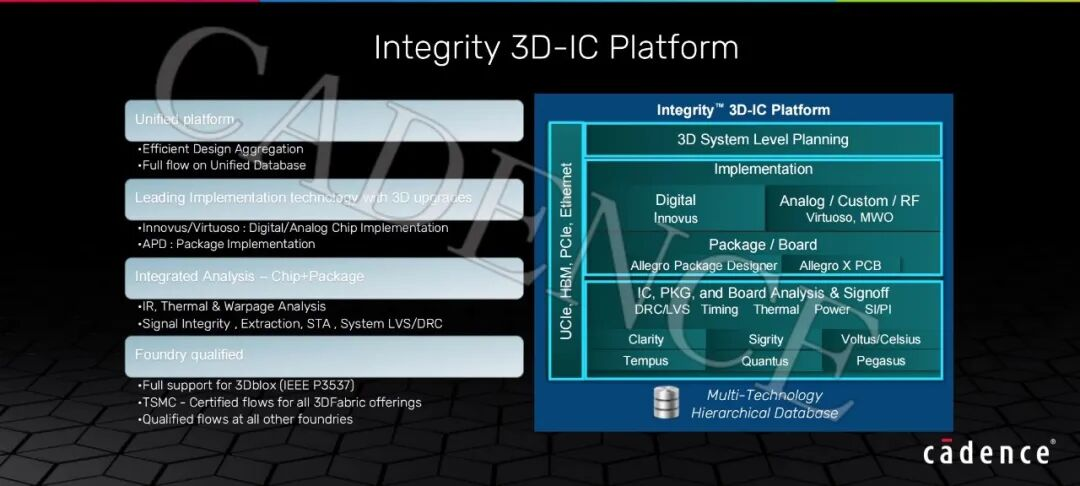

在產品側,為應對 3D-IC 設計所帶來的挑戰,2021 年,Cadence 推出 IntegrityTM3D-IC 設計平臺,通過集成統一的操作界面和數據庫,將所有與 3D-IC 相關的設計數據(包括 routing、placement 等)融合在一起,為客戶提供一站式 EDA 工具服務。

IntegrityTM不僅同 Cadence 領先的數字和模擬領域的工具 Innovus 和 Virtuoso 緊密結合,還能與 Cadence 的各種分析工具,尤其是多物理場仿真分析工具結合進行系統分析,從而優化設計。

據 Ben 介紹,過去幾年,Cadence 持續投入提升 IntegritiyTM的性能和兼容能力,目前已實現和主要的晶圓廠伙伴及封測廠商的緊密合作,且已被所有的行業頭部客戶采用,包括領先的 AI 廠商和服務器廠商。

3D-IC 通過堆疊多層芯片實現高密度集成,但不同芯片因功能、工藝、尺寸差異大,且堆疊方式(如 TSV 位置、RDL 布線、散熱路徑等)會直接影響整體性能。因此,IntegrityTM3D-IC中的 System Planner(系統規劃器)便十分重要,能夠在芯片設計初始階段提供對整個系統的全局規劃,從而得到最佳的系統表現。同時,IntegrityTM3D-IC 平臺支持 Cadence 自研布線技術,能夠實現芯片間復雜線路的連接,考慮到先進封裝存在各種復雜布線需求,IntegrityTM3D-IC 還支持自動布線和自動分組。

此外,針對 Cadence 的多物理場仿真解決方案,IntegrityTM3D-IC 能夠實現這些工具在芯片中的內置和深度聯動,幫助客戶驗證結果并優化設計。

Voltus:全新升級

Voltus 是 Cadence 推出的一款電源完整性分析工具,已有 11 年歷史。據 Ben 介紹,今年 Cadence 計劃推出新一代 Voltus 產品——Voltus Infinity,大幅提升 Voltus 內部算法,包括針對GPU加速的XD(neXt generationDynamic)、針對廣泛仿真分析覆蓋度的算法XC(eXtremeCoverage),以及針對可用性分析和調試的XU(neXt generationUser interface)等三項關鍵技術。

據了解,Voltus-XD 將 Wafer 中所有的 IR drop(壓降分析)仿真引擎從 CPU 遷移到 GPU,通過采用 Voltus 的 GPU 分析引擎實現加速,從而大幅縮短模擬時間。

今年 5 月,Cadence 推出了超級計算機——Millennium M2000,將 NVIDIA GPU 技術與 Cadence 的全套計算軟件及 AI 功能相結合(包括 XD 技術),與傳統 CPU 集群需要兩周的時間相比,工程師現可在一天內完成芯片級電源完整性模擬。

在提升仿真分析覆蓋度方面,過去因為仿真性能受限等原因,通常芯片設計在進行 Voltus 和 IR drop 仿真時,只能覆蓋 20 個或 100 個時鐘周期(Cycle)以及芯片的少部分應用。而升級后的仿真引擎 Voltus-XC,可以將時鐘周期提升至百萬級別,使得芯片設計廠商能夠進行更充分的驗證,從而降低芯片設計風險,讓簽核(Sign Off)環節更加有保證。

在可用性以及可調試性方面,Voltus-XU 采用了新一代的用戶界面,同時引入了 AI 助手(集成Cadence 大語言模型和 JedAI),便于用自然語言同 EDA 圖形界面互動,debug、查詢設計結果。

AI 賦能多物理場仿真

相比傳統 2D 芯片,3D-IC 的優勢是“縮小面積、提升性能、降低功耗”,但堆疊結構也直接帶來了大規模互聯產生的散熱和“機械失效”(Mechanical Failure)等方面的新問題。

在 Cadence 的 EDA 工具生態中,Thermal/Mechanical(熱學 / 機械應力分析工具) 是其 “多物理場解決方案(Multiphysics Solution)” 的重要組成部分。

Ben Gu 表示,準確的 Thermal 仿真對 3D-IC 設計至關重要,Cadence 的 Celsius Thermal Solver 自2019 年面世以來,經過多年打磨已完全能夠應對3D-IC 的設計挑戰。Celsius 能夠同 Innovus、Voltus 有非常緊密地結合,從 Voltus 取得 Power 的數據后進行仿真分析,再將結果反饋給Voltus得到更準確的IR drop結果。目前,Celsius 3D-IC 方案已經被多家頭部客戶采用。

而為應對機械失效等方面的挑戰,據 Ben 介紹,Cadence 即將推出 Tenacity Stress Solver。為應對 3D-IC 多達數百萬個凸塊(bump)所帶來的復雜應力(stress) 分析問題,Tenacity 能夠提供層級化的解決方案(Hierarchical solution),借助于 AI 和 GPU 的技術加速,在不犧牲精度的情況下,提供快速的仿真解決方案。

此外,針對常規 3D-IC 仿真較為耗時等問題,Cadence 還即將推出 Celerity AI 加速解決方案,加快設計流程提升設計表現。Celerity 可以通過Cadence 內部生成的大量設計數據訓練仿真大模型,再交由客戶微調優化,最終用神經網絡替代傳統仿真流程,提升芯片設計效率。

結語

從 Cadence 在 AI 時代的 EDA 創新實踐中,能夠清晰地看到 AI 正從 “輔助工具” 升級為驅動 EDA 工具研發與芯片設計變革的“核心引擎”。

在領先的 EDA 廠商積極創新探索下,由 AI 賦能的 EDA 工具正助力芯片設計實現“降維破局”。未來,隨著 EDA AI 智能體的進一步落地、多物理場仿真與 AI 的進一步融合,EDA 工具將從 “自動化” 邁向 “自主化”,不僅能幫助芯片設計團隊更高效地突破先進工藝與復雜集成的技術壁壘,更將持續夯實 AI 芯片創新的底層根基,最終推動半導體行業在算力革命中實現更具想象力的突破。

-

Cadence

+關注

關注

68文章

1022瀏覽量

147243 -

芯片設計

+關注

關注

15文章

1167瀏覽量

56770 -

eda

+關注

關注

72文章

3135瀏覽量

183519 -

AI

+關注

關注

91文章

40726瀏覽量

302383

原文標題:Cadence:以全棧 AI 技術破解 3D-IC 設計難題

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Cadence Conformal AI Studio三大核心引擎重塑IC驗證

重磅合作!Quintauris 聯手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

AI重塑EDA,3D-IC成關鍵戰場:Cadence的洞察與應變

山東移動攜手華為榮獲NetworkX 2025電信領域最具創新AI實踐獎

Cadence AI芯片與3D-IC設計流程支持臺積公司N2和A16工藝技術

《電子發燒友電子設計周報》聚焦硬科技領域核心價值 第29期:2025.09.15--2025.09.26

【今晚7點半】正點原子 x STM32:智能加速邊緣AI應用開發!今晚正點原子B站直播間等你

《電子發燒友電子設計周報》聚焦硬科技領域核心價值 第28期:2025.09.8--2025.09.12

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+內容總覽

生成式 AI 重塑自動駕駛仿真:4D 場景生成技術的突破與實踐

Cadence在3D-IC以及AI領域的創新實踐

Cadence在3D-IC以及AI領域的創新實踐

評論