上一期內容中,我們為大家介紹了如何調整DDS設置。本期德思特將帶大家進一步深入,**解析固有頻率與幅度斜率的相關知識,并探討頻率與幅度斜率中存在的量化誤差——包括時間量化誤差、行為時間誤差以及值量化誤差。**掌握這些概念,將幫助我們更全面地理解信號生成的精確性與穩定性。

01

固有頻率

和斜率頻率說明

除了頻率、幅度和初始相位之外,德思特DDS 模塊還支持線性頻率和幅度斜率作為動態參數。

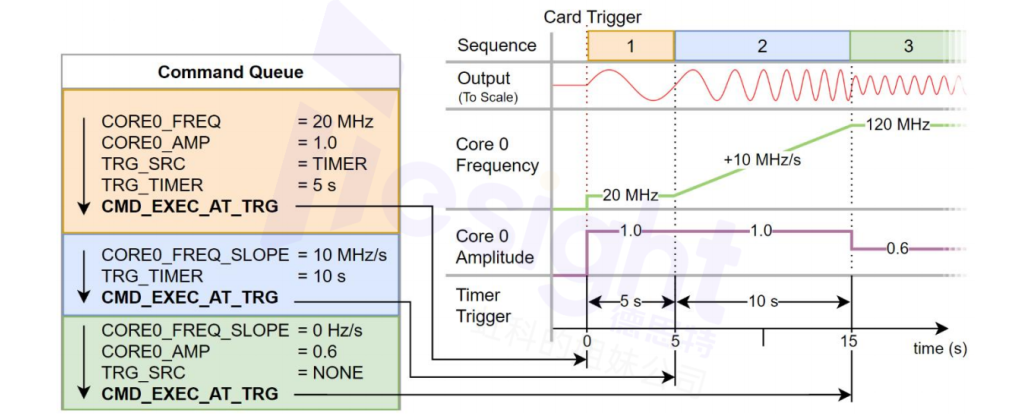

具有線性斜率的序列編程

序列順序

- 初始重置后:所有參數設置為 0,觸發源設置為外部卡觸發器。

- 在卡觸發事件時:將頻率設置為 20 MHz,幅度設置為 1.0。為了在 5 秒后切換到下一個序列,將觸發源設置為內部定時器,該定時器開始計時到 5 秒,此時觸發下一個序列。

- 核心頻率:以 10 MHz/秒的線性平穩速率增加。因此,10 秒后達到最終頻率 120 MHz。

- 通過將斜率設置為 0 來停止斜率,同時將幅度設置為 0.6。最后,將觸發源設置為 NONE,這將禁用內部定時器。

02

斜率量化機制與誤差

雖然斜率實際上是線性的,但它們是在卡的邏輯中以離散步驟計算的,具有量化的時間和值分辨率。對于TS-66xx DDS 模塊,最小斜率刷新速率 t_re 為 6.4 ns,這對于它們設計的大多數應用來說綽綽有余。

由于這些量化的計算,斜率增量和時間分辨率是有限的,并且可能在實際值和所需設置值之間存在一定的量化誤差。

通常,這些效果僅在異常長的斜率(其最小斜率步長達到)或短斜率(其時間量化變得相關)的順序為秒時才可見。為了減輕這些效果,應在斜率結束時手動設置最終頻率。

時間量化誤差

當為定時器輸入一個浮點值時,驅動程序會將其舍入到 t_re 步長的完整時鐘周期,從而創建時間誤差。 對于約 1 毫秒長的斜率,此量化誤差在 +/- 3.2 ns 或 3.2 ppm 的范圍內,對于許多應用來說可以忽略不計。 可以通過在您的應用程序和編程中考慮此量化,并且只使用 t_re 步長的時間周期來減輕它。

行為時間誤差

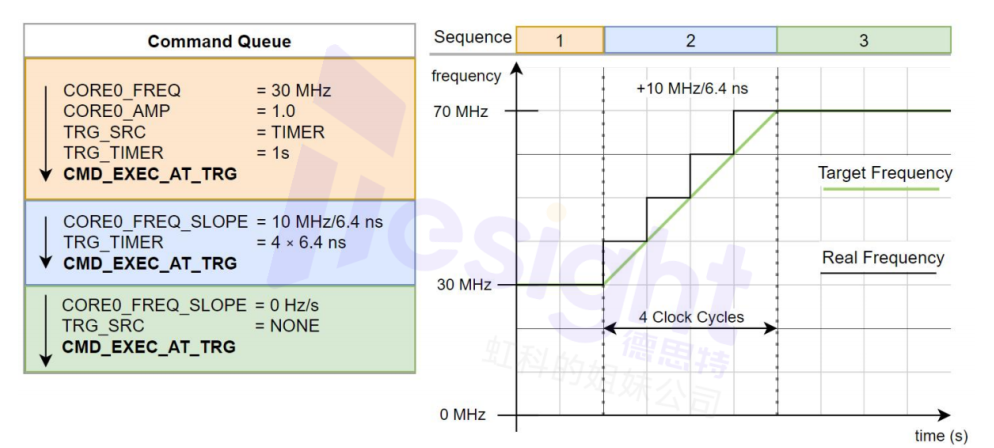

此外,還可能發生另一種時間誤差:如果僅在執行事件處有斜率命令,則頻率將與觸發事件同時增加,導致預期的最終頻率,如圖1所示。

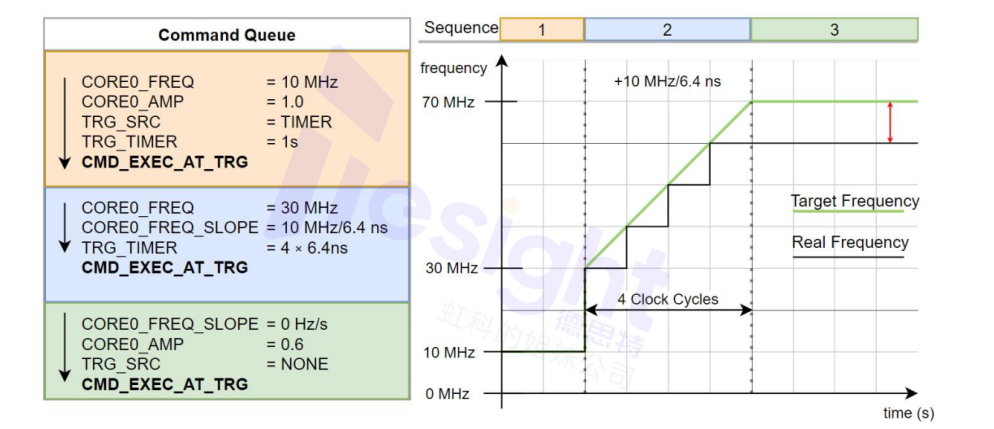

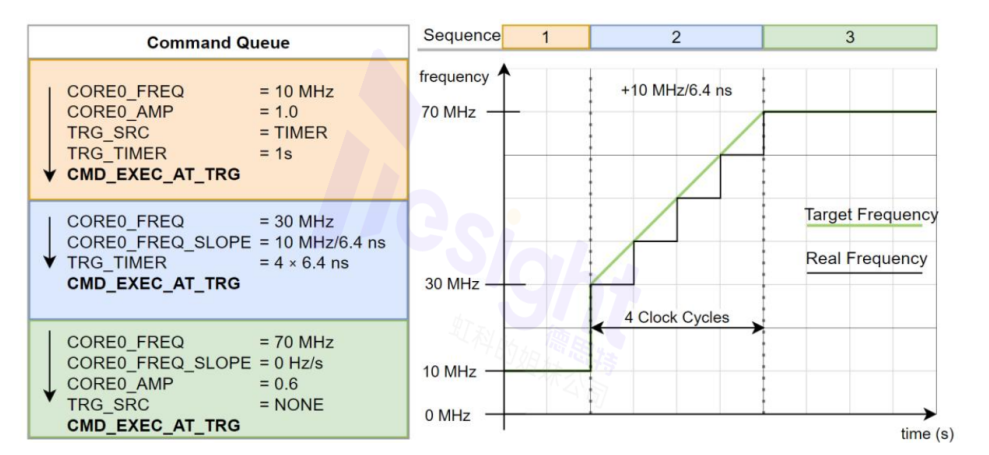

然而,當在同一個執行事件中設置頻率和斜率速度時,首先在第一個時鐘周期設置頻率,然后頻率在下一個時鐘周期增加,如圖 2所示。雖然這種行為在技術上并不錯誤,但因此斜率比預期短一個時鐘周期 t_re。這種行為可以通過顯式設置最終頻率或通過增加一個增量調整起始頻率來輕松解釋,如圖3所示。

請注意,為了顯示目的,選擇了一個非常短的斜率周期為 4 個時鐘周期,目前還不可能使用EXEC_AT_TRIG 命令,因為最小定時器時間在 100 ns 的范圍內。對于毫秒數量級的斜率周期,這種影響在百萬分之幾的范圍內。

圖1:首先設置啟動頻率,

然后啟動一個斜率

圖2:在同一執行事件中

設置的頻率和斜率導致不同的最終值

圖3:同一執行事件的頻率和斜率集;

最終值是顯式設置的

值量化誤差

為了減少值誤差, 斜率在內部以比DDS的頻率分辨率fstep更高的斜率fstep分辨率進行計算。 對于持續時間在秒量級的較長時間,可以設置一個步進除數,進一步提高分辨率,但通常對于毫秒時間尺度內的應用程序來說并不需要。

fstep可以通過讀取API中的寄存器SPCDDS AVAILFREQ_SLOPE STEP來讀取, fstep可以通過讀取寄存器SPC_DDS_AVAIL_FREQ_STEP來讀取。

示例:

德思特66xx DDS模塊具有大約0.3 Hz的頻率分辨率fstep。 如果您將斜率速度設置為fstep/tre,則頻率每6.4 ns會 增加exactly 0.3 Hz。 如果這也將是最小頻率斜率分辨率fstep,則低于0.3 Hz/6.4 ns的斜率值將不可能,并且不會執行任何斜率。

因此,在一秒鐘后, 只能進行量化頻率變化0Hz、47 MHz、 247 MHz、 347 MHz等。

總結

為了計算最大頻率斜率量化誤差, 只需將斜率分辨率乘以斜率持續時間。 我們除以2, 因為我們向上或向下舍入到值之間的值:ferror=fstep·△t/2

實際實現的頻率斜率分辨率fstep高于fstep,fstep=694 Hz/s。 因此, 如果您想在 1毫 秒內從1 MHz增加到2MHz,您將最終獲得最大誤差為fstep ·△t /2 = 0.348 Hz, 這對于其設計的大多數應用程序來說可以忽略不計。

相關產品

德思特PCIe板式AWG

支持最高10 GS/s采樣率和16 bit高分辨率,確保高精度、高帶寬信號的生成,滿足嚴苛的測試需求。單卡提供最多8個通道,并可通過星形集線器同步技術擴展至64個同步通道,適用于大規模多通道測試場景。基于PCIe總線架構,可輕松集成到自動化測試系統,適用于實驗室研發或產線測試,提供高密度、低延遲的信號生成方案。

德思特PXIe板式AWG

支持最高1.25 GS/s采樣率和16 bit高分辨率,確保高精度、高帶寬信號的生成,滿足嚴苛的測試需求。單卡提供最多4個通道,并可通過星形集線器同步技術擴展至64個同步通道,適用于大規模多通道測試場景。基于PXIe總線架構,可輕松集成到自動化測試系統,適用于實驗室研發或產線測試,提供高密度、低延遲的信號生成方案。

德思特任意波形發生器

可輕松生成復雜脈沖序列、一系列雷達脈沖,驅動電光和聲光調制器、帶有損傷的脈沖射頻信號、高斯脈沖、多電平脈沖、脈沖幅度調制(PAM)和偽隨機二進制序列(PRBS)信號、用于前沿研究和量子計算的脈沖。

END

本期我們帶大家解析了固有頻率與幅度斜率的相關知識,并探討了其中涉及的量化誤差——包括時間量化誤差、行為時間誤差與值量化誤差。下期我們將進入相位偏移模式的內容,精彩繼續,干貨不容錯過,敬請期待!

審核編輯 黃宇

-

定時器

+關注

關注

23文章

3368瀏覽量

123593 -

DDS

+關注

關注

22文章

684瀏覽量

156581

發布評論請先 登錄

德思特應用 | 突破10ns脈沖限制:德思特脈沖發生器如何解決NVM測試的超快激勵與高保真挑戰

德思特干貨 | DDA技術深度解析系列(二):如何改變DDS設置?

天馬微電子成功實現185Hz刷新率AMOLED顯示屏量產落地

德思特方案 | 研發量產一機搞定,德思特脈沖發生器TS-PG1072為激光芯片測試降本增效

德思特方案 | 整車 GNSS 產線測試,3 分鐘高精度驗證

混頻器:雷達/衛星通信核心器件,德思特脈沖發生器助力變頻測試高效落地

【干貨】必看!刷新率全解析:從原理到實戰,告別卡頓拖影的終極指南

浮思特 | 智能洗衣背后的靜默力量,ABOV單片機如何實現精準控制?

LED全息顯示屏:1920Hz與3840Hz刷新率對比解析

在cypress 3014進行多種分辨率刷新率切換的操作,是否可行?

最新動態!德思特受邀亮相粵港科創盛會,展示國產高精度定位硬實力!

6.4ns刷新率!德思特DDS模塊如何實現極致精密的動態斜率控制?

6.4ns刷新率!德思特DDS模塊如何實現極致精密的動態斜率控制?

評論