在電子電路系統(tǒng)設(shè)計(jì)中,工程師處理ESD有時(shí)候總覺得沒有頭緒,主要原因是ESD測(cè)試難以量化,每次測(cè)試的結(jié)果也會(huì)存在差異,所以憑感覺處理起來(lái)很‘玄學(xué)’。 簡(jiǎn)單說(shuō)起來(lái)就是ESD對(duì)系統(tǒng)內(nèi)部存在干擾,但處理起來(lái)常常就是一團(tuán)亂麻,監(jiān)測(cè)不到ESD泄放路徑。單從電路增加ESD防護(hù)設(shè)計(jì)維度有時(shí)候是無(wú)法達(dá)到目的,所以PCB設(shè)計(jì)是解決ESD防護(hù)問題中非常重要的一環(huán),但必要時(shí)還是要配合ESD器件共同達(dá)到抑制的目的。

無(wú)論是普通電路系統(tǒng)還是高速電路系統(tǒng),對(duì)于EMC的處理都很有必要,今天就分享幾個(gè)PCB Layout幾個(gè)原則,可以大大減小EMC出現(xiàn)問題的概率。PCB布局的ESD防護(hù)思路是:敏感的信號(hào)或者電路遠(yuǎn)離靜電放電測(cè)試點(diǎn),信號(hào)環(huán)路面積最小化噪聲耦合,降低參考地平面電位差保持信號(hào)參考電平穩(wěn)定。

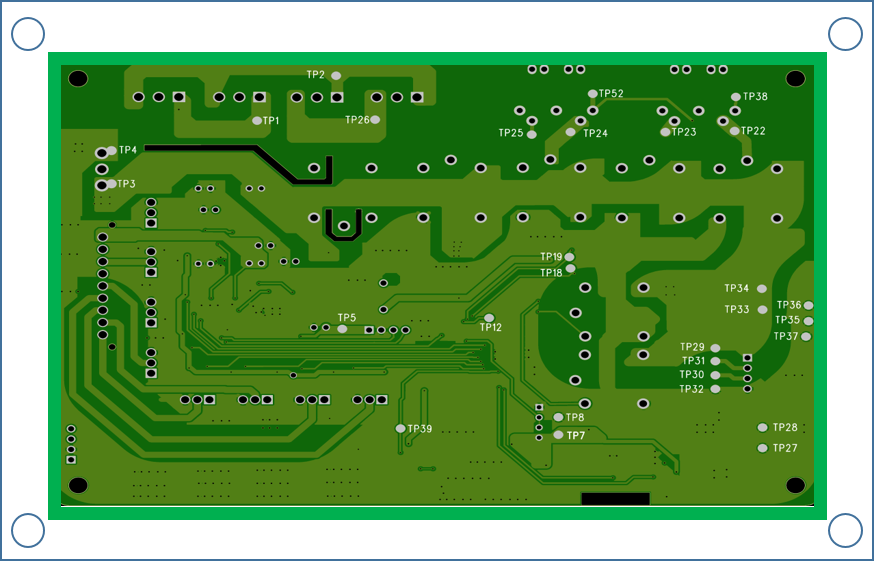

圖1.PCB Layout示意圖

如圖1所示,PCB Layout設(shè)計(jì)建議參考

1. 單層PCB設(shè)計(jì)時(shí),設(shè)置良好的接地平面和電源平面,信號(hào)線盡可能緊靠電源平面層或接地平面,保證信號(hào)回流時(shí)的通路以最短,信號(hào)環(huán)路最小的原則。

2. 多層PCB層疊設(shè)計(jì)必須保證比較完整的GND平面,所有的 ESD泄放路徑直接通過(guò)過(guò)孔連接到這個(gè)完整的GND平面,其他層盡可能多的鋪 GND。

3. 在PCB四周增加地保護(hù)環(huán)路,關(guān)鍵信號(hào)(RESET/Clock等)與板邊距離不小于 5mm,同時(shí)必須與布線層的板邊GND銅皮距離不小于 10mils。

4. 在電源和接地之間設(shè)計(jì)高頻旁路電容,要求等效串聯(lián)電感值(ESL)和等效串聯(lián)電阻(ESR)越小越好

5. 對(duì)于部分ESD 整改難度較大的IO,可將IO GND獨(dú)立出來(lái),與電源GND用磁珠連接,以防止ESD能量進(jìn)入GND。

另外,在PCB布局時(shí)做好敏感器件的保護(hù)、隔離,一些敏感模塊如射頻、音頻、存儲(chǔ)器可以添加屏蔽罩。但屏蔽罩的整體成本太高,ESD保護(hù)器件具有更好的性價(jià)比,但如何選用合適的ESD器件才是關(guān)鍵,配合PCB的線路設(shè)計(jì)達(dá)到防護(hù)目的。

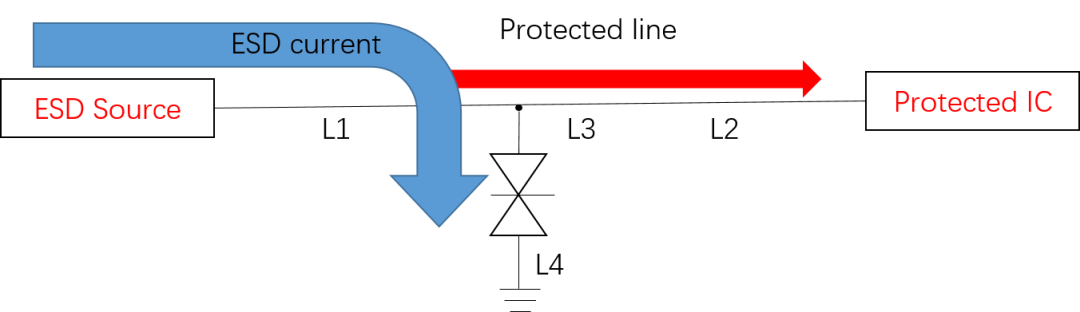

圖2.ESD泄放路徑避免能量進(jìn)入保護(hù)電路

放電事件通常通過(guò)接口(如連接線)或人工端口(如USB、音頻)迫使電流 IESD (圖2)迅速進(jìn)入系統(tǒng)。使用ESD二極管保護(hù)系統(tǒng)免受ESD影響,取決于ESD二極管能否將 IESD 分流到地,在選用ESD器件時(shí)需要注意如下參數(shù):

1.工作電壓 (VRWM)

VRWM工作電壓是指建議器件工作電壓范圍,應(yīng)用電路最高電壓超過(guò)該值時(shí)會(huì)導(dǎo)致漏電流增大,從而損壞器件和影響系統(tǒng)運(yùn)行。建議電路應(yīng)用電壓≤ ESD 器件的工作電壓VRWM。

2.結(jié)電容(Cj)

ESD器件與信號(hào)并聯(lián)使用,而ESD半導(dǎo)體設(shè)計(jì)時(shí)的寄生電容,對(duì)于高速信號(hào)應(yīng)最大限度地減小結(jié)電容Cj以保持信號(hào)完整性。

3. IEC 61000-4-2等級(jí)(Contact discharge/ Air discharge)

IEC61000-4-2等級(jí)體現(xiàn)器件在接觸放電和空氣放電的穩(wěn)健性。接觸放電是指用靜電槍向ESD器件放電時(shí)該器件可承受的最大電壓。空氣放電是指使用靜電槍空氣間隙向ESD器件放電時(shí)該器件可承受的最大電壓。

4.ESD器件通道數(shù)

ESD器件有單通道和多通道不同封裝類型。多通道是內(nèi)部集成多個(gè)單通道器件,根據(jù)應(yīng)用需求,多通道器件可實(shí)現(xiàn)更小尺寸方案并節(jié)省PCB空間,當(dāng)然,單通道器件可提供更高的設(shè)計(jì)靈活性。

5.單向與雙向

雙向ESD器件可同時(shí)具有正負(fù)工作電壓的電路中(±3.3V等),因此,雙向ESD器件可支持?jǐn)?shù)據(jù)信號(hào)在正負(fù)電壓之間切換的接口(如模擬信號(hào)/RS233等)。單向ESD只有工作在正電壓范圍,但具有更好的負(fù)鉗位。

6. 鉗制電壓(Vc)

鉗制電壓表示瞬態(tài)脈沖下作用于ESD器件時(shí)2端的壓降,鉗制電壓越低意味能更好的保護(hù)后級(jí)的電子元件。瞬態(tài)測(cè)試包含靜電和浪涌,不同測(cè)試條件下鉗制電壓不同,選型前確認(rèn)具體測(cè)試需求和后級(jí)極限損壞電壓,保證器件選型的合理性

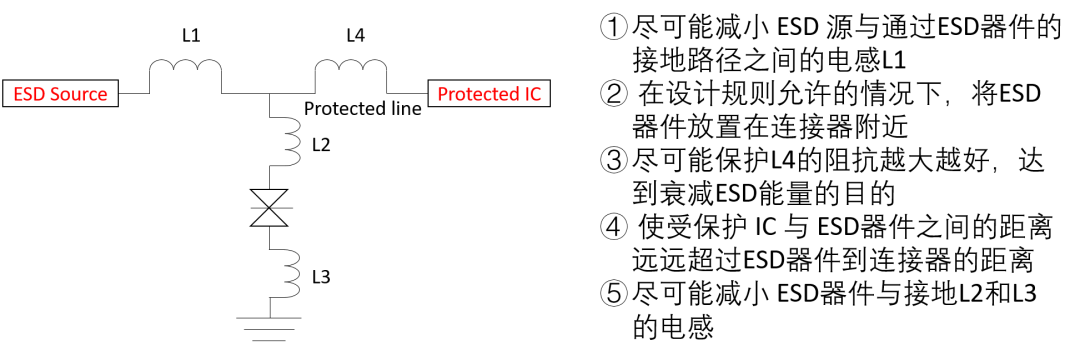

綜上,要想從PCB布局+ESD二極管實(shí)現(xiàn)最好的靜電防護(hù),很大程度上需要從整機(jī)系統(tǒng)上優(yōu)化設(shè)計(jì)。因?yàn)樵O(shè)計(jì)人員無(wú)法控制 IESD,所以降低對(duì)地阻抗是將鉗制電壓最小化的主要方法。設(shè)計(jì)建議如下(圖3)。

圖3.ESD二極管PCB優(yōu)化建議

產(chǎn)品推薦

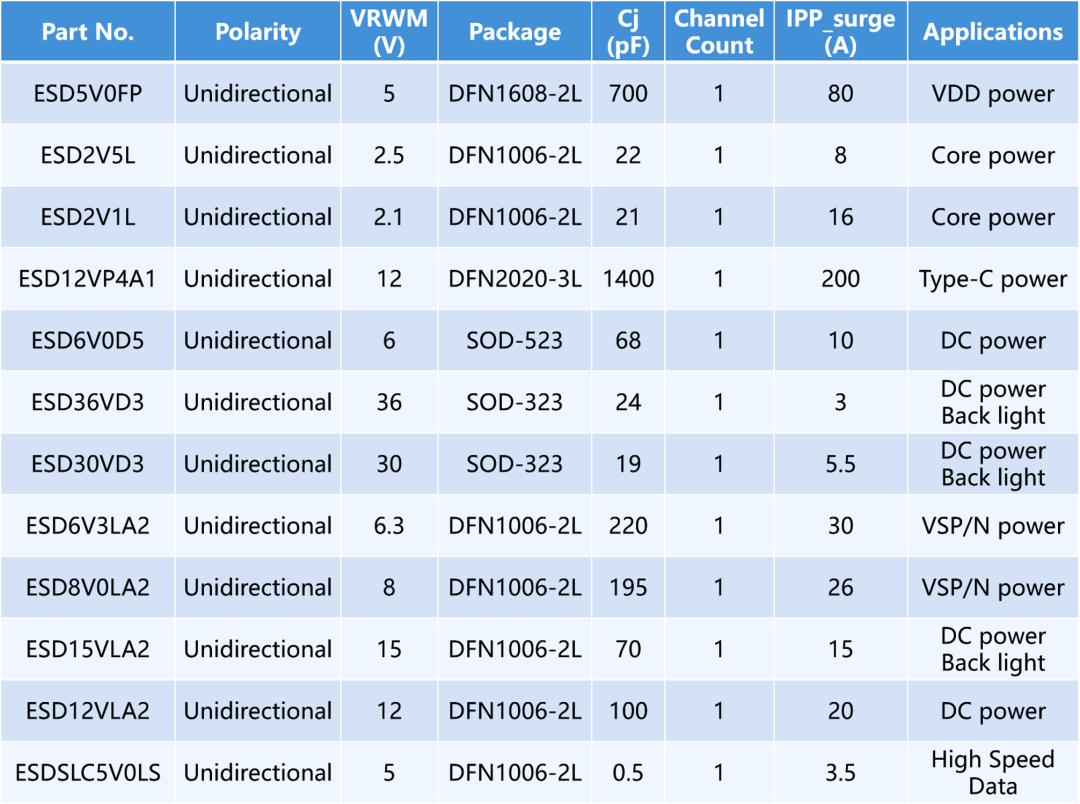

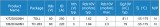

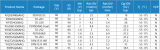

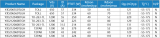

揚(yáng)杰科技推出應(yīng)用于電源和信號(hào)單向TVS方案,在瞬態(tài)脈沖負(fù)壓情況下,單向ESD器件約-0.7V會(huì)Forward導(dǎo)通,而雙向結(jié)構(gòu)ESD器件無(wú)論在正壓還是負(fù)壓條件下,2個(gè)方向均要擊穿才會(huì)導(dǎo)通;如果電源或主芯片為高階制程,電源或I/O防護(hù)電路變得十分脆弱,在負(fù)壓條件下會(huì)導(dǎo)致主芯片內(nèi)部的襯底二極管率先導(dǎo)通而燒毀,從而導(dǎo)致主芯片損壞。表1是我司新開發(fā)的單向結(jié)構(gòu)ESD和具體應(yīng)用,以應(yīng)對(duì)在負(fù)壓瞬態(tài)脈沖下敏感問題 。

-

ESD

+關(guān)注

關(guān)注

50文章

2363瀏覽量

178658 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4901瀏覽量

93917 -

硬件電路

+關(guān)注

關(guān)注

39文章

263瀏覽量

30127 -

Pcb layout

+關(guān)注

關(guān)注

6文章

100瀏覽量

29912 -

揚(yáng)杰科技

+關(guān)注

關(guān)注

1文章

146瀏覽量

11919

原文標(biāo)題:干貨分享 | 如何通過(guò)硬件電路優(yōu)化降低ESD干擾

文章出處:【微信號(hào):yangjie-300373,微信公眾號(hào):揚(yáng)杰科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何通過(guò)優(yōu)化電能質(zhì)量在線監(jiān)測(cè)裝置的散熱系統(tǒng)來(lái)降低功耗?

揚(yáng)杰科技先進(jìn)封裝項(xiàng)目一期正式開工

如何降低電磁干擾對(duì)電能質(zhì)量在線監(jiān)測(cè)裝置精度的影響?

如何降低電能質(zhì)量在線監(jiān)測(cè)裝置對(duì)傳導(dǎo)干擾的敏感度?

EMC干擾問題整改:從ESD死機(jī)到通過(guò)CE認(rèn)證的全記錄

揚(yáng)杰科技與北京一高科技達(dá)成合作

揚(yáng)杰科技推出SOD-323HE封裝TVS新品

揚(yáng)杰科技推出用于清潔能源的N60V MOSFET產(chǎn)品

揚(yáng)杰科技拜訪維揚(yáng)經(jīng)濟(jì)開發(fā)區(qū)管委會(huì)

博世集團(tuán)蒞臨揚(yáng)杰科技參觀交流

揚(yáng)杰科技亮相PCIM Europe 2025 以硬核技術(shù)驅(qū)動(dòng)能源變革

如何布線才能降低MDDESD風(fēng)險(xiǎn)?PCB布局的抗干擾設(shè)計(jì)技巧

揚(yáng)杰科技N60V SGT MOSFET產(chǎn)品介紹

揚(yáng)杰科技全資子公司MCC(越南)工廠正式通線

揚(yáng)杰科技推出全新SiC MOSFET產(chǎn)品

揚(yáng)杰科技分享如何通過(guò)硬件電路優(yōu)化降低ESD干擾

揚(yáng)杰科技分享如何通過(guò)硬件電路優(yōu)化降低ESD干擾

評(píng)論