前 言

本文主要介紹基于全志科技T113與FPGA的核間通信案例,適用開發環境如下。

Windows開發環境:Windows 7 64bit、Windows 10 64bit

虛擬機:VMware15.5.5

Linux開發環境:Ubuntu18.04.4 64bit

U-Boot:U-Boot-2018.07

Kernel:Linux-5.4.61、Linux-RT-5.4.61

LinuxSDK:T113_Tina5.0-V1.0(Linux)

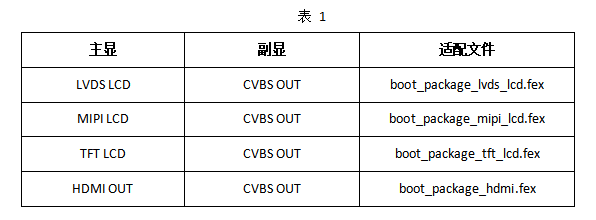

無特殊說明情況下,默認基于NAND FLASH配置評估板進行演示,使用USB TO UART0作為調試串口,通過Linux系統啟動卡(Micro SD方式)啟動系統。

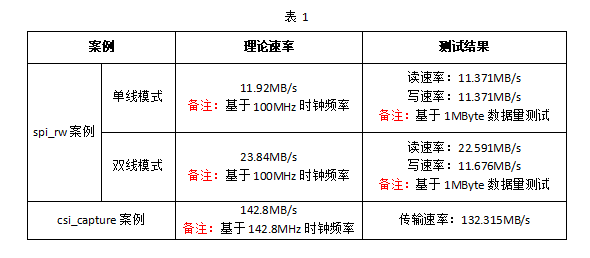

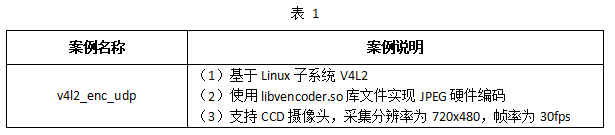

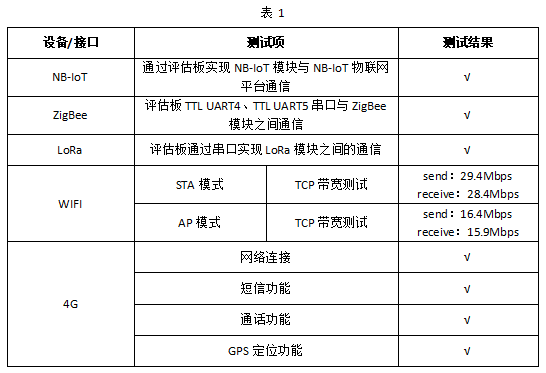

本文檔對應案例的測試結果說明如下表所示。

spi_rw案例

案例說明

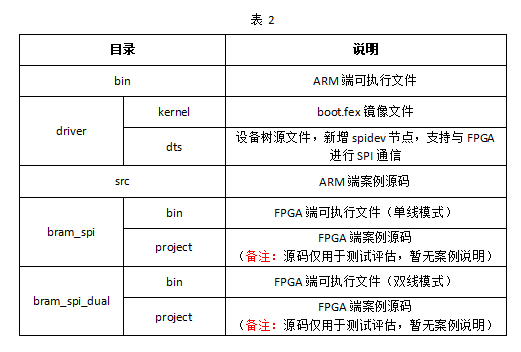

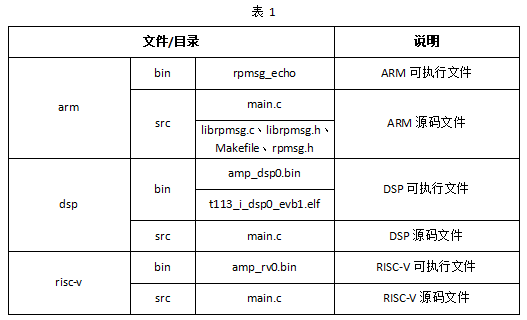

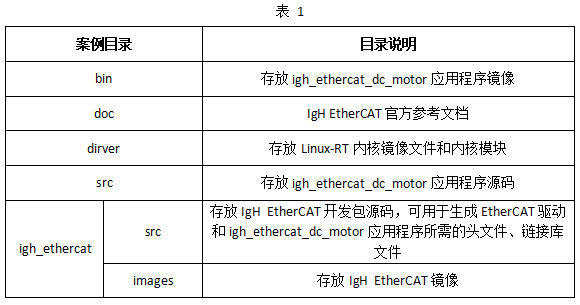

案例功能:主要演示T113(ARM Cortex-A7)與Spartan-6(FPGA)處理器之間的SPI通信。案例源碼位于“4-軟件資料Demobase-demosspi_rw”目錄下,具體目錄結構說明如下。

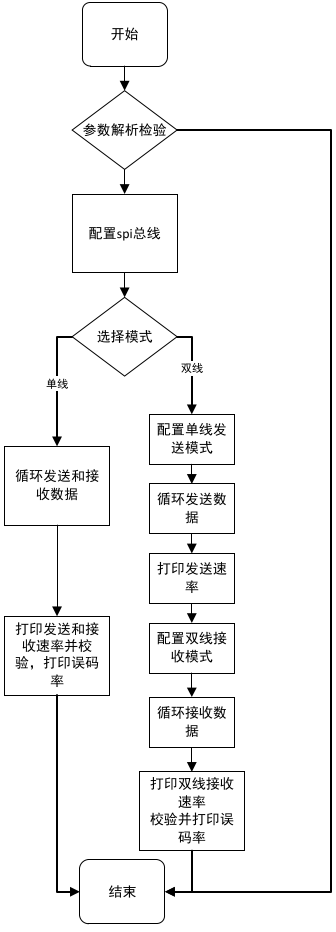

ARM端實現SPI Master功能,具體如下:

打開SPI設備節點,如:/dev/spidev1.0。

使用ioctl配置SPI總線,如SPI總線極性和相位、通信速率、數據字長度等。

選擇模式為單線模式或雙線模式。當SPI總線為雙線模式時,發送數據是單線模式,接收數據是雙線模式。

發送數據至SPI總線,并從SPI總線讀取數據。

打印發送和接收速率。

校驗讀寫數據,然后打印誤碼率。

FPGA端實現SPI Slave功能,具體如下:

FPGA將SPI Master發送的數據保存至BRAM。

SPI Master發起讀數據時,FPGA從BRAM讀取數據通過SPI總線傳輸給SPI Master。

當SPI總線為雙線模式,接收數據支持雙線模式,而發送數據不支持雙線模式。

圖?1?ARM端程序流程圖

圖?1?ARM端程序流程圖

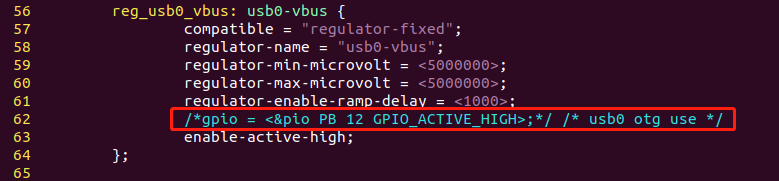

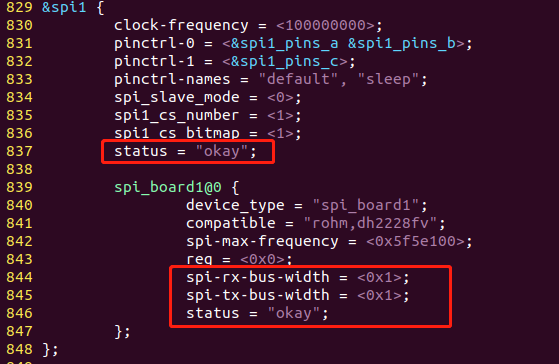

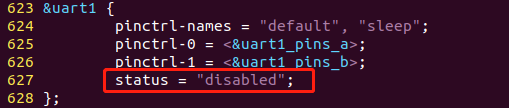

本案例使用的設備樹源文件為"driverdtsnandboard.dts"。該設備樹源文件基于LinuxSDK開發包內核源碼中的board.dts設備樹進行修改,具體修改內容如下。

屏蔽reg_usb0_vbus節點GPIO配置,避免引腳復用沖突。

關閉UART1節點,避免引腳復用沖突。

新增SPI總線和spidev驅動配置。生成/dev/spidev1.0節點,為應用層提供SPI的配置和讀寫數據的接口。

圖?2

圖?2

圖?3

圖?3

圖?4

圖?4

圖?5

圖?5

案例測試

硬件連接

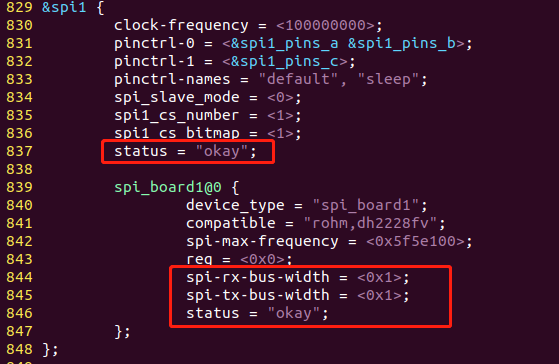

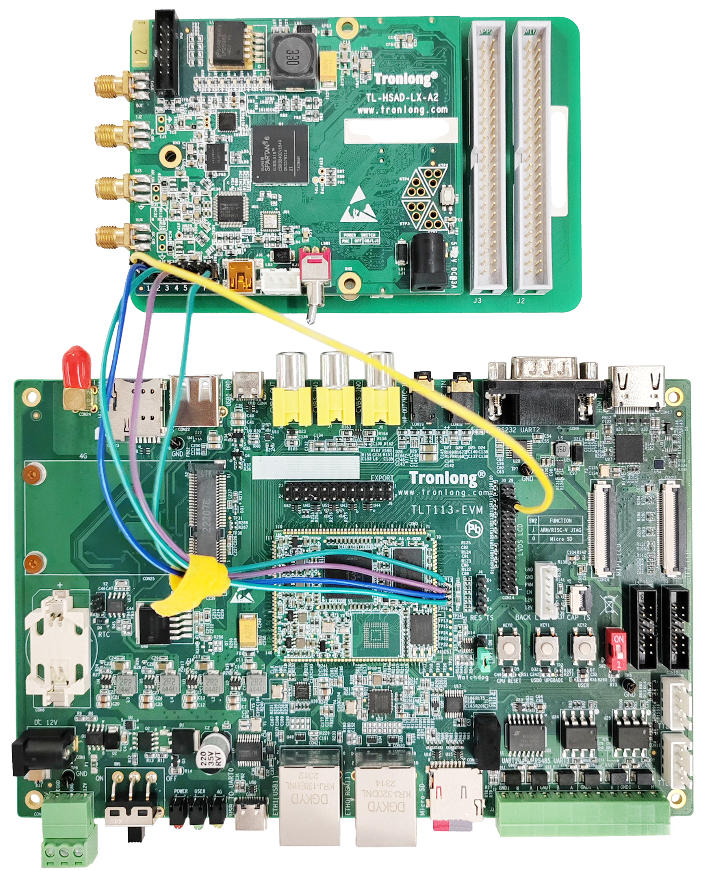

由于評估底板拓展接口未預留SPI總線引腳,因此需參考如下方法進行飛線連接,并且應盡可能使用短線連接。

圖?6

圖?6

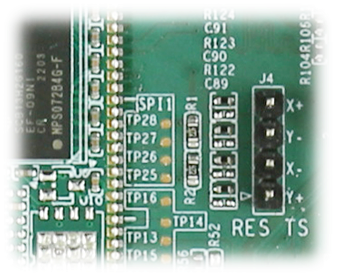

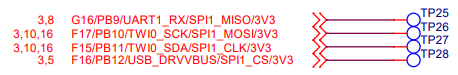

1.請根據評估底板絲印將SPI1的測試點TP25(SPI1 MISO)、TP26(SPI1 MOSI)、TP27(SPI1 CLK)、TP28(SPI1 CS)通過飛線引出。

圖?7

圖?7

圖?8

圖?8

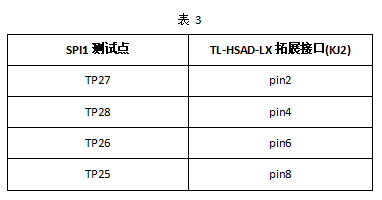

2.將飛線引出的引腳與創龍科技TL-HSAD-LX采集卡的拓展接口(KJ2)按照下表對應關系進行連接。

表?3

表?3

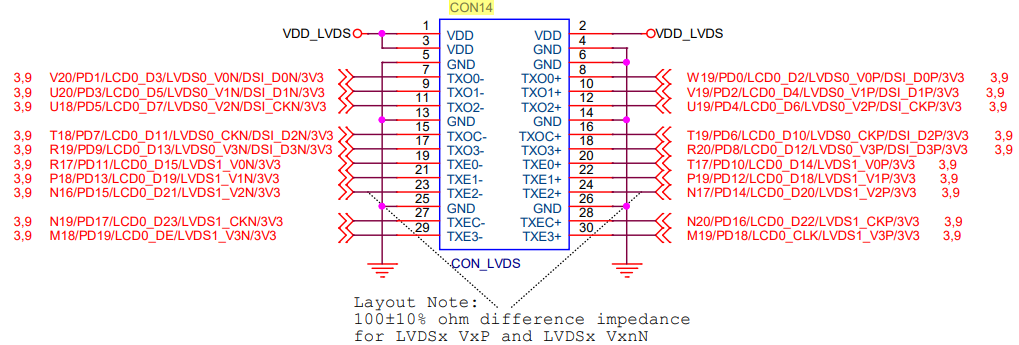

3.將評估底板LVDS LCD接口的第26引腳(GND)連接至TL-HSAD-LX采集卡拓展接口(KJ13)的第1引腳,進行共地連接。

圖?9

圖?9

案例測試

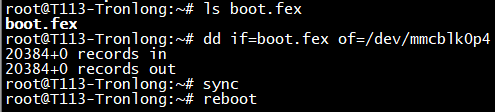

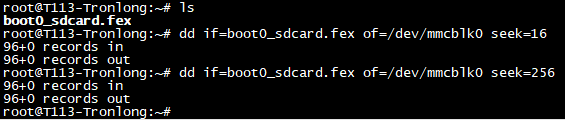

將案例bin目錄下的可執行文件spi_rw、"driverkernelnand"目錄下的boot.fex鏡像文件拷貝至評估板文件系統任意目錄下。

評估板上電啟動,在評估板文件系統boot.fex文件所在路徑下,執行如下命令替換原來的固件,并重啟評估板。

Target# dd if=boot.fex of=/dev/mmcblk0p4

Target# sync

Target# reboot

圖?10

圖?10

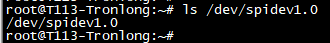

評估板重啟后,執行如下命令查看新生成的spidev設備節點。

Target# ls /dev/spidev1.0

圖?11

圖?11

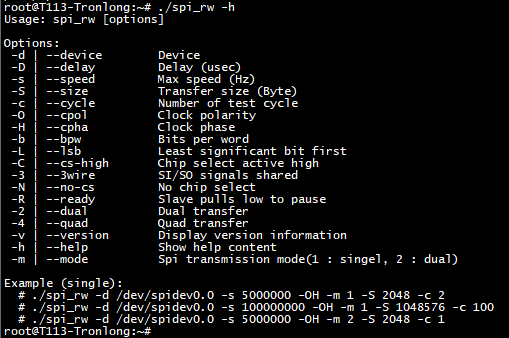

執行如下命令查詢程序命令參數。

Target# ./spi_rw -h

圖?12

圖?12

1.單線模式

TL-HSAD-LX采集卡上電啟動,加載運行案例"bram_spibin"目錄下的程序可執行文件,bram_spi程序支持SPI單線模式。

2.功能測試

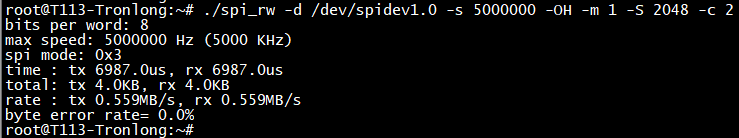

執行如下命令運行程序,ARM通過SPI總線寫入2KByte隨機數據至FPGA BRAM,然后讀出數據、進行數據校驗,同時打印SPI總線讀寫速率和誤碼率,如下圖所示。

Target# ./spi_rw -d /dev/spidev1.0 -s 5000000 -OH -m 1 -S 2048 -c 2

參數解析:

-d:設置設備節點;

-s:設置通信時鐘頻率(Hz);

-O:時鐘極性反轉(CPOL=1);

-H:下降沿采集數據(CPHA=1);

-m:選擇模式傳輸模式(1表示單線模式。2表示雙線模式);

-S:設置傳輸數據大小,單位為Byte;

-c:循環傳輸數據包的次數。

圖?13

圖?13

本次測試指定SPI總線通信時鐘頻率為5MHz,則SPI單線模式理論通信速率為:(5000000/1024/1024/8)MB/s ≈ 0.596MB/s。從上圖可知,本次實測SPI單線模式寫速率為0.559MB/s,讀速率為0.559MB/s,誤碼率為0.0%。

備注:由于本案例硬件采用飛線方式進行連接,因此若設置SPI總線通信時鐘頻率超過10MHz,可能會出現誤碼現象。

1.性能測試

執行如下命令運行程序,測試SPI單線模式的最高通信帶寬。ARM通過SPI總線寫入隨機數據至FPGA BRAM,然后讀出數據、進行數據校驗,循環100次,同時打印SPI總線讀寫速率和誤碼率,如下圖所示。

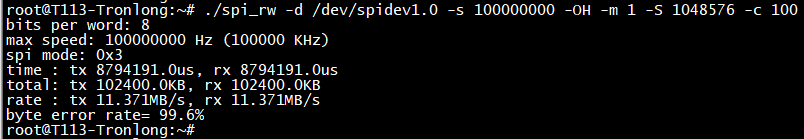

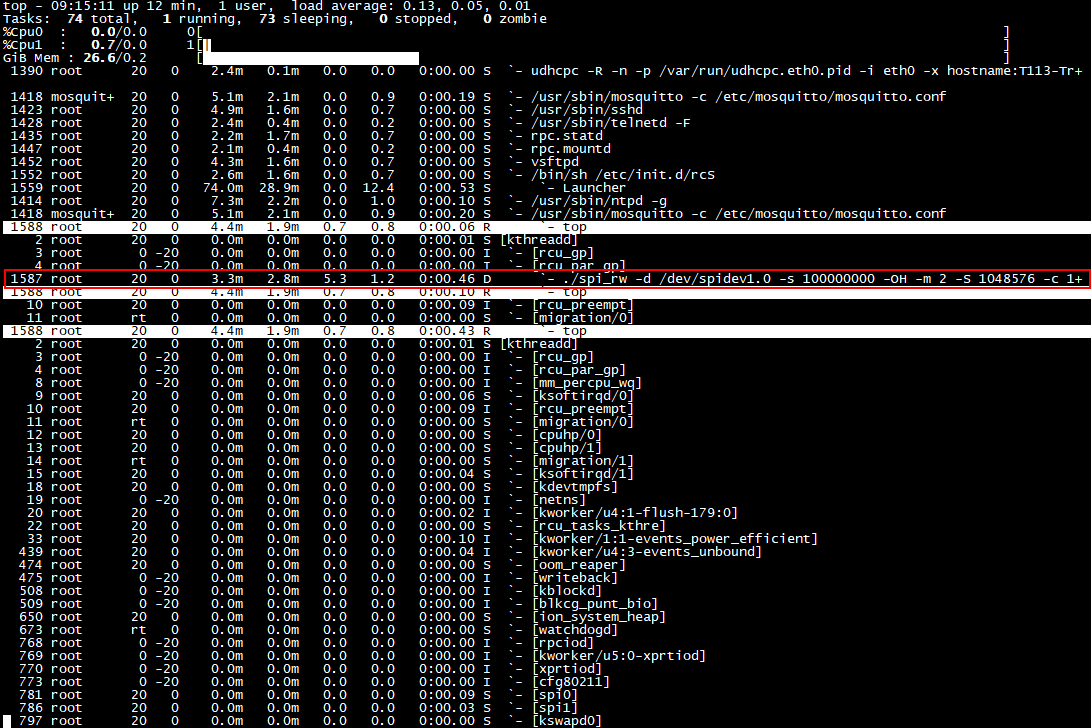

Target# ./spi_rw -d /dev/spidev1.0 -s 100000000 -OH -m 1 -S 1048576 -c 100

圖?14

圖?14

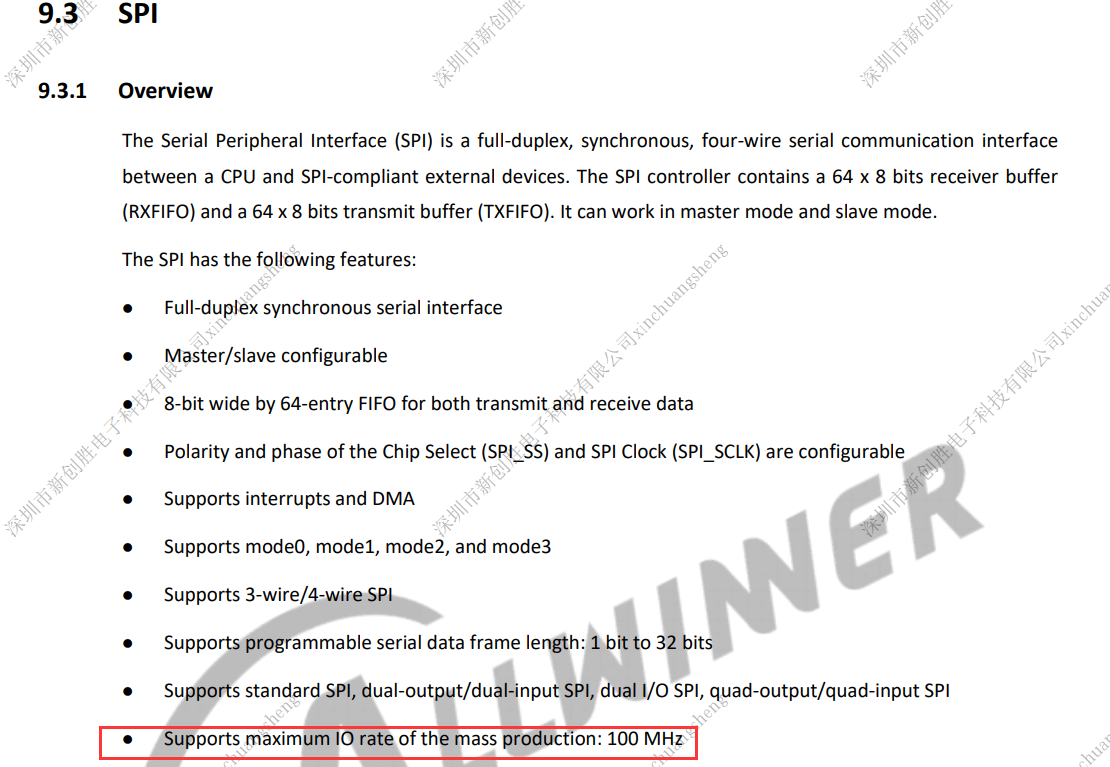

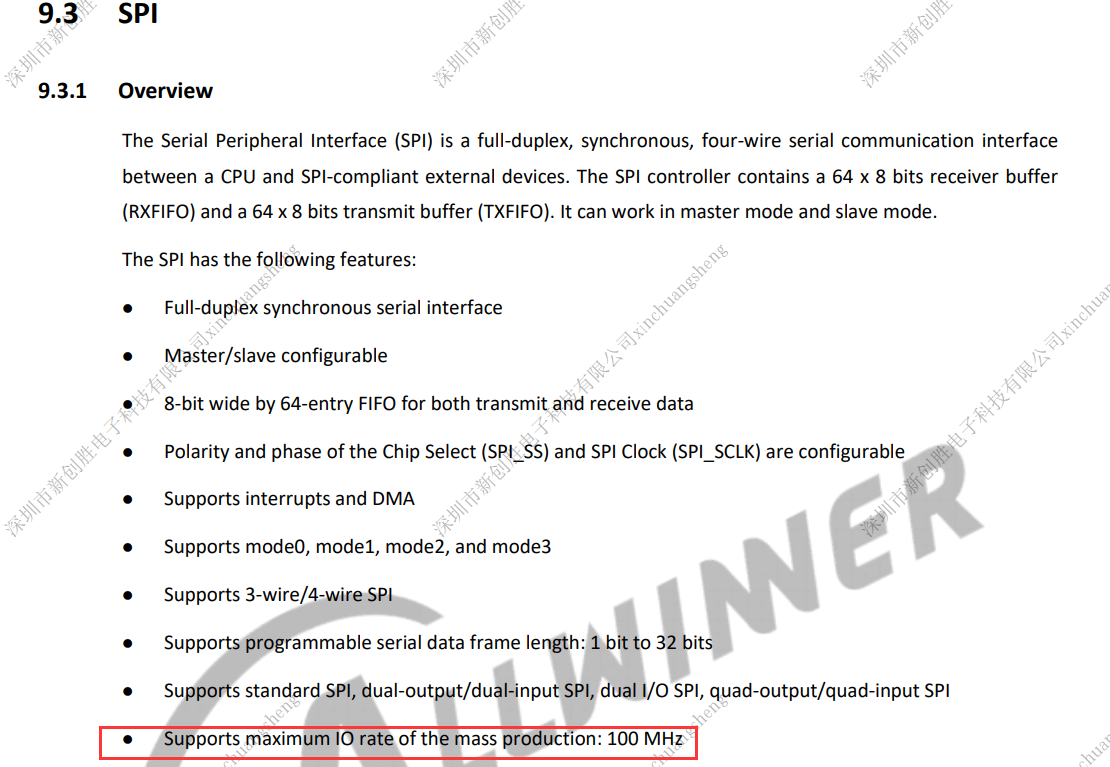

根據官方數據手冊(如下圖),SPI總線通信時鐘頻率理論值最大為100MHz。本次測試設置SPI總線通信時鐘頻率為最大值100MHz,則SPI單線模式理論速率為:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。從上圖可知,在100MHz下實測SPI單線模式寫速率為:11.371MB/s,SPI單線模式讀速率為:11.371MB/s。

備注:由于本次測試受限于飛線連接方式,因此在100MHz通信時鐘頻率下測得誤碼率過高,測試結果僅供參考。

圖?15

圖?15

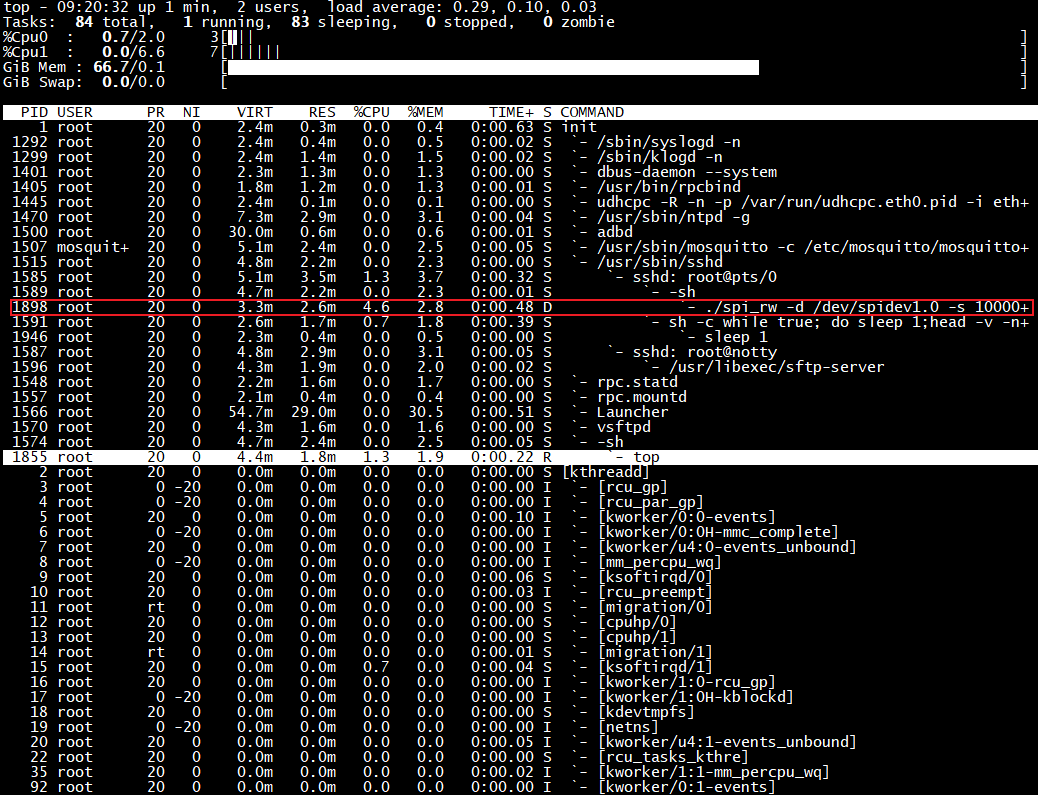

同時測得CPU的占用率約為4.6%,如下圖所示。

圖?16

圖?16

2.雙線模式

TL-HSAD-LX采集卡上電啟動,加載運行案例"bram_spi_dualbin"目錄下的程序可執行文件,bram_spi_dual程序支持SPI雙線模式。

3.功能測試

執行如下命令運行程序,ARM通過SPI總線寫入2KByte隨機數據至FPGA BRAM,然后讀出數據、進行數據校驗,同時打印SPI總線讀寫速率和誤碼率,如下圖所示。

Target# ./spi_rw -d /dev/spidev1.0 -s 5000000 -OH -m 2-S 2048 -c 1

參數解析:

-d:設置設備節點;

-s:設置通信時鐘頻率(Hz);

-O:時鐘極性反轉(CPOL=1);

-H:下降沿采集數據(CPHA=1);

-m:選擇模式傳輸模式(1表示單線模式。2表示雙線模式);

-S:設置傳輸數據大小,單位為Byte;

-c:循環傳輸數據包的次數。

圖?17

圖?17

本次測試指定SPI總線通信時鐘頻率為5MHz,則SPI雙線模式理論通信速率為:(5000000/1024/1024/4)MB/s ≈1.192MB/s。從上圖可知,本次實測SPI雙線模式寫速率為0.559MB/s,讀速率為1.104MB/s,誤碼率為0.0%。

備注:由于本案例硬件采用飛線方式進行連接,因此若設置SPI總線通信時鐘頻率超過10MHz,可能會出現誤碼現象。

4.性能測試

執行如下命令運行程序,測試SPI雙線模式的最高通信帶寬。ARM通過SPI總線寫入隨機數據至FPGA BRAM,然后讀出數據、進行數據校驗,循環100次,同時打印SPI總線讀寫速率和誤碼率,如下圖所示。

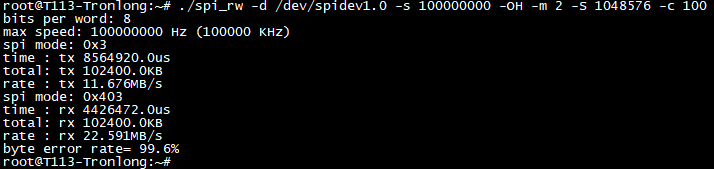

Target# ./spi_rw -d /dev/spidev1.0 -s 100000000 -OH -m 2-S 1048576 -c 100

圖?18

圖?18

根據官方數據手冊(如下圖),SPI總線通信時鐘頻率理論值最大為100MHz。本次測試設置SPI總線通信時鐘頻率為最大值100MHz,則SPI雙線模式理論速率為:(100000000/1024/1024/4)MB/s ≈23.84MB/s。從上圖可知,在100MHz下實測SPI雙線模式寫速率為:11.676MB/s,SPI雙線模式讀速率為:22.591MB/s。

備注:由于本次測試受限于飛線連接方式,因此在100MHz通信時鐘頻率下測得誤碼率過高,測試結果僅供參考。

圖?19

圖?19

同時測得CPU的占用率約為5.3%,如下圖所示。

圖?20

圖?20

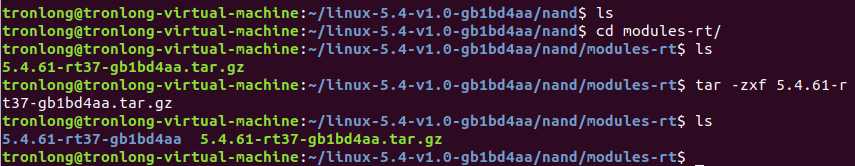

案例編譯

ARM端設備樹編譯

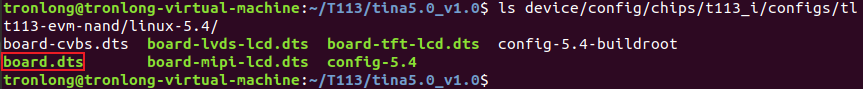

將案例"driverdtsnand"目錄下board.dts設備樹拷貝至LinuxSDK開發包內核源碼"device/config/chips/t113_i/configs/tlt113-evm-nand/linux-5.4/"目錄下。

圖?21

圖?21

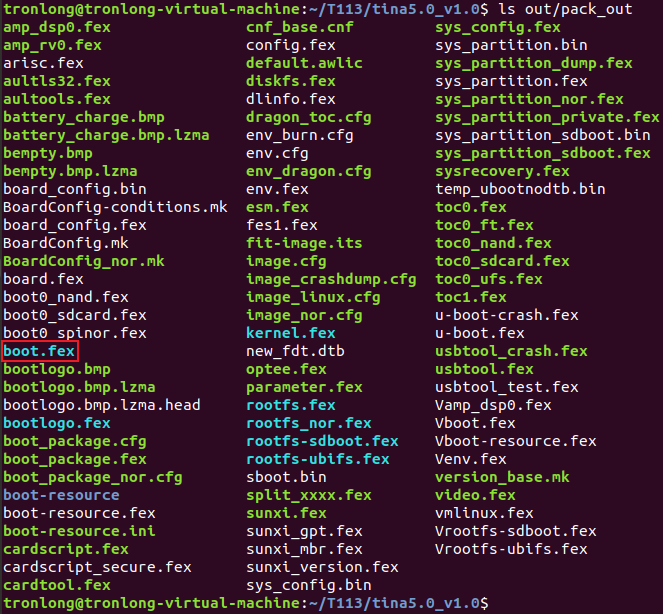

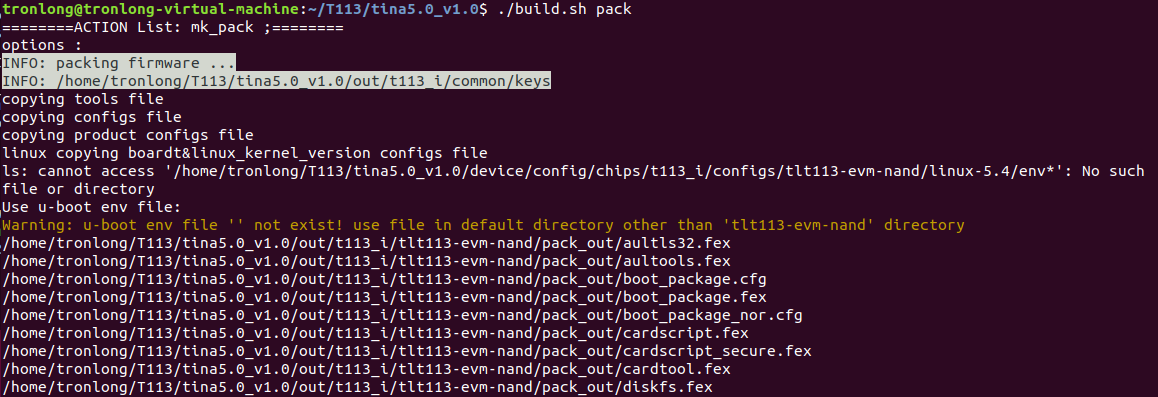

請按照《Linux系統使用手冊》文檔編譯Linux內核、設備樹等,并重新執行"./build.sh pack"命令,將會在"tools/pack/out/"目錄下生成新的boot.fex鏡像文件。將其拷貝至評估板文件系統進行固化,評估板重啟后將會加載新的設備樹文件,生成"/dev/spidev1.0"設備節點。

圖?22

圖?22

ARM端程序編譯

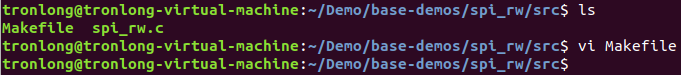

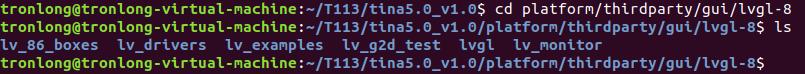

將案例src源碼目錄拷貝至Ubuntu工作目錄下,進入源碼目錄,執行如下命令修改Makefile配置文件,LICHEE_DIR路徑修改為LinuxSDK開發包實際路徑,將LICHEE_OUT_SYS路徑修改為buildroot實際路徑。

Host# vi Makefile

圖?23

圖?23

修改內容如下:

LICHEE_DIR := /home/tronlong/T113/tina5.0_v1.0 //指定LinuxSDK包安裝路徑

LICHEE_OUT_SYS = $(LICHEE_DIR)/out/t113_i/tlt113-evm-nand/buildroot/buildroot //指定buildroot實際路徑

備注:若為eMMC配置評估板,請將路徑"tlt113-evm-nand"修改為"tlt113-evm-emmc"。

圖?24

圖?24

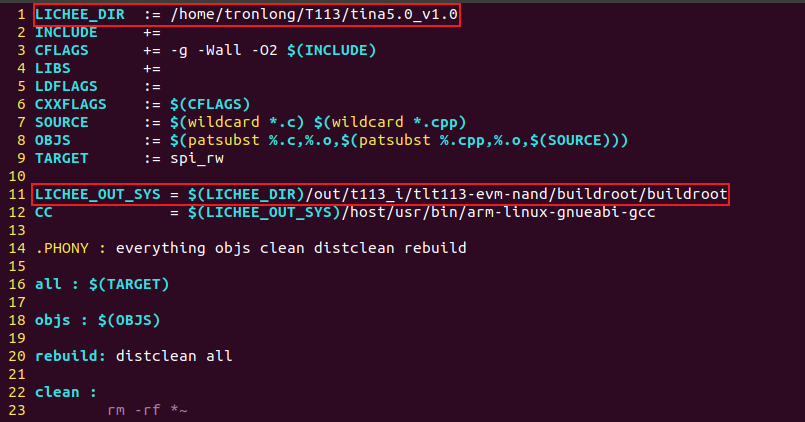

修改完成,繼續執行如下命令,使用LinuxSDK開發包目錄下的編譯器進行案例編譯,編譯完成將會在同一個目錄下生成可執行程序。

Host# make clean

Host# make

圖?25

圖?25

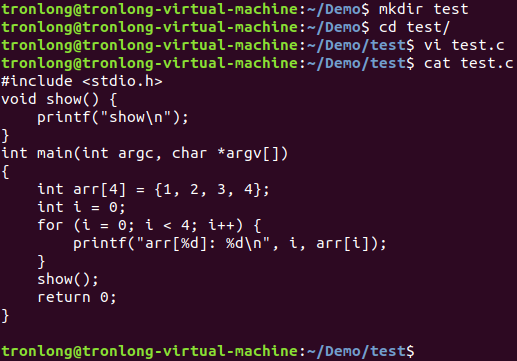

ARM端程序關鍵代碼

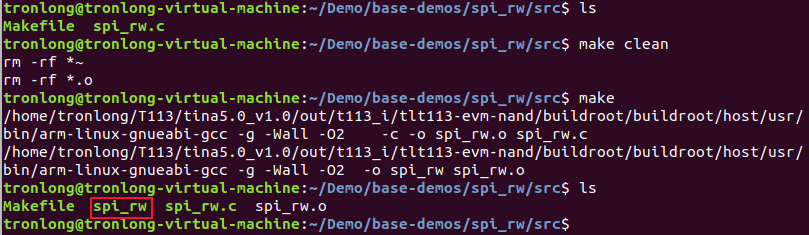

1.打開SPI設備,分配讀寫緩沖區。

圖?26

圖?26

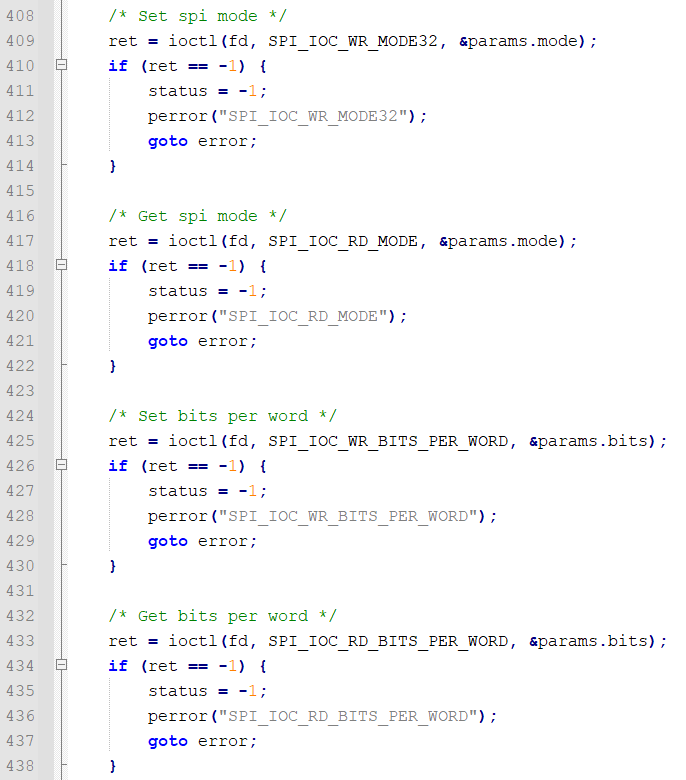

2.配置SPI總線。

圖?27

圖?27

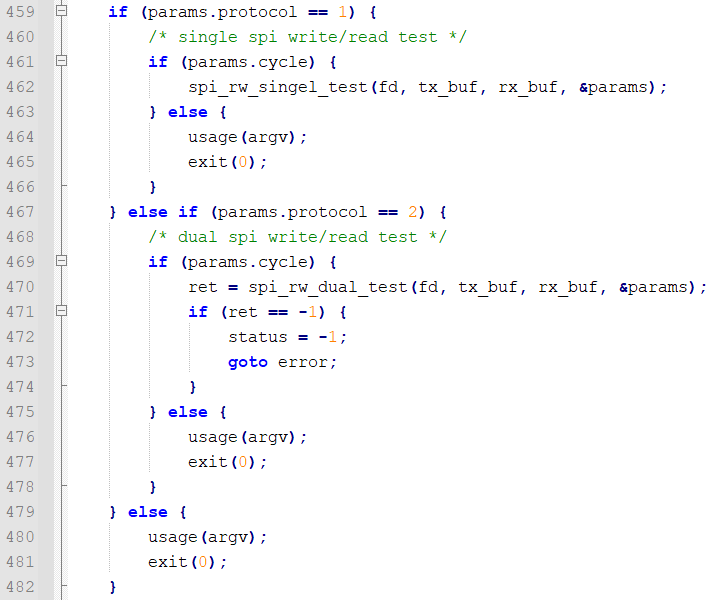

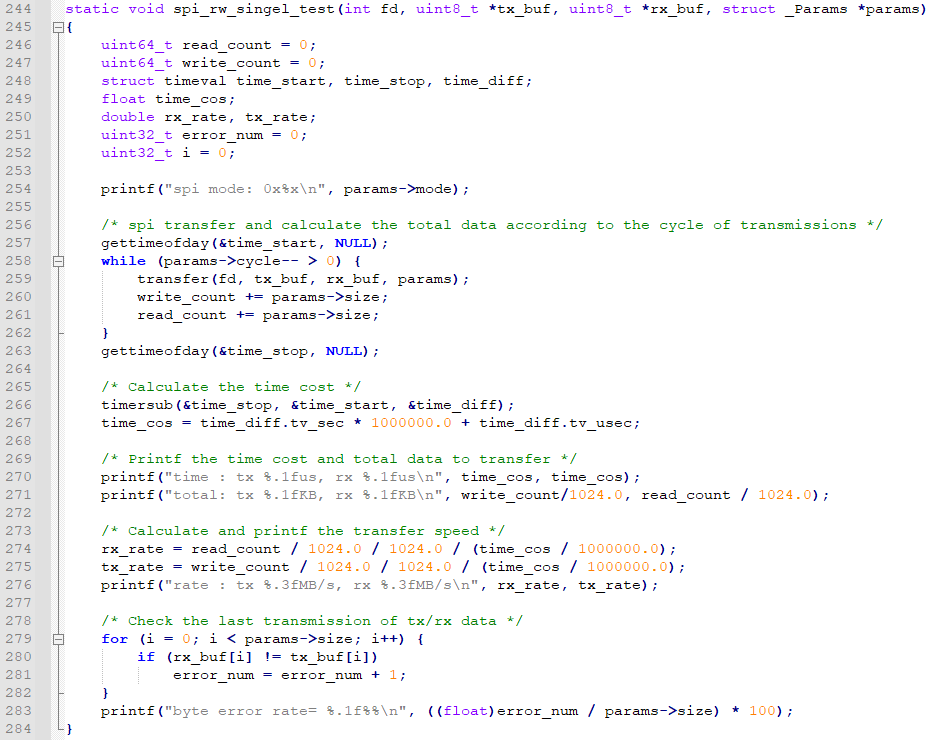

3.SPI讀寫速率測試功能實現。

圖?28

圖?28

4.單線模式。

圖?29

圖?29

審核編輯 黃宇

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638505 -

Cortex

+關注

關注

2文章

220瀏覽量

48965 -

開發板

+關注

關注

26文章

6372瀏覽量

120104

發布評論請先 登錄

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—Linux系統使用手冊(三)

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—Linux系統使用手冊(二)

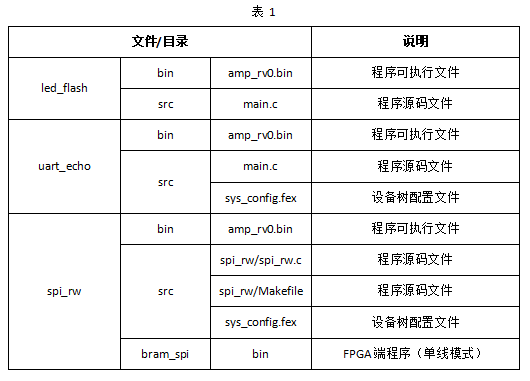

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—ARM + DSP、RISC-V核間通信開發案例

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—RISC-V案例開發手冊(上)

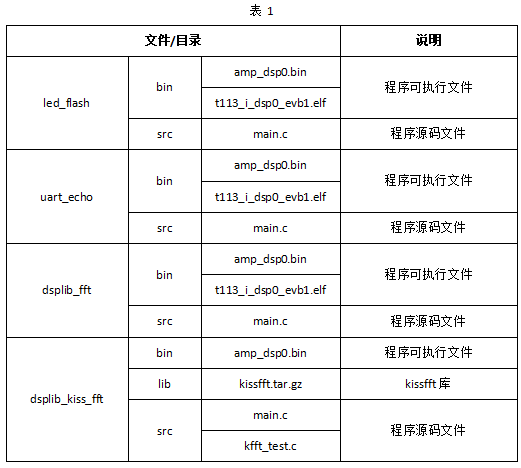

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—DSP案例開發手冊

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—GDB程序調試方法說明

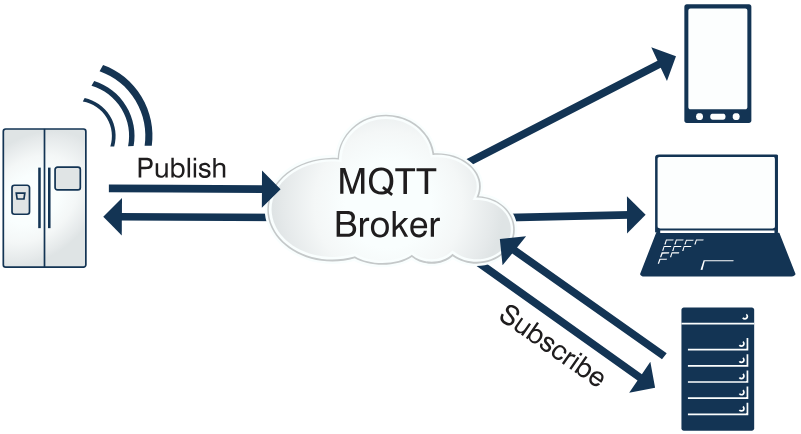

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—MQTT通信協議案例

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—Linux-RT應用開發案例

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—ARM + FPGA通信案例

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—ARM + FPGA通信案例

評論