SGMII簡介

SGMII(Serial Gigabit Media Independent Interface) 通過將網(wǎng)絡(luò)數(shù)據(jù)與控制接口進行轉(zhuǎn)換,將復(fù)雜的GMII接口轉(zhuǎn)換為一對serdes接口,減少了PHY與MAC之間的接口數(shù)量。

SGMII IP遵循《Serial-GMII Specification V1.7》與《IEEE 802.3-2008》規(guī)范。

SGMII IP特性

支持10/100/1000Mb/s GMII接口

支持自協(xié)商同步

支持MDIO控制接口

支持半雙工與全雙工模式

支持獨立的SERDES調(diào)試接口

支持運行狀態(tài)與自協(xié)商結(jié)果輸出

SGMII IP設(shè)計

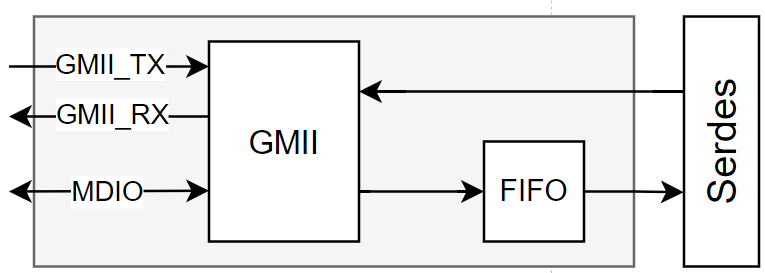

SGMII IP包含了《Serial-GMII Specification V1.7》定義的PCS功能部分與PMA部分。

SERDES實現(xiàn)了PCS部分的8B/10B編解碼功能的同時,也實現(xiàn)了PMA部分的數(shù)據(jù)時鐘恢復(fù)、數(shù)據(jù)串行與數(shù)據(jù)接串功能。

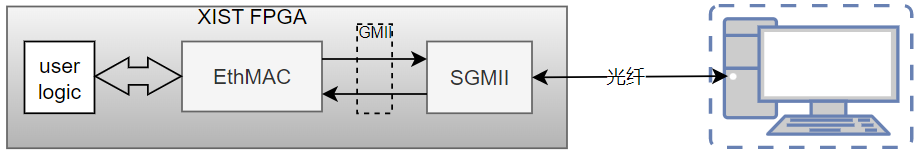

圖1 SGMII系統(tǒng)框圖

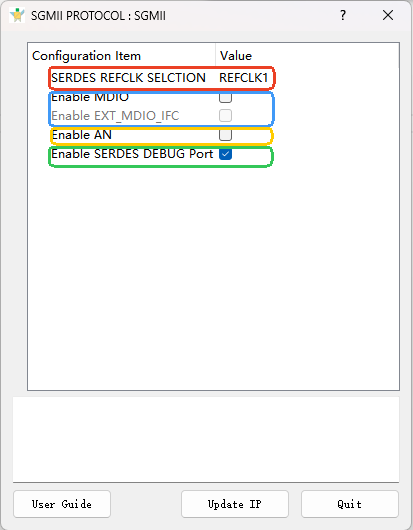

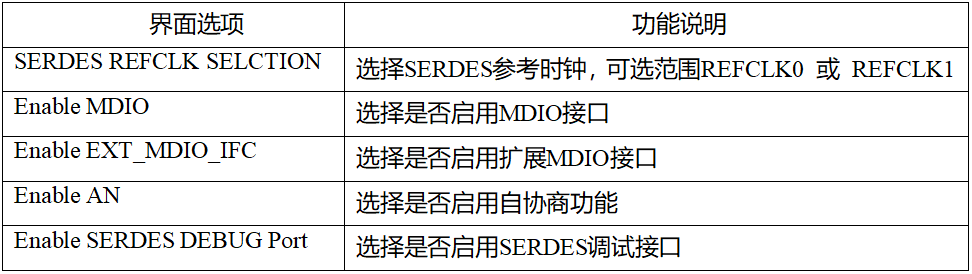

SGMII IP使用

圖2 IP界面配置

資源占用情況

典型應(yīng)用示例

圖3展示了一種SGMII的典型應(yīng)用場景,借助EthMAC IP將用戶數(shù)據(jù)打包為網(wǎng)絡(luò)數(shù)據(jù)包,通過光纖將數(shù)據(jù)傳遞到電腦端。

圖3 SGMII典型應(yīng)用

獲取技術(shù)文檔與demo

技術(shù)文檔獲取:SGMII IP已發(fā)布,用戶可以在HQFPGA IP Manage中打開SGMII IP界面查看用戶指南,或訪問智多晶官網(wǎng)下載SGMII IP用戶指南。

-

接口

+關(guān)注

關(guān)注

33文章

9562瀏覽量

157421 -

IP

+關(guān)注

關(guān)注

5文章

1875瀏覽量

156298 -

時鐘

+關(guān)注

關(guān)注

11文章

1995瀏覽量

135156

原文標題:“芯”技術(shù)分享 | 智多晶 SGMII IP介紹

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

GMII、SGMII和SerDes的差異總結(jié)

智多晶XSTC_8B10B IP介紹

智多晶FIFO_Generator IP介紹

智多晶eSPI_Slave IP介紹

SGMII模式下在接收路徑和發(fā)送路徑中使用此IP應(yīng)該注意什么?

國產(chǎn)智多晶FPGA介紹及應(yīng)用

vcs-mx 201306模擬器無法編譯sgmii網(wǎng)橋IP的原因?

國產(chǎn)FPGA智多晶叼

88e1111 RGMII to SGMII 模式配置不成功,求助!

多晶硅生產(chǎn)流程是什么_單晶硅與多晶硅的區(qū)別

智多晶DDR Controller介紹

深入解讀智多晶FIR IP

智多晶LPC_Controller IP介紹

智多晶MCU硬核IP全面升級|CM3和STAR新特性介紹

智多晶SGMII IP介紹

智多晶SGMII IP介紹

評論