電子發燒友網報道(文 / 吳子鵬)日前,PCI-SIG 正式公布 PCI Express 8.0(PCIe 8.0)規范的開發計劃,目標在 2028 年向會員發布。根據公布的規范,PCIe 8.0 將使速率在 PCIe 7.0 的基礎上翻倍至 256.0 GT/s,通過 x16 配置實現 1TB/s 的雙向帶寬。

從 PCI-SIG 目前公布的細節來看,PCIe 8.0 首先實現了速度的提升,新的標準會開發協議增強功能以提高帶寬。不過速度提升之后會帶來一系列技術挑戰,比如信號完整性與抗干擾能力方面的問題。隨著速率從 PCIe 7.0 的 128 GT/s 翻倍至 256 GT/s,信號在銅纜或 PCB 中傳輸時的衰減、串擾(相鄰信號線的電磁干擾)、抖動(信號 timing 偏差)會進一步惡化。同時,外部電磁干擾(EMI)也會加劇,這就要求連接器、線纜和 PCB 設計具備更強的抗干擾能力。另外,連接器的插入損耗、回波損耗(信號反射)會隨頻率升高而惡化,因此需要重新設計接觸件結構并采用低損耗材料。為此,PCI-SIG 在 PCIe 8.0 規范目標中提到要評估新型連接器技術。

高速率傳輸還需要 PCIe 8.0 平衡延遲與 FEC 之間的矛盾。在高速傳輸過程中,信號錯誤率會隨速率提升而上升,這必須依賴前向糾錯(FEC)技術來修正錯誤。但 FEC 需要額外的計算和數據冗余(如增加校驗位),不可避免地會增加延遲。所以,挑戰在于設計 “輕量級 FEC 算法”,在保證糾錯能力的同時,最小化計算開銷和冗余數據量,從而平衡可靠性與低延遲。基于此,PCI-SIG 會確認相關技術可滿足延遲和前向糾錯(FEC)目標。

PCIe 的核心優勢之一是向后兼容,然而在高速率下,兼容設計的難度大幅增加。例如,物理層需支持多速率自適應,這就要求電路同時兼容不同信號特性,進而增加了均衡器、時鐘恢復電路的設計復雜度;協議層需兼容前代的流量控制、事務處理機制,同時引入新的增強功能(如更高效率的帶寬利用),這需要避免新功能與舊協議沖突而導致邏輯設計冗余。不過,PCI-SIG 的目標是保持 PCIe 8.0 與歷代 PCIe 技術的向后兼容。

PCIe 8.0 還必須考慮散熱方面的影響,功耗上升會直接導致芯片(如 PCIe 控制器、交換機)和鏈路組件(連接器、線纜)的發熱量增加,而高溫會進一步惡化信號完整性并縮短器件壽命。在芯片級,需要集成更高效的熱管理模塊;在系統級,需優化散熱方案(如液冷、高密度散熱鰭片),尤其在超大規模數據中心等密集部署場景中,散熱成本可能會顯著上升。為此,PCI-SIG 也會確保達成可靠性指標。

綜上,PCIe 8.0 的速度躍升本質上是對信號物理特性、功耗控制、兼容性設計的全面挑戰,需要從材料、電路、協議、測試等多維度突破現有技術瓶頸,才能實現高帶寬、低延遲、高可靠的目標。

PCIe 8.0規范發布之后,有望為人工智能 / 機器學習、高速網絡、邊緣計算和量子計算等新興應用提供可擴展的互連解決方案;并將支持汽車、超大規模數據中心、高性能計算(HPC)以及軍事 / 航空航天等數據密集型市場。

發布評論請先 登錄

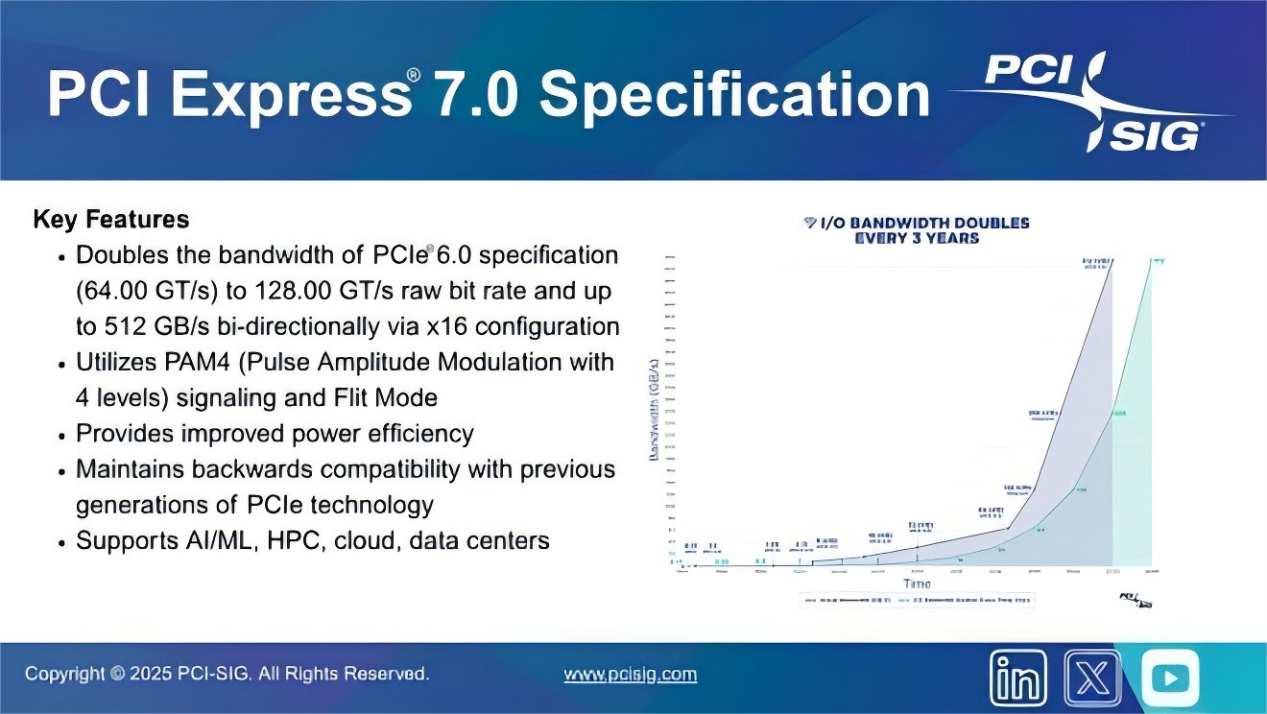

PCIe 7.0發布:16通道雙向512GB/s,擁抱光纖未來

【PCIe 6.0 連載 · 上篇】64GT/s 時代來臨:AI與算力爆發下的高速互聯新基石

深入剖析Cypress S25FL128S/S25FL256S:高性能SPI閃存的卓越之選

簡單認識Metorage 1TB MicroSD工業級存儲卡

PCIe 5.0 8TB SSD挺進消費級市場

帶寬7.2Tb/s!海思光電推出HI-ONE硅光引擎

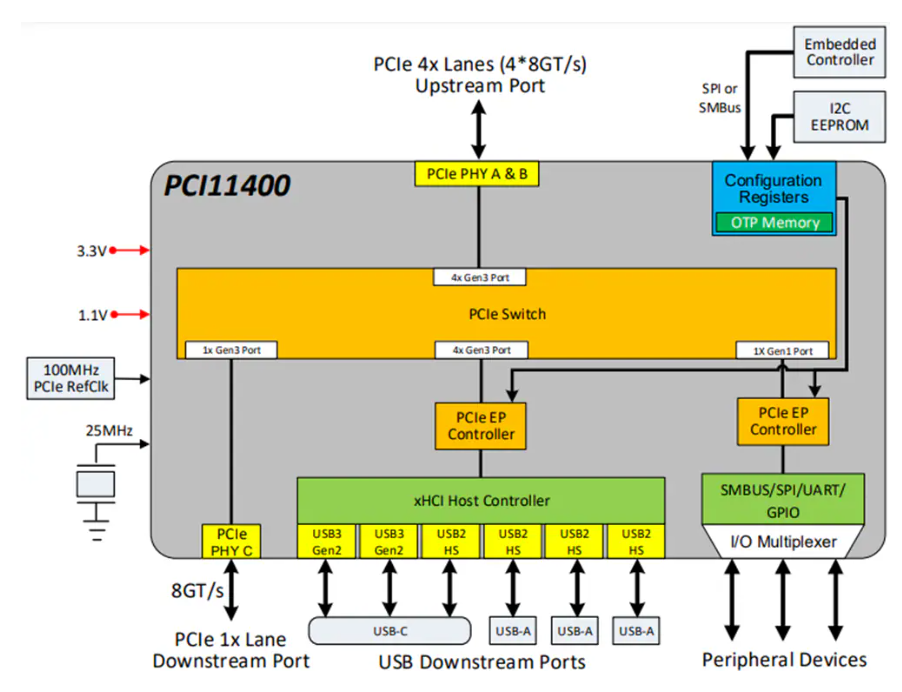

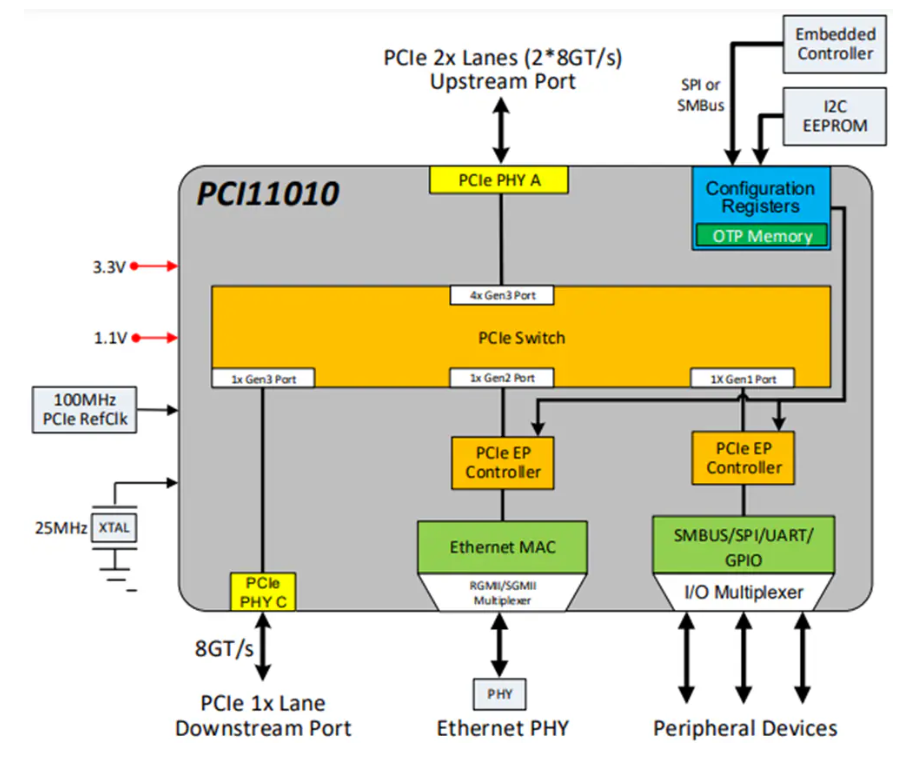

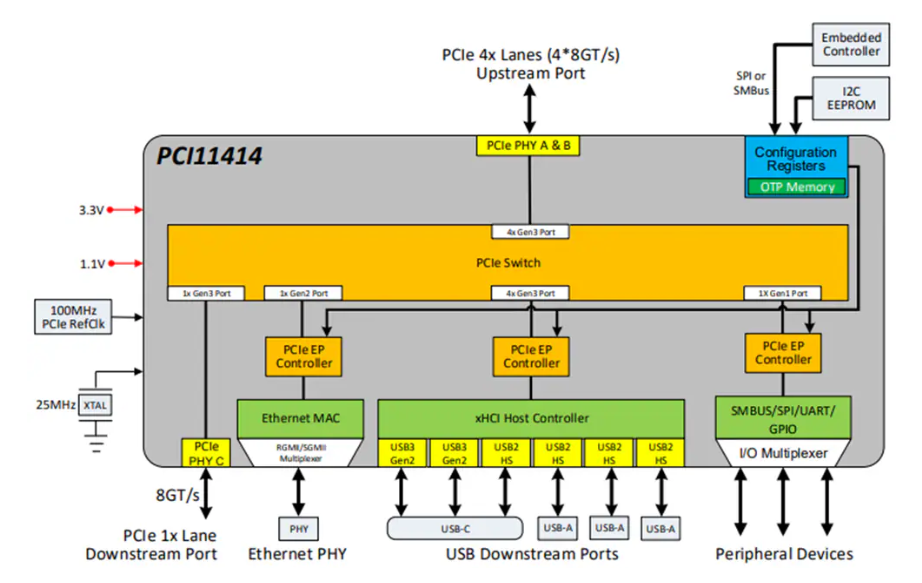

?Microchip PCI11400 PCIe交換機技術解析與應用指南

全球首款HBM4量產:2.5TB/s帶寬超越JEDEC標準,AI存儲邁入新紀元

PCIe 6.0 SSD主控芯片狂飆!PCIe 7.0規范到來!

PCIe 8.0 規范公布:1TB/s 帶寬、256GT/s 速率

PCIe 8.0 規范公布:1TB/s 帶寬、256GT/s 速率

評論