電子發(fā)燒友網(wǎng)綜合報(bào)道,近日,PCI-SIG宣布PCI Express 8.0規(guī)范的Version 0.3 版本已獲得工作組批準(zhǔn),現(xiàn)已向PCI-SIG 會(huì)員開(kāi)放。這標(biāo)志著PCIe 8.0 規(guī)范完成了第一版審查草案,該規(guī)范正按照2028年正式推出的預(yù)設(shè)開(kāi)發(fā)進(jìn)程推進(jìn)。按照 PCIe 規(guī)范此前的開(kāi)發(fā)慣例,PCIe 8.0 此后還將經(jīng)歷 Version 0.5 / 0.7 / 0.9 等階段方能走到最終的 1.0 版本。

PCI Express 8.0 規(guī)范開(kāi)發(fā)計(jì)劃于今年8月公布,該標(biāo)準(zhǔn)將繼續(xù)采用PAM4脈沖幅度調(diào)制信號(hào)技術(shù),并在PCIe 7.0的基礎(chǔ)上實(shí)現(xiàn)傳輸速率翻倍,達(dá)到每通道256GT/s。在×16 配置下雙向傳輸帶寬可達(dá) 1TB/s,旨在滿足未來(lái)高性能計(jì)算、AI對(duì)高速互聯(lián)的需求。

PCIe規(guī)范自2001年正式發(fā)布以來(lái),經(jīng)歷了多個(gè)版本的演進(jìn),始終圍繞 “更高帶寬、更低延遲、更強(qiáng)擴(kuò)展性” 展開(kāi)。

2017年P(guān)CIe 4.0推出,速率為 16GT/s。它實(shí)現(xiàn)了每通道 PHY 集成,功耗降低 30%,廣泛應(yīng)用于 NVMe SSD、AI 加速卡等。2019 年P(guān)CIe 5.0發(fā)布,速度提升到 32GT/s。此版本引入了前向糾錯(cuò)(FEC)、FLIT 調(diào)度算法等技術(shù),支持 CXL(Compute Express Link)協(xié)議落地,可用于高性能計(jì)算、AI 訓(xùn)練集群等場(chǎng)景。

PCI-SIG組織于2022年1月發(fā)布PCIe 6.0標(biāo)準(zhǔn)。其雙向帶寬達(dá)256 GB/s(x16通道),較PCIe 5.0實(shí)現(xiàn)翻倍,同時(shí)采用四級(jí)PAM4信號(hào)調(diào)制與輕量級(jí)前向糾錯(cuò)技術(shù),有效提升傳輸速率至64 GT/s并降低誤碼率 。該標(biāo)準(zhǔn)引入固定尺寸FLIT流量控制單元,支持動(dòng)態(tài)帶寬調(diào)節(jié)與完整數(shù)據(jù)加密功能,兼具高效傳輸與物理安全性,且向下兼容前代協(xié)議 。

核心技術(shù)革新包括通過(guò)PAM4信號(hào)調(diào)制實(shí)現(xiàn)單位間隔傳輸4級(jí)信號(hào);采用1b1b編碼及新型FLIT協(xié)議提升鏈路利用率;運(yùn)用循環(huán)冗余校驗(yàn)與格雷編碼增強(qiáng)可靠性 。電源管理方面引入L0p動(dòng)態(tài)狀態(tài)調(diào)節(jié)功能,可降低非活動(dòng)通道功耗并優(yōu)化能效比。PCIe 6.0 SSD主控預(yù)計(jì)在2028年開(kāi)始量產(chǎn),部分企業(yè)已推出基于PCIe 6.0的測(cè)試產(chǎn)品或主控芯片。

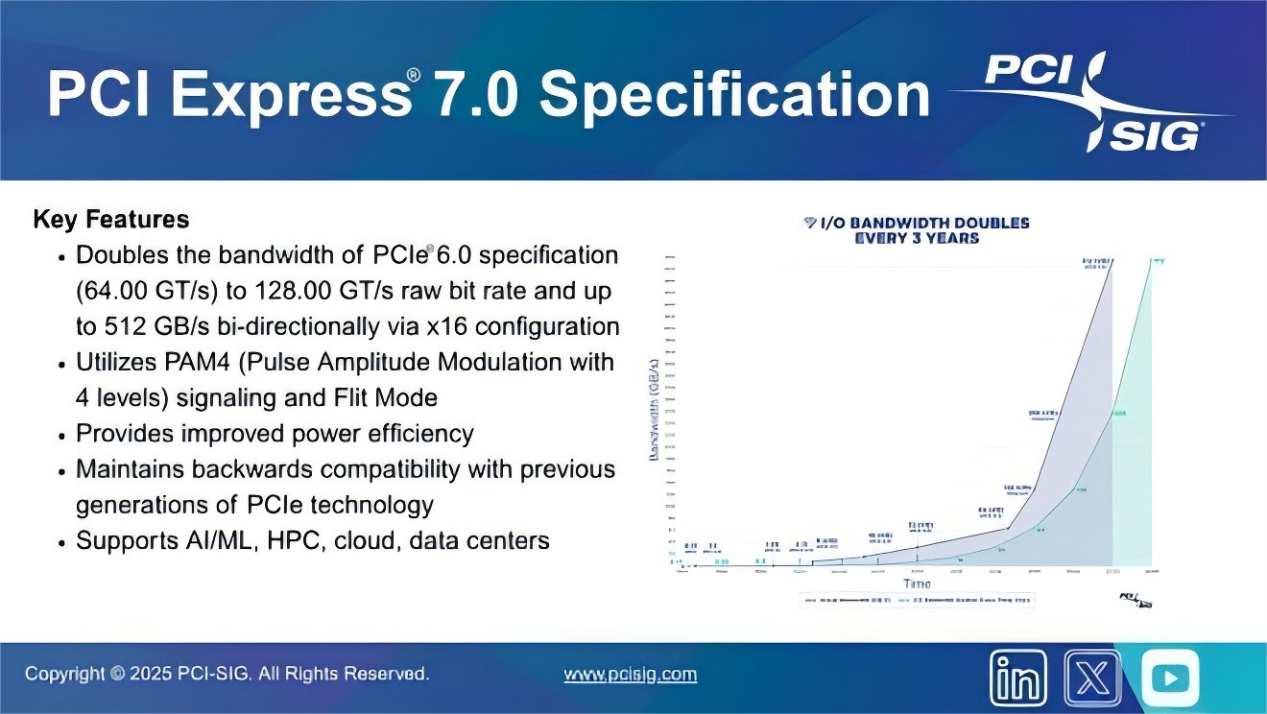

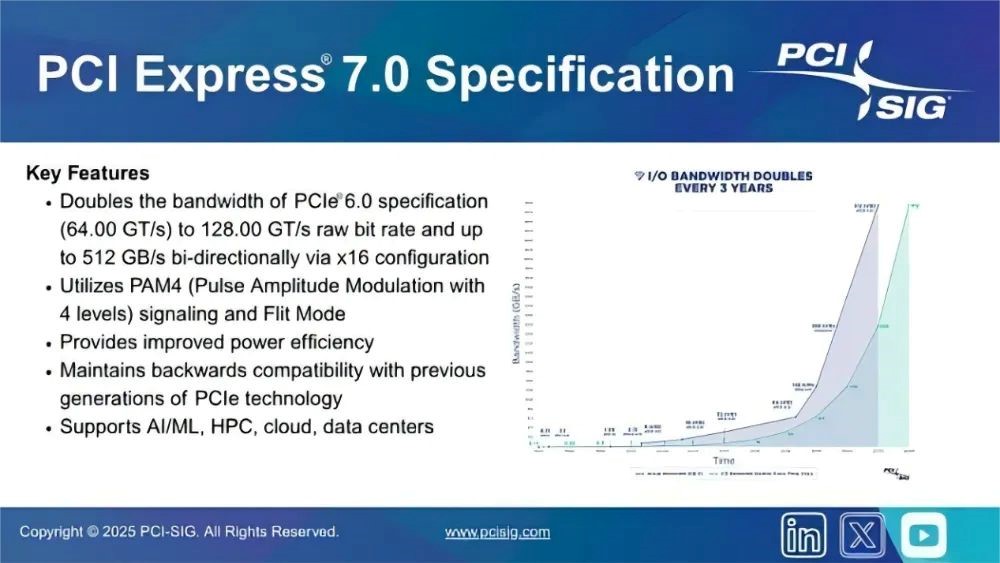

PCIe 7.0規(guī)范于2025年6月12日由PCI-SIG正式發(fā)布,最高傳輸速率達(dá)128GT/s,為下一代AI、機(jī)器學(xué)習(xí)、800以太網(wǎng)、云計(jì)算和量子計(jì)算等數(shù)據(jù)驅(qū)動(dòng)型應(yīng)用提供了強(qiáng)大的支持。PCIe 7.0規(guī)范的主要特點(diǎn)包括:提供128.0GT/s的原始比特率,通過(guò)x16配置可實(shí)現(xiàn)高達(dá)512GB/s的雙向帶寬。采用PAM4(4級(jí)脈沖幅度調(diào)制)信號(hào)和基于Flit的編碼技術(shù)。提高了能效比。與以往的PCIe技術(shù)保持向后兼容性。預(yù)計(jì)2027年完成預(yù)測(cè)試,2028年發(fā)布首批集成商名單。

市場(chǎng)進(jìn)程方面,據(jù)CFM閃存市場(chǎng)數(shù)據(jù)統(tǒng)計(jì),PCIe 4.0在2023年已占據(jù)消費(fèi)級(jí)SSD市場(chǎng)55%的出貨量,2025年將攀升至71%,持續(xù)鞏固主流地位。另外,有數(shù)據(jù)顯示,企業(yè)級(jí)SSD需求擴(kuò)張,PCIe 5.0 SSD的高效能需求將進(jìn)一步推升產(chǎn)業(yè)成長(zhǎng)。2025年企業(yè)級(jí)SSD市場(chǎng)將年增15%,PCIe 5.0 SSD滲透率將從2024年的9%提升至2026年的61%。根據(jù) IDC 測(cè)算,2025 年 PCIe 5.0 在數(shù)據(jù)中心市場(chǎng)的滲透率預(yù)計(jì)將達(dá)到 78%。隨著 AI 技術(shù)發(fā)展,數(shù)據(jù)中心對(duì)高速數(shù)據(jù)傳輸和存儲(chǔ)需求大增,PCIe 5.0 因高帶寬、低延遲等特性,正逐漸成為數(shù)據(jù)中心的主流選擇。

發(fā)布評(píng)論請(qǐng)先 登錄

PCIe 7.0發(fā)布:16通道雙向512GB/s,擁抱光纖未來(lái)

pcie總線授時(shí)時(shí)碼卡#時(shí)統(tǒng)卡 #時(shí)碼卡 #pcie總線授時(shí) #cpci授時(shí)卡

CPCI或pcie總線時(shí)統(tǒng)卡# 授時(shí)卡# 時(shí)統(tǒng)卡# pcie總線授時(shí)

總線授時(shí)卡優(yōu)勢(shì)解讀 #雙模pcie授時(shí)卡 #北斗pcie授時(shí)卡 #pcie授時(shí)板卡 #總線 #同步天下

開(kāi)發(fā)者必備,10 分鐘搞定 RK3588 PCIE 拆分!

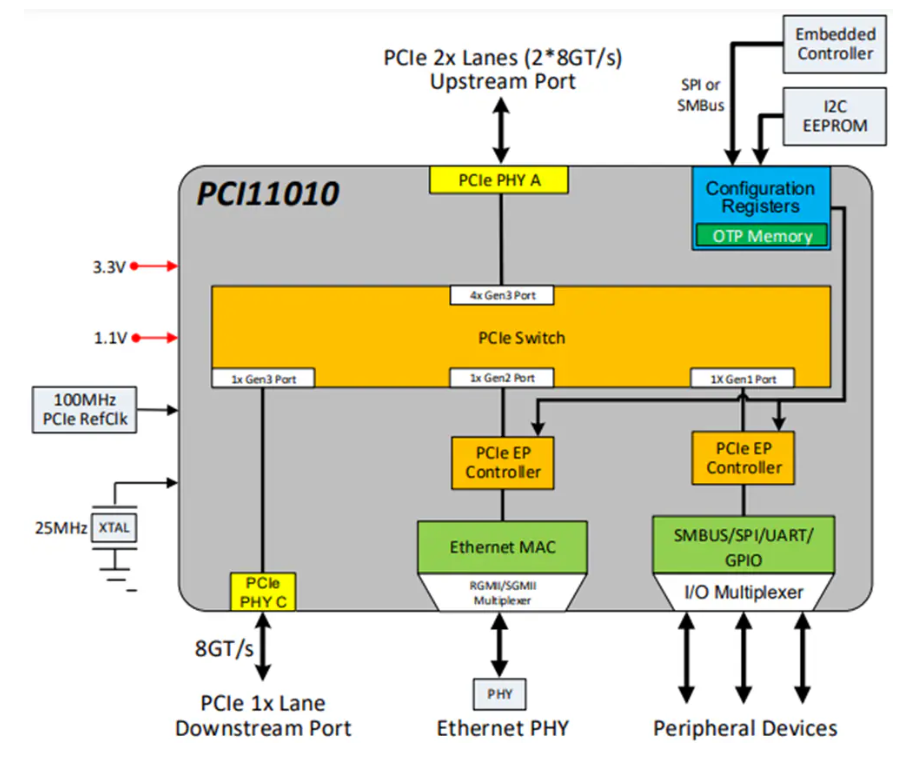

?PCI11010 PCIe交換機(jī)技術(shù)解析與應(yīng)用設(shè)計(jì)指南

PCIe 6.0 SSD主控芯片狂飆!PCIe 7.0規(guī)范到來(lái)!

QNX QOS 8.0助力構(gòu)建復(fù)雜任務(wù)關(guān)鍵型嵌入式應(yīng)用

PCIe 8.0 規(guī)范公布:1TB/s 帶寬、256GT/s 速率

0.1 至 8.0 GHz SP3T 開(kāi)關(guān) skyworksinc

PCIe 4.0/5.0仍是主流!三家SSD企業(yè)搶灘高性能存儲(chǔ)市場(chǎng),新品相繼亮相

PCIe 8.0規(guī)范開(kāi)發(fā)更新!

PCIe 8.0規(guī)范開(kāi)發(fā)更新!

評(píng)論