導語

芯片是電子產品的核心,為了滿足不同應用領域的需求,芯片被分為不同的等級。其中,工業級芯片適用于工業自動化、控制系統和儀器儀表等領域,對芯片的可靠性和穩定性要求較高。這些芯片通常具有更寬的工作溫度范圍(-40°C至85°C),能夠在更惡劣的工作環境下正常運行,如高溫、低溫、濕度和振動等。

本篇將從靜電可靠性入手,解答ArtInChip芯片在靜電相關驗證項目的成果,打造“工業級”芯片ESD天花板。

Part 01.

靜電可靠性

電子產品無法忽視的指標

對于芯片來說,其可靠性可初略分為靜電可靠性、生產制造可靠性、壽命可靠性。

靜電可靠性的相關驗證項目,主要包含HBM (Human Body Model,人體對產品靜電放電模型)、CDM(Charge Device Model,產品帶靜電對外放電模型)、LU(Latch-Up,閂鎖)。

HBM、CDM是面向半導體器件的靜電放電測試模型,用于指導半導體的制造、封測、PCBA加工、裝配測試等生產過程中的ESD管控,其管控標準應遠低于所有被加工的元器件中最低ESD耐壓等級。而在進行產品設計選型時,應盡量選用ESD耐壓等級高的元器件,以提高產品的可靠性。

Part 02.

靜電抗擾度

等級劃分及行業標準要求

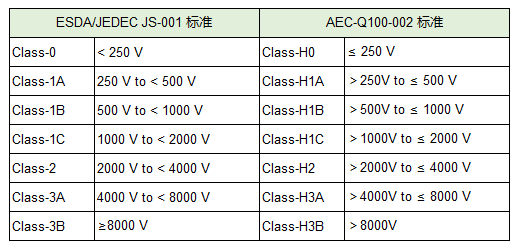

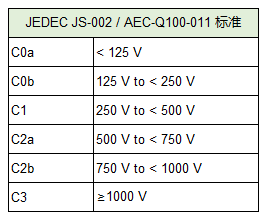

如表1所示為JEDEC和AEC-Q100標準針對半導體器件HBM的靜電抗擾度等級劃分,表2所示為針對CDM的靜電抗擾度等級劃分。而AEC-Q100通常要求HBM通過級別為±2000V;CDM通過級別為±500V,角引腳±750V。

表1:HBM靜電抗擾度等級劃分

表2:CDM靜電抗擾度等級劃分

Part 03.

精密防護

匠芯創打造“工業級”ESD天花板

ESD可能會發生在I/O與電源、地之間,可能會發生在不同的I/O之間,也可能出現在電源和地之間,因此對于ESD保護電路的設計需要考慮所有可能發生ESD的情形。有一種常見的芯片ESD設計方案,沒有直接的電壓鉗位保護結構,而是利用全芯片整個電路的阱與襯底的接觸空間作為ESD電流泄放通道,這種方案成本較小但靜電性能有限。

為了顯著提高芯片的ESD防護水平,匠芯創在芯片ESD設計上從整個芯片防護及可能發生的ESD情形考慮。每個I/O電路中設計相應的ESD保護電路包含二極管、MOS管、靜電泄放器的組合,在發生ESD時能提供電源到地直接低阻抗電流泄放通道;并在合適的位置增加芯片電源和地引腳數量,有效增強抗ESD能力;此外嚴格把控版圖設計,避免出現ESD薄弱環節。

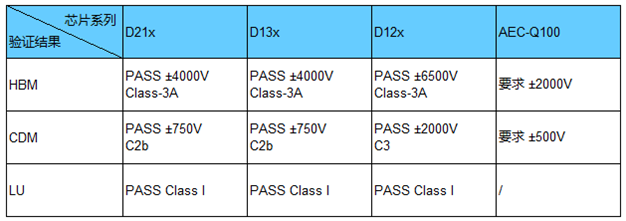

匠芯創D21x、D13x、D12x系列產品在靜電可靠性項目測試結果表現十分搶眼,遠超行業標準要求。其中,在HBM項目上至少通過±4kV Class-3A級別,超出AEC-Q100要求的±2kV Class-2級別;在CDM項目上至少通過±750V C2b級別,超出AEC-Q100要求的±500V C2a級別。

表3:匠芯創產品在靜電可靠性項目測試結果

Part 04.

嚴控成本

匠芯創板級ESD兼具性價比優勢

在板級ESD方面,通常嚴格、完善的ESD設計意味著成本的增加。

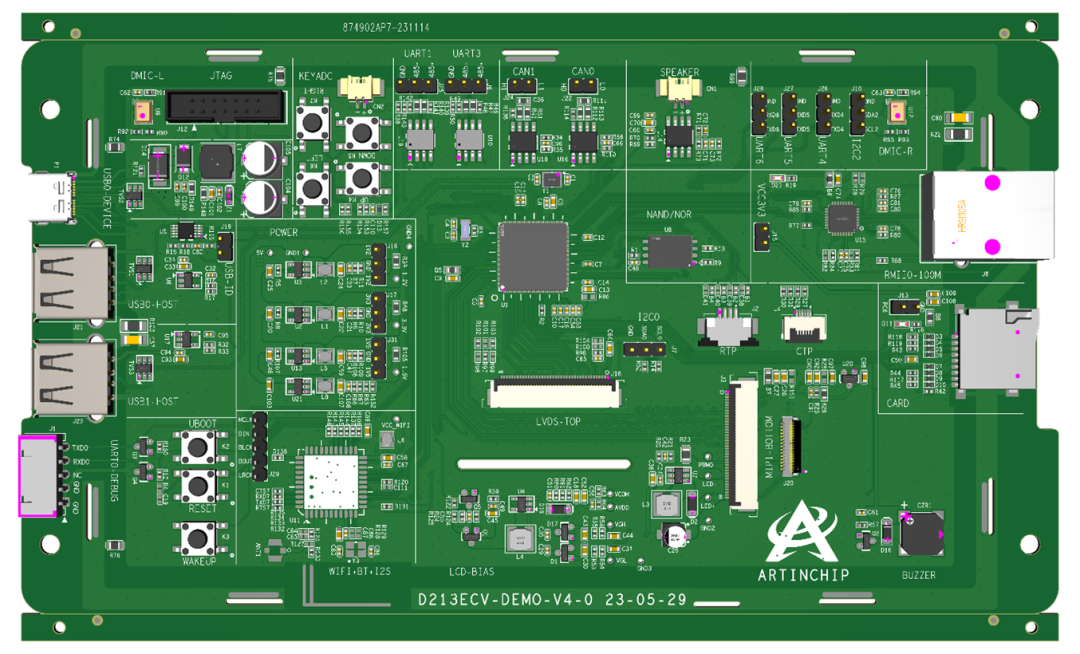

基于匠芯創系列產品設計的兩層板EVB方案,能達到接觸放電±6kV工業三級以上級別,不需要過多的防護器件及增加板卡層數,在滿足工規行業靜電可靠性的同時,還能大大降低成本和設計復雜度,極具性價比。

-

靜電

+關注

關注

2文章

553瀏覽量

38241 -

可靠性

+關注

關注

4文章

281瀏覽量

27604 -

工業芯片

+關注

關注

0文章

27瀏覽量

7700 -

匠芯創

+關注

關注

0文章

58瀏覽量

193

發布評論請先 登錄

芯片可靠性(RE)性能測試與失效機理分析

匠芯創ArtInChip 2025年9月資訊

【匠芯創D133CBS KunLun Pi開發板試用體驗】介紹、環境搭建

【匠芯創D133CBS KunLun Pi開發板試用體驗】《匠芯創D133CBS RISC-V KunLun Pi 》 開箱及搭建vscode開發環境

慕尼黑展會直擊|匠芯創RISC-V芯片矩陣,彰顯國產工業控制芯實力

工業級芯片之三問:靜電可靠性是匠芯創芯片設計端的重要指標

工業級芯片之三問:靜電可靠性是匠芯創芯片設計端的重要指標

評論