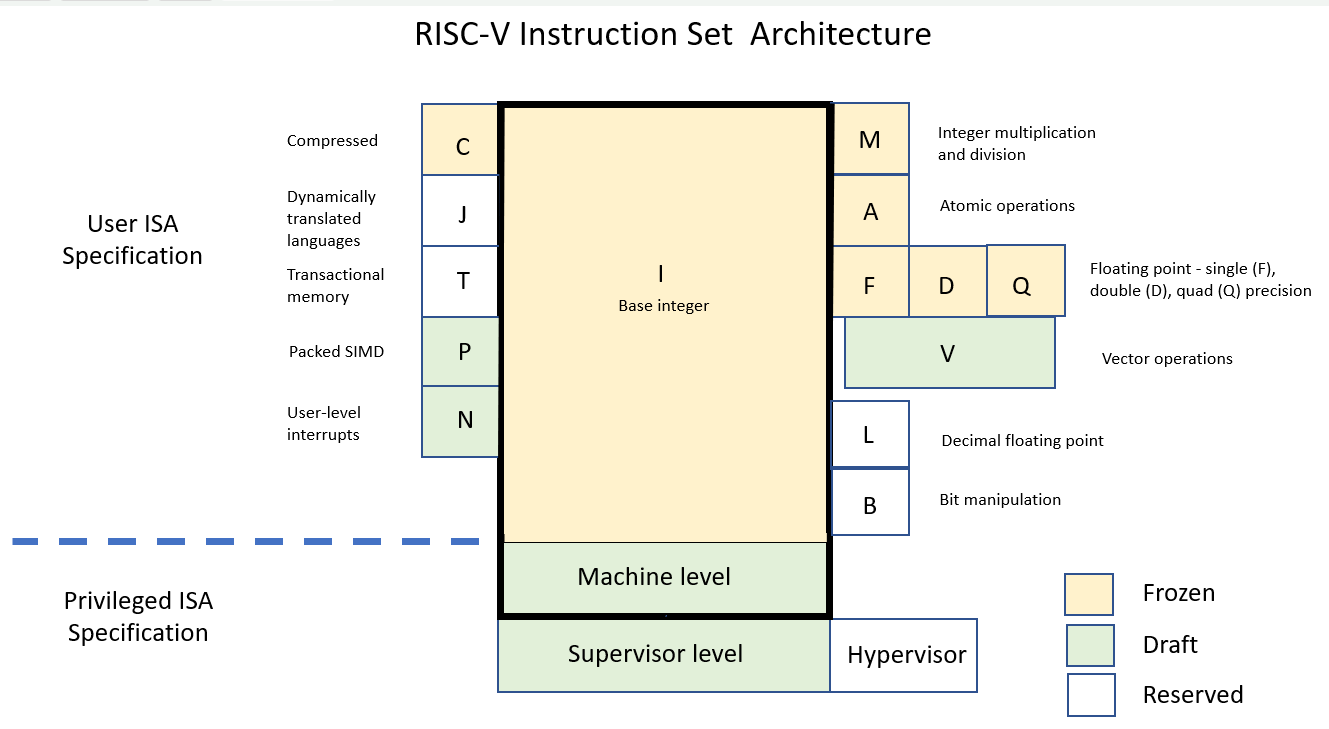

RISC-V(Reduced Instruction Set Computing-V)是一個(gè)開源指令集架構(gòu)(ISA),它的設(shè)計(jì)目標(biāo)是提供一個(gè)簡潔、可擴(kuò)展且高效的指令集,適用于各種應(yīng)用場景,從低功耗設(shè)備到高性能計(jì)算。易靈思提供完整的RISC-V 解決方案,致力于讓開發(fā)者和硬件設(shè)計(jì)人員可以根據(jù)需要自定義和擴(kuò)展指令集,且無需擔(dān)心專有技術(shù)的限制。

RISC-V的特點(diǎn):

簡潔高效:RISC-V采用精簡的指令集,使得每條指令的執(zhí)行時(shí)間更短,提高了處理器的性能。

模塊化設(shè)計(jì):RISC-V支持通過擴(kuò)展來增強(qiáng)處理器功能,比如加速浮點(diǎn)運(yùn)算、增加原子操作指令等。

開源免費(fèi):RISC-V的開源性質(zhì)允許任何人使用、修改和擴(kuò)展指令集,降低了硬件開發(fā)的成本。

可定制性強(qiáng):用戶可以根據(jù)實(shí)際應(yīng)用需求,添加或刪除指令、修改處理器架構(gòu)。

易靈思提供的RISC-V IP支持用戶自定義指令。眾所周知,自定義指令不僅能夠提升特定算法的執(zhí)行效率,尤其是在涉及到計(jì)算密集型或硬件加速任務(wù)時(shí),尤其重要。例如,在數(shù)字信號處理(DSP)、圖像處理或加密解密等應(yīng)用中,自定義指令能夠顯著提高處理速度,并降低處理延遲。通過使用易靈思的Sapphire RISC-V SoC IP核,開發(fā)者可以靈活配置和生成支持自定義指令的系統(tǒng)設(shè)計(jì),充分利用FPGA硬件資源進(jìn)行定制化加速。這樣的設(shè)計(jì)不僅滿足了高性能計(jì)算的需求,也降低了開發(fā)復(fù)雜度和硬件成本。

本次講給大家介紹易靈思RISCV的自定義指令:

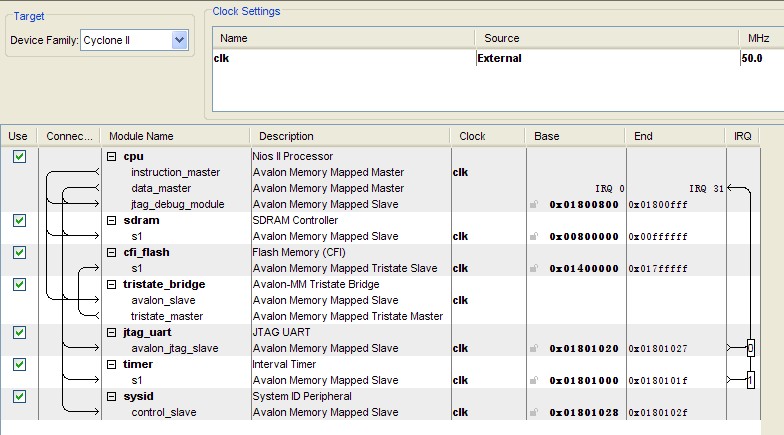

在Sapphire RISC-V SoC中,支持用戶定義的自定義指令,這使得開發(fā)者能夠加速特定的計(jì)算任務(wù)。自定義指令接口支持R型指令格式,并通過兩個(gè)寄存器(rs1 和 rs2)向自定義硬件邏輯傳輸數(shù)據(jù)。用戶可以定義最多1024個(gè)ID,每個(gè)ID對應(yīng)一個(gè)特定的功能。

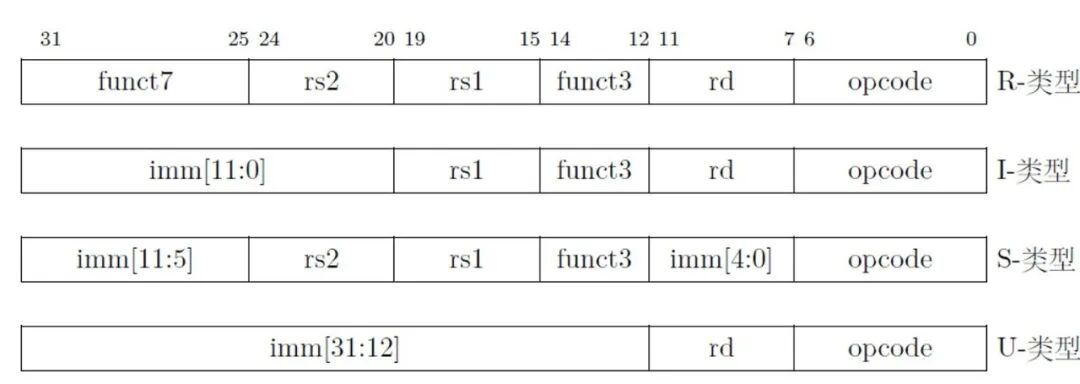

接下來我們先看一下R指令的格式:

上圖是RISC-V手冊中的基礎(chǔ)的指令,我們需要重點(diǎn)看一下R指令格式,其中bit6:0是opcode,bit11:7是rd——作為輸出,bit14:12是function3,bit19:15是rs1,bit24:20是rs2,bit31:25是function7。

其中function3和function7共10bit,因此支持1024個(gè)功能ID。

自定義指令的使用方法:

RISCV DIE中定義指令:用戶可以通過定義一個(gè)特定的功能ID來指定指令的行為。

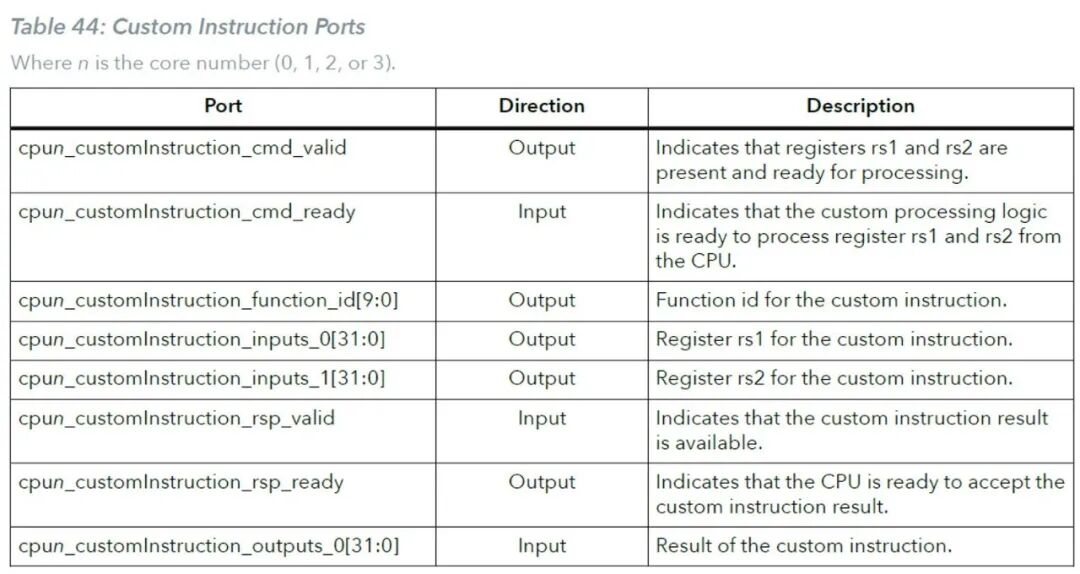

FPGA測處理 對應(yīng)的接口信號:

cmd_valid:指令是否有效,表明指令數(shù)據(jù)已經(jīng)準(zhǔn)備好。

cmd_ready:表示硬件邏輯是否準(zhǔn)備好接收指令。

function_id:指定自定義指令的功能ID,用于標(biāo)識不同的自定義操作。

inputs_0 和 inputs_1:分別對應(yīng)傳遞到自定義硬件邏輯的兩個(gè)輸入寄存器 rs1 和 rs2。

rsp_valid:指示自定義指令的處理結(jié)果是否有效。

rsp_ready:表示處理器是否準(zhǔn)備好接收結(jié)果。

outputs_0:存儲自定義指令的處理結(jié)果,通常會返回到處理器寄存器中。

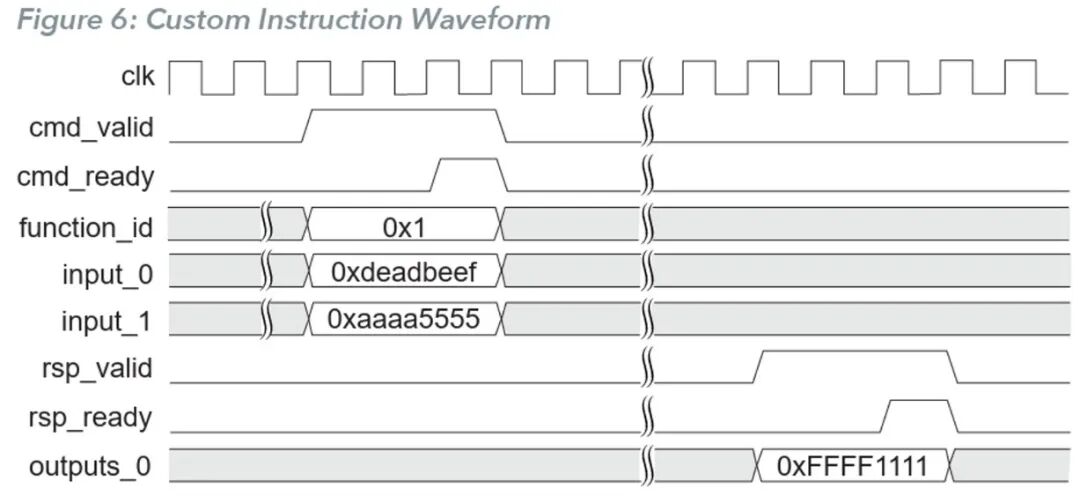

用戶自定義指令的時(shí)序圖:

其中function_id是R指令的function7和function3,{ function7, function3}。

用戶可以根據(jù)function_id和接收到的input0和input_1處理自己的邏輯,比如矩陣加速運(yùn)算等。

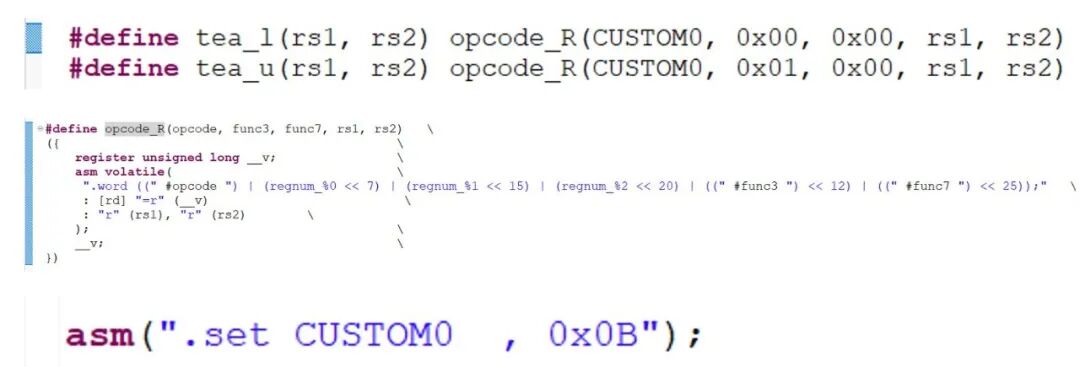

那么在RISC-V開發(fā)中如何撰寫自己的代碼呢?其實(shí)在生成RISCV的參考例子中,我們可以看到有一個(gè)用戶自定義命令的demo(customInstructionDemo),在這個(gè)例子中我們可以看到如下的代碼:

其中tea_l和tea_u傳入rs1和rs2的寄存器的值,也就是對應(yīng)時(shí)序圖中的input_0和input_1,CUSTOM0保持不變,其實(shí)等于0x0B,而第二個(gè)和第三個(gè)參數(shù)對應(yīng)的是function3和function7,對應(yīng)的是時(shí)序圖中的function_id信號,另外我們觀察這個(gè)宏定義,有句話:[rd] "=r" (__v) , 表示將匯編語句的結(jié)果輸出到一個(gè)名為__v的變量中,這個(gè)變量通過"=r"指定為一個(gè)通用寄存器(r)。rd是目標(biāo)寄存器,通常是結(jié)果存儲的地方。也就是接收將時(shí)序圖中的outputs_0信號,然后返回給C語言程序處理。

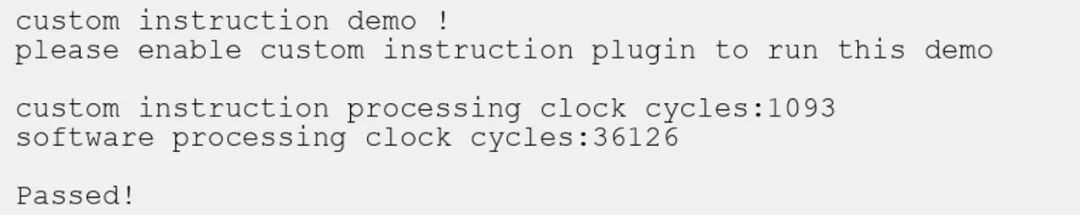

Demo采用一個(gè)加密算法,分別通過RISCV計(jì)算和FPGA測的邏輯計(jì)算進(jìn)行對比,其結(jié)果表明擁有36倍的加速性能:

自定義指令可以顯著提高特定算法的處理效率,尤其是在涉及到頻繁運(yùn)算或者特定硬件加速的任務(wù)中,比如數(shù)字信號處理(DSP)、圖像處理或加密解密等。相信通過使用Efinix的Efinity軟件,開發(fā)者可以配置和生成支持自定義指令的Sapphire SoC設(shè)計(jì),進(jìn)一步增強(qiáng)系統(tǒng)的功能與性能,加快您的設(shè)計(jì)。

隨著易靈思提供的Efinity開發(fā)平臺和RISC-V架構(gòu)的強(qiáng)大支持,開發(fā)者能夠在不依賴專有技術(shù)的前提下,根據(jù)具體應(yīng)用需求快速實(shí)現(xiàn)硬件加速方案。這種高度可定制性使得RISC-V架構(gòu)在面向未來的計(jì)算密集型應(yīng)用中,具有巨大的潛力和競爭優(yōu)勢。通過自定義指令的靈活應(yīng)用,開發(fā)者能夠在實(shí)現(xiàn)高性能和低功耗的同時(shí),進(jìn)一步提升系統(tǒng)的整體效率和可靠性。

因此,無論是在高效的硬件加速應(yīng)用中,還是在需要快速響應(yīng)和高吞吐量的實(shí)時(shí)系統(tǒng)中,易靈思的RISC-V IP核與自定義指令的結(jié)合,提供了一個(gè)理想的解決方案,助力開發(fā)者在更短的時(shí)間內(nèi)實(shí)現(xiàn)創(chuàng)新,推動技術(shù)的快速發(fā)展。

易靈思公司介紹

易靈思是一家國產(chǎn)FPGA公司,總部位于深圳前海。公司憑借自主可控的Quantum硬件架構(gòu),采用邏輯和路由可以互換的XLR結(jié)構(gòu),實(shí)現(xiàn)了創(chuàng)新的產(chǎn)品設(shè)計(jì)與軟件算法,使得FPGA產(chǎn)品具備低功耗、小體積、高密度、高性能等優(yōu)勢。已量產(chǎn)的40nm Trion系列及16nm鈦金系列 FPGA產(chǎn)品,廣泛應(yīng)用于機(jī)器視覺、顯示、工業(yè)控制、醫(yī)療、汽車、AI和通信等終端領(lǐng)域。

重要產(chǎn)品

鈦金系列FPGA具有增強(qiáng)的Quantum架構(gòu),16nm工藝,35K 至 1,000K 邏輯單元,超高性能 300-500MHz,封裝最小可至3.5mm*3.4mm@60K LE,功耗低至競爭對手的1/4,硬核資源豐富,最新產(chǎn)品TJ375現(xiàn)已量產(chǎn)。

-

FPGA

+關(guān)注

關(guān)注

1661文章

22440瀏覽量

637279 -

開源

+關(guān)注

關(guān)注

3文章

4244瀏覽量

46260 -

RISC-V

+關(guān)注

關(guān)注

49文章

2903瀏覽量

53163 -

易靈思

+關(guān)注

關(guān)注

6文章

65瀏覽量

5548

原文標(biāo)題:易靈思FPGA RISC-V 如何使用自定義指令加速設(shè)計(jì)

文章出處:【微信號:易靈思官微,微信公眾號:易靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

NIOS II自定義指令設(shè)計(jì)之實(shí)例篇

如何使用RISC-V創(chuàng)建自定義處理器

采用匯編指示符來使用自定義指令

為什么選擇RISC-V?

SOPC中自定義外設(shè)和自定義指令性能分析

Codasip采用Imperas技術(shù)來強(qiáng)化其RISC-V處理器驗(yàn)證優(yōu)勢

RISC-V以在定制芯片中引入48位計(jì)算

如何看待RISC-V SoC設(shè)計(jì)中自定義擴(kuò)展的指令集架構(gòu)

RISC-V與x86、Arm爭端再起

新處理器使開發(fā)人員能夠?qū)崿F(xiàn)自定義指令并添加加速器

Out項(xiàng)目之增強(qiáng)RISC-V處理器性能的自定義硬件模塊

易靈思FPGA RISC-V自定義指令的使用方法

易靈思FPGA RISC-V自定義指令的使用方法

評論