在現(xiàn)代數(shù)字信號處理(DSP)應用中,FPGA(現(xiàn)場可編程門陣列)憑借其高度并行性、可定制性和靈活性,已成為加速信號處理任務的核心硬件平臺之一。

作為在該領域具備領先技術的廠商,易靈思推出的 40nm Trion 系列與 16nm 鈦金系列(TJ-Series)FPGA,分別面向不同性能層級的 DSP 應用需求,通過高效的 DSP 硬件原語為各類實時信號處理任務提供強大支持。FPGA 中的 DSP 原語是指其內(nèi)部用于執(zhí)行數(shù)字信號處理操作的基本構建模塊,通常包含乘法、加法、累加及移位等專用硬件單元。

與傳統(tǒng)的 CPU 相比,F(xiàn)PGA 能夠以硬件方式并行處理多個信號流,在諸如音頻處理、圖像處理、通信系統(tǒng)、雷達與衛(wèi)星系統(tǒng)等高吞吐、低延遲的應用場景中,展現(xiàn)出顯著的性能與能效優(yōu)勢。

本文將重點解析易靈思 FPGA 中的 DSP 原語結構、功能特性及其在實際設計中的使用方法,幫助讀者理解如何借助這些硬件資源構建高效的信號處理系統(tǒng)。

Part 01 一、Trion 系列 DSP 原語介紹

Trion 系列采用 40nm 工藝,其 DSP 模塊最高運行頻率可達 400MHz,具備 18×18 位硬件乘法能力,適用于中等復雜度的數(shù)字信號處理任務,下圖展示了 Trion 系列 DSP 的運行頻率。

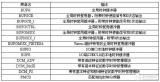

EFX_MULT 原語信號說明:

DSP 是 FPGA 中的一個模塊,有輸入和輸出信號,同時還有一些參數(shù),下圖顯示 Trion 源語的框圖:

針對框圖中的各個信號,具體的解釋如下:

| Port Name | Direction | Description |

| A[17:0] | Input | Operand A |

| B[17:0] | Input | Operand B |

| CLK | Input | Clock |

| CEA | Input | Clock enable A |

| RSTA | Input | Set/reset A |

| CEB | Input | Clock enable B |

| RSTB | Input | Set/reset B |

| O[35:0] | Output | Multiplier output |

| CEO | Input | Clock enable O |

| RSTO | Input | Set/reset O |

另外在使用 DSP 模塊的時候,還需要傳遞一些參數(shù),如下所示:

總結:易靈思 40nm Trion 系列 FPGA 的一個 DSP 支持 18*18bit 的硬件乘法器,在使用的時候進需要根據(jù)原理框圖進行例化即可。

在使用 DSP 源語的時候,如果現(xiàn)在數(shù)據(jù)超過 18*18bit,比如20*20bit 那我們應該怎么辦呢?下推薦一種方法:

首先分割輸入數(shù)據(jù):

對于20位×20位的數(shù)據(jù),可以將 20 位輸入拆分成兩個 18 位的數(shù)據(jù)進行多次計算。例如,假設輸入數(shù)據(jù)分別為 A[19:0] 和 B[19:0],可以按如下方式拆分:

-> A[19:0]可以分解為:A[17:0](低18位)和 A[19:18](高2位)

-> B[19:0]可以分解為:B[17:0](低18位)和 B[19:18](高2位)

然后可以分別計算四個乘積:

低位乘積:A[17:0] * B[17:0]

高低位乘積:A[19:18] * B[17:0]

低高位乘積:A[17:0] * B[19:18]

高位乘積:A[19:18] * B[19:18]

最后,你可以通過加法操作將這些結果合并成一個 20位× 20位 的最終結果。至于采用一個 DSP 復用還是采用多個 DSP 分別計算提高時序,大家可以根據(jù)自己的需求自行設計。

Part 02 二、鈦金系列 DSP 原語進階特性

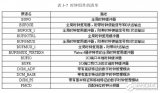

相信有了易靈思 Trion DSP 的源語知識,那么我們再來看鈦金系列DSP 模塊就會簡單一些,易靈思鈦金系列采用 16nm 工藝制造,因此其 DSP 的峰值頻率可以到達 1000Mhz,如下所示:

與 Trion 的 DSP 相比,鈦金系列 FPGA 具有高性能、復雜的 DSP 模塊,能夠執(zhí)行乘法、加法、減法、累加以及4位可變右移操作,并支持多種工作模式,具備更強的運算靈活性與并行處理能力。每個DSP模塊有四種工作模式,分別支持以下乘法操作:

正常模式(Normal):支持 19×18 位整數(shù)乘法和 48 位加法/減法。

雙通道模式(Dual):支持 11×10 位整數(shù)乘法和1個 8×8 位整數(shù)乘法,并具有兩個 24 位加法/減法。

四通道模式(Quad):支持 7×6 位整數(shù)乘法和三個 4×4 位整數(shù)乘法,并具有四個 12 位加法/減法。(注意:7×6 模式的輸出會被截斷為 12 位。)

浮點模式(Float):支持一個融合乘加/減/累加(FMA)BFLOAT16 浮點乘法。

這些整數(shù)乘法器可以表示帶符號或無符號數(shù),具體取決于SIGNED參數(shù)。當多個EFX_DSP12或EFX_DSP24原語映射到同一個 DSP 模塊時,它們必須使用相同的SIGNED值。乘法器的輸入數(shù)據(jù)可以是 A 和 B ,且輸出結果可以用于加法或減法操作。

EFX_DSP48 結構簡介

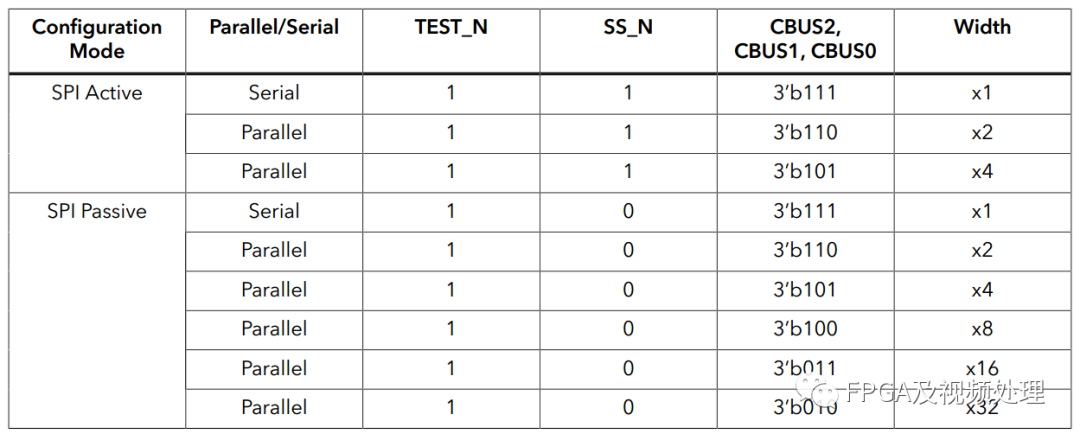

下圖是鈦金系列 FPGA DSP48 的源語框圖:

圖中顯示了 DSP 中的整體原理。圖中藍色是對應的寄存器,我們可以看到一個 DSP48 有一個 19*18bit 的有符號的乘加器,輸出 37 bit ,之后經(jīng)過 P 寄存器(用戶可以自己決定是否啟用)到達 pext,pext 用于擴展 37bit 到 48bit,分為 ALIGN_LEFT:左對齊,右邊的位補 0 ; ALIGN_RIGHT ,左邊補符號位(取決于符號位是 0 還是1 ),pext 同時連接了多個輸出,比如可以通過 M 二選一模塊進入加法器模塊,也可以通過 CASCOUT_SEL 選擇 CASCOUT 輸出。

如果選擇了進入加法器模塊,M_SEL 和 N_SEL 可以選擇加法器的兩個輸入,同時 OP[1:0] 可以選擇加法器的功能(如下圖信號解釋表格所示),加法器的結果可以通過 W_SEL 選擇輸出到 W 寄存器,最終通過 O 寄存器輸出。

下面是 DSP48 模塊的信號框圖和信號詳解,讀者可以根據(jù)對應的解釋和上面的原理框圖進行理解:

鈦金系列DSP48 工作模式詳解:

1. Normal 模式

功能:實現(xiàn) 19×18 位整數(shù)乘法,產(chǎn)生 37 位結果(P),并可擴展至 48 位。乘法器支持有符號或無符號運算,具體由 SIGNED 參數(shù)控制。

擴展與移位:C 輸入為 18 位,可通過 C_EXT 參數(shù)擴展至 48 位。邏輯移位器支持右移 0-15 位,移位方式(算術或邏輯)取決于 DSP 塊的符號設置。移位值由 SHIFT_ENA 端口使能時從 C 輸入捕獲。

適用場景:需要高精度乘法的應用,如濾波器設計或大型累加運算。

2. Dual 模式

功能:同時執(zhí)行一個 11×10 位乘法(21 位結果)和一個 8×8 位乘法(16 位結果),兩個結果均擴展至 24 位。

數(shù)據(jù)路徑:C 輸入被分配到兩個數(shù)據(jù)路徑,每個路徑可獨立擴展。移位器功能與 Normal 模式類似,支持動態(tài)移位控制。

適用場景:中等并行度的信號處理,例如雙通道音頻處理或圖像處理中的像素運算。

3. Quad 模式

功能:實現(xiàn)一個 7×6 位乘法(13 位結果,被截斷為 12 位)和三個 4×4 位乘法(各 8 位結果,擴展至 12 位)。注意:7×6 乘法的輸出會被截斷,因此計算范圍受限。

特殊處理:C 輸入分為四個數(shù)據(jù)路徑。移位器支持多通道獨立移位,增強了靈活性。

適用場景:高并行低精度任務,如機器學習中的權重計算或多通道傳感器數(shù)據(jù)處理。

4. Float 模式

功能:支持 BFLOAT16 格式的融合乘加(FMA)操作,輸入為 BFLOAT16,輸出為 FP32 格式。此模式專為 AI 和機器學習應用優(yōu)化。

配置要求:必須啟用 A_REG、B_REG、P_REG、OP_REG 和 W_REG 等寄存器參數(shù),并設置 P_EXT 和 C_EXT 為 ALIGN_RIGHT。移位器被旁路。

輸出格式:O 輸出包含錯誤標志位(如溢出、無效操作),位 [31:0] 為 FP32 數(shù)據(jù)。

適用場景:浮點密集型應用,如神經(jīng)網(wǎng)絡推理或科學計算。

在使用易靈思鈦金系列DSP源語的時候,讀者需要根據(jù)自己的位寬靈活選擇模式,達到最優(yōu)的資源利用率和最少的 DSP 占用,DSP 更多的使用方法請查看源語手冊。

Part 03 三、總結

易靈思 FPGA 的 DSP 原語從 Trion 系列的 18×18 定點乘法器到鈦金系列支持 1000Mhz、多模式可配置的 DSP48 模塊,均體現(xiàn)出其在硬件加速方面的持續(xù)優(yōu)化與創(chuàng)新。

無論是中低復雜度的嵌入式處理,還是高吞吐、多通道的實時信號處理任務,設計師均可通過合理選用和配置相應的 DSP 原語,充分發(fā)揮易靈思 FPGA 在性能、功耗和靈活性方面的綜合優(yōu)勢,構建出高效、可靠的數(shù)字信號處理系統(tǒng)。

通過本文對易靈思 DSP 原語結構、功能及使用方法的系統(tǒng)介紹,希望讀者能夠更深入地理解其工作原理,并將其靈活運用于實際項目設計中,以實現(xiàn)更優(yōu)的信號處理解決方案。

易靈思公司介紹

易靈思是一家國產(chǎn)FPGA公司,總部位于深圳前海。公司憑借自主可控的Quantum硬件架構,采用邏輯和路由可以互換的XLR結構,實現(xiàn)了創(chuàng)新的產(chǎn)品設計與軟件算法,使得FPGA產(chǎn)品具備低功耗、小體積、高密度、高性能等優(yōu)勢。已量產(chǎn)的40nm Trion系列及16nm鈦金系列 FPGA產(chǎn)品,廣泛應用于機器視覺、顯示、工業(yè)控制、醫(yī)療、汽車、AI和通信等終端領域。

重要產(chǎn)品

鈦金系列FPGA具有增強的Quantum架構,16nm工藝,35K 至 1,000K 邏輯單元,超高性能 300-500MHz,封裝最小可至3.5mm*3.4mm@60K LE,功耗低至競爭對手的1/4,硬核資源豐富,最新產(chǎn)品TJ375現(xiàn)已量產(chǎn)。

-

dsp

+關注

關注

559文章

8220瀏覽量

364374 -

FPGA

+關注

關注

1656文章

22317瀏覽量

631099 -

數(shù)字信號

+關注

關注

2文章

1055瀏覽量

48996 -

易靈思

+關注

關注

6文章

63瀏覽量

5507

原文標題:易靈思FPGA DSP原語使用方法

文章出處:【微信號:易靈思官微,微信公眾號:易靈思官微】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

易靈思(Elitestek)FPGA編程器功能特點及驅(qū)動安裝方法

FPGA設計之浮點DSP算法實現(xiàn)【賽靈思工程師作品】

易靈思推Trion Titanium FPGA,采用 “Quantum? 計算架構”

易靈思FPGA產(chǎn)品幫助安防領域創(chuàng)新和突破

易靈思FPGA軟件更新的節(jié)奏,也許能磨出一個好產(chǎn)品

易靈思FPGA產(chǎn)品的主要特點

易靈思FPGA DSP原語使用方法

易靈思FPGA DSP原語使用方法

評論