一站式PCBA智造廠家今天為大家PCB設計中什么是高速信號?PCB設計中為什么高頻會出現(xiàn)信號失真。在電子設備制造中,高速信號的處理成為PCB設計的關鍵。高速信號通常指頻率范圍從50 MHz到3 GHz的信號,例如時鐘信號。在實際應用中,時鐘信號并非理想的方波,而是具有上升和下降時間的梯形波。這些高頻信號在傳輸過程中容易出現(xiàn)失真,影響系統(tǒng)的整體性能。因此,保證信號完整性在高速PCB設計中至關重要。

什么是高速信號?

高速信號通常指頻率范圍從50 MHz到3 GHz的信號,如時鐘信號。盡管理想情況下時鐘信號是方波,但實際中由于上升和下降時間的存在,時鐘信號在時域中呈現(xiàn)梯形波形,而在頻域中,其高頻諧波的幅度取決于上升和下降時間。

為什么高頻會出現(xiàn)信號失真?

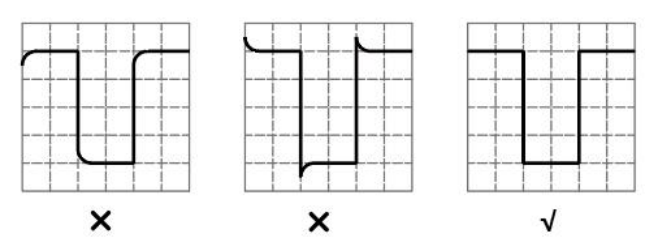

在低頻(>1kHz)下,信號保持在數(shù)據(jù)特征限制范圍內(nèi)。當速度增加時,高頻率的影響開始顯現(xiàn),導致振鈴、串擾、反射、接地反彈和阻抗不匹配問題。這些問題不僅影響系統(tǒng)的數(shù)字特征,還會影響模擬特征,進而影響I/O接口和內(nèi)存接口的數(shù)據(jù)速率。通過PCB設計和有效的布局布線,可以避免這些問題。

保證高速PCB設計中信號完整性的7個措施

1. 阻抗控制

影響阻抗控制的三個因素是基板材料、走線寬度和走線距地/電源層的高度。高頻信號傳輸時,走線的電感和電容開始影響性能,過孔存根和走線缺陷導致的阻抗不匹配會引起信號失真。

常見的終端方案:

- 并聯(lián)終端方案:終端電阻(RT)等于線路阻抗,盡可能靠近負載放置。

- 戴維南終端方案:將終端電阻分成兩個獨立電阻,減少總電流。

- 有源并聯(lián)終端:將終端電阻放置在偏置電壓的路徑上。

- 串聯(lián)-RC并聯(lián)終端:電阻和電容組合充當終端阻抗。

- 串聯(lián)終端:匹配信號源端的阻抗,減少二次反射。

- 差分對端接:在接收端的信號之間需要一個終端電阻,必須匹配差分負載阻抗。

2. 防止傳輸損耗

- 介電吸收:高頻介質(zhì)中的信號使PCB介電材料吸收信號能量,降低信號強度。

- 集膚效應:高頻信號生成的波形在高頻時引發(fā)感抗增加,導致信號強度衰減。

3. 防止串擾

串擾是由于電流通過電線時在附近產(chǎn)生磁場而導致的信號能量交叉耦合。可以通過以下措施減少串擾:

- 走線間距:兩條走線的中心間距至少是走線寬度的3倍。

- 接地層的放置:在不同層之間放置固體接地層。

- 低介電常數(shù)材料:通過降低走線之間的互電容/雜散電容來減少串擾。

4. 避免直角走線和注意過孔位置

直角走線增加拐角區(qū)域的電容值,導致特性阻抗變化,引起反射。通過用兩個45°角代替直角彎曲可以減少反射。過孔位置也會影響信號完整性,應盡量減少走線長度,避免不同走線中的過孔。

5. 不同走線

- 正交布線:在不同層上引導信號,最小化耦合區(qū)域。

- 短平行走線:減少信號之間的并行長度。

6. 避免接地反彈

數(shù)字電路需要快速開關時間,在“0”和“1”信號電平之間切換時會產(chǎn)生地彈,可以通過以下方法減少地彈:

- 引腳轉換率控制:減慢驅(qū)動器的速度,降低跳動率。

- 多電源和接地引腳:防止靠近接地引腳位置的開關效應。

7. 降低EMI

電磁干擾(EMI)影響系統(tǒng)的EMI/EMC性能。可以通過以下措施減少EMI:

- 低電感元件:使用具體低ESR和有效串聯(lián)電感(ESL)的表面貼裝電容。

- 固體接地平面:在電源信號平面旁邊使用實心接地平面。

其他建議

- 確定最高頻率網(wǎng)絡并計算系統(tǒng)中最快上升時間。

- 考慮走線上受控阻抗值、端接和傳播延遲。

- 在帶線和帶狀線路由技術之間進行選擇。

- 考慮不同電源電壓的數(shù)量。

- 為發(fā)射器路徑、接收器路徑、模擬信號、數(shù)字信號等功能創(chuàng)建圖表。

- 確定兩個獨立功能組之間的連接,考慮返回電流和其他走線的串擾。

- 考慮空間寬度間隙。

- 確定最小鉆孔和過孔要求,評估盲孔和埋孔的可行性。

通過這些措施,設計人員可以在高速PCB設計中有效保證信號完整性,提高系統(tǒng)性能和可靠性。

關于PCB設計中什么是高速信號?PCB設計中為什么高頻會出現(xiàn)信號失真的知識點,想要了解更多的,可關注領卓PCBA,如有需要了解更多PCB打樣、SMT貼片、PCBA加工的相關技術知識,歡迎留言獲取!

審核編輯 黃宇

-

PCBA

+關注

關注

25文章

1924瀏覽量

56810 -

高速信號

+關注

關注

1文章

267瀏覽量

18505 -

PCB

+關注

關注

1文章

2307瀏覽量

13204

發(fā)布評論請先 登錄

IDT信號完整性產(chǎn)品:解決高速信號傳輸難題

PK6350無源探頭在高速數(shù)字總線信號完整性測試中的應用案例

Samtec高速線纜深入解析:高速信號完整性的關鍵技術

高頻PCB布線“避坑指南”:4大核心技巧讓信號完整性提升90%

阻抗匹配技術:信號完整性與功率傳輸的基石??

了解信號完整性的基本原理

信號完整性測試基礎知識

信號完整性視角下,SMA插頭PCB連接的原理剖析

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

評論