| 基于3UVPXXCZU15EG+TMS320C6678的信號處理板 |

|

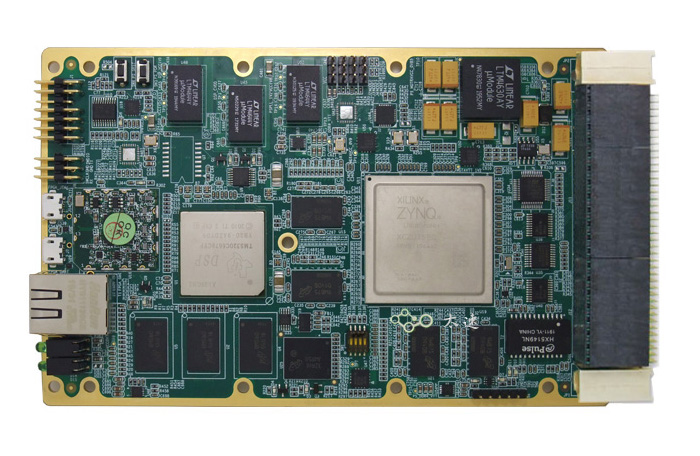

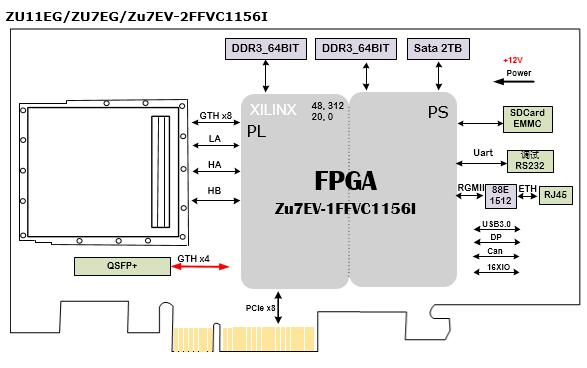

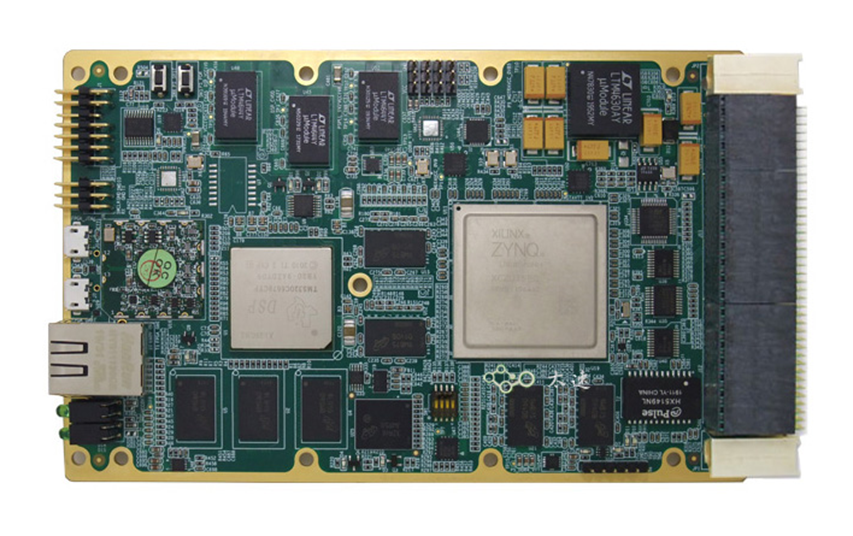

一、板卡概述 本板卡系我司自主研發的基于3UVPX風冷、導冷架構的信號處理板,適用于高速圖像處理等。芯片采用工業級設計。 板卡采用標準3UVPX架構,板上集成一片Xilinx公司ZynqUltraScale+系列FPGAXCZU15EG,一片TI公司的多核浮點處理器TMS320C6678,一片STM32MCU用于板卡狀態監控、電源控制及健康管理功能,板卡集成多片DDR、Flash、PHY、RS422等芯片。 板卡的電氣與機械設計依據VPX標準(VITA46.0),支持導冷,能夠滿足用戶在特殊環境下的使用需求。  |

二、硬件參數

表1:板卡硬件參數

處理器

FPGA:XilinxXCZU15EG-2FFVB1156I

協處理器

MCU:STM32F103C8T6

內存

FPGA-PS:類型DDR4,位寬64bit,容量4GB

FPGA-PL:類型DDR4,位寬64bit,容量4GB

DSP:類型DDR3,位寬64bit,容量4GB

加載方式

FPGA:QSPI,SD卡,eMMC可選擇

DSP:SPI加載模式,SPIFlash32MB

四個,電源狀態指示燈,FPGA狀態指示,DSP狀態指示,MCU狀態指示

FPGA:MicroUSB接口

DSP:2x7PinJTAG接口,間距2.54mm,

MCU:3pinJTAG接口,間距2.54mm,

復位方式

外復位

前面板

4個狀態指示燈

3個處理器仿真器接口

1路FPGA-PS串口

1路FPGA-PS千兆以太網

VPX接口

P0:IIC總線,外復位,外參考時鐘

P1:GTXx16,TTL/LVTTLIOx8

P2:8路RS422,2路RS232,1路1000BASE-T,2路SGMII,TTL/LVTTLIOx8

三、性能指標

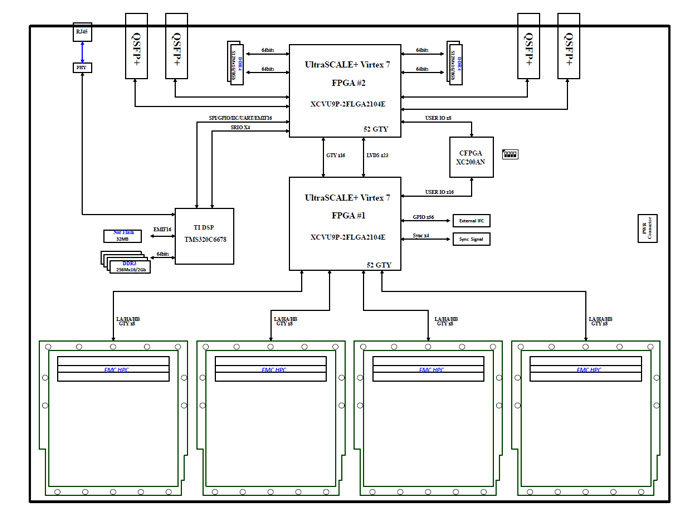

板載一片XilinxFPGAXC7V690T-2FFG1761I。

板載一片TIDSPTMS320C6678。

板載一片STMCUSTM32F103C8T6。

DSP連接一組DDR3,64bit位寬,容量4GB,數據速率1333MT/s。

FPGAPS連接一組DDR4,64bit位寬,容量4GB,數據速率2400MT/s。

FPGAPL連接一組DDR4,64bit位寬,容量4GB,數據速率2400MT/s。

DSP采用SPI加載方式,SPIFlash容量32MB。

FPGA采用QSPI,SD卡,eMMC加載方式。

DSP和FPGA通過SRIOx4@5Gbps/Lane,SGMII高速總線互聯。

DSP和FPGA通過EMIF16,GPIO,SPI,UART等低速總線互聯。

VPXP1支持4組SRIOx4@5Gbps/Lane。

VPXP1支持8個TTL/LVTTL電平IO。

VPXP2支持8路RS422接口至FPGAPL。

VPXP2支持1路RS232接口至FPGAPL。

VPXP2支持1路RS232接口至MCU。

VPXP2支持1路1000BASE-T至FPGA-PS。

VPXP2支持1路SGMII至FPGA。

VPXP2支持1路SGMII至DSP。

VPXP2支持8個TTL/LVTTL電平IO。

板卡芯片采用工業級。

板卡結構采用標準VPX3U大小,支持風冷、導冷結構。

四、物理特性

尺寸:大小為100mmx160mm

工作溫度:商業級0℃~+55℃,工業級-40℃~+85℃

工作濕度:10%~80%

五、供電要求

單電源供電,整板功耗:50W

電壓:DC+12V,5A

紋波:≤10%

六、應用領域

高速信號處理

軟件無線電

標簽: C6678信號處理板 , FPGA 信號處理 , FPGA開發平臺 , XC7Z045板卡 , XCZU15EG板卡

審核編輯 黃宇

-

處理器

+關注

關注

68文章

20300瀏覽量

253674 -

信號處理板

+關注

關注

0文章

29瀏覽量

8892

發布評論請先 登錄

綜合圖像處理硬件平臺設計資料:2-基于6U VPX的雙TMS320C6678+Xilinx FPGA K7 XC7K420T的圖像信號處理板

基于4片DSP6678+FPGA KU115 的VPX高速信號處理平臺

【VPX610】基于6U VPX總線架構的高性能實時信號處理平臺

3U VPX板卡設計原理圖:821-基于RFSOC的8路5G ADC和8路9G的DAC 3U VPX卡

【VPX315】青翼凌云科技基于 3U VPX 總線架構的 JFMQL100TAI + FT-M6678 智能信號處理平臺

【VPX361】青翼凌云科技基于3U VPX總線架構的XCZU47DR射頻收發子模塊

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX雙FMC接口通用信號處理平臺

VPX處理板設計原理圖:9-基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡 C6678板卡, XC7VX690T板卡, VPX處理板

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

評論