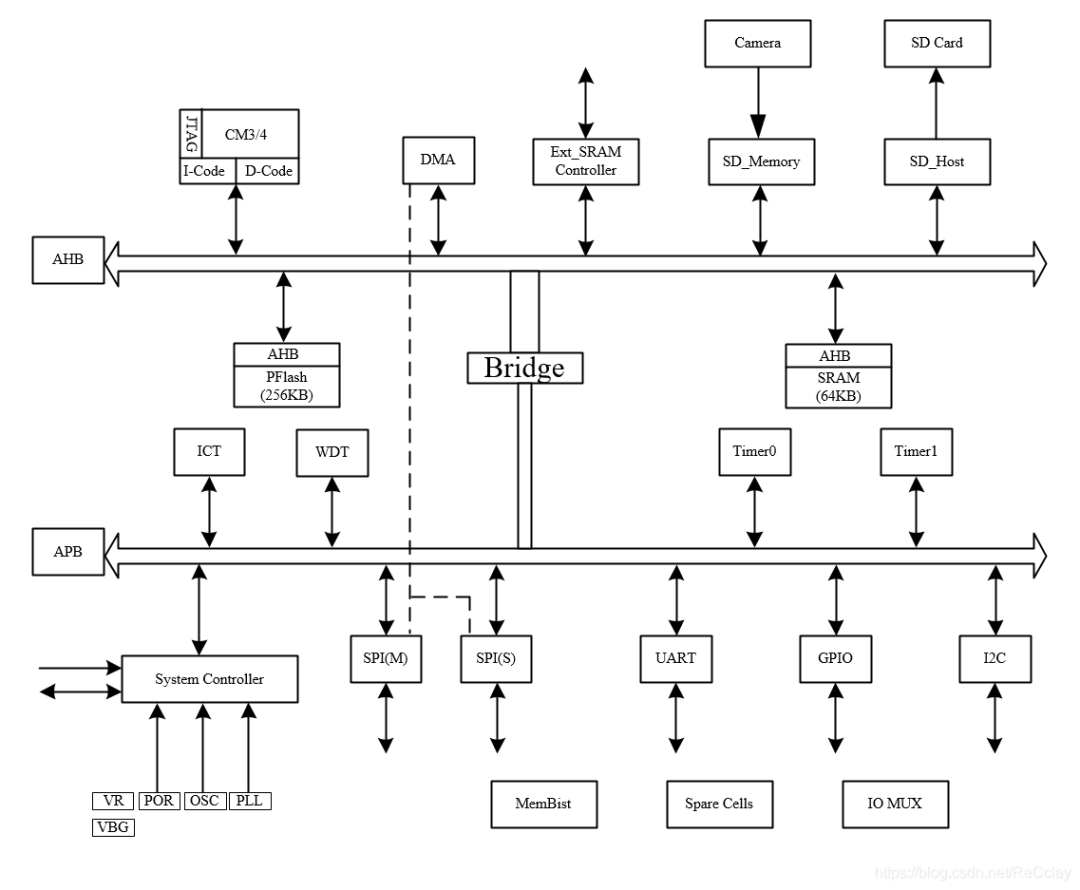

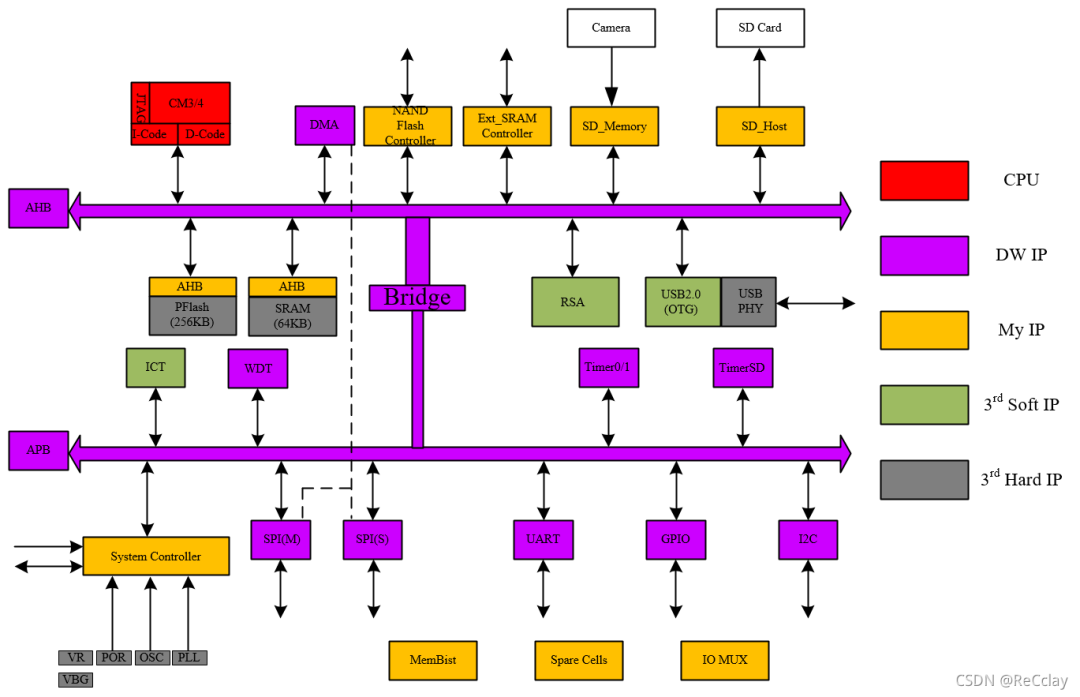

一、SoC 架構圖:核心功能和設計目標

SoC 是基于通用處理器這樣的思路進行設計的,與 PC 設計思路一樣。即通用處理器是由 CORE + MEM 兩部分組成,修改軟件來實現不同的功能,電腦還是同一個電腦,硬件組成還都是一樣的。 SoC 架構圖四大組成部分:

1、核 CORE

2、存儲 MEM

3、外設 IO

4、總線 BUS

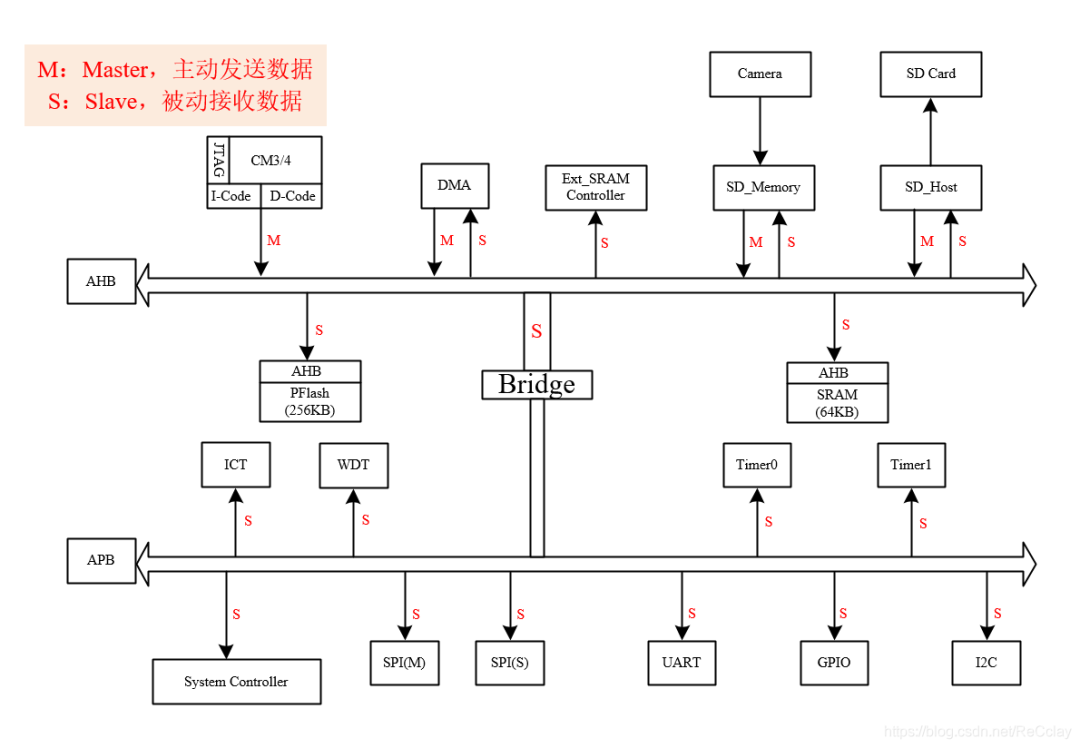

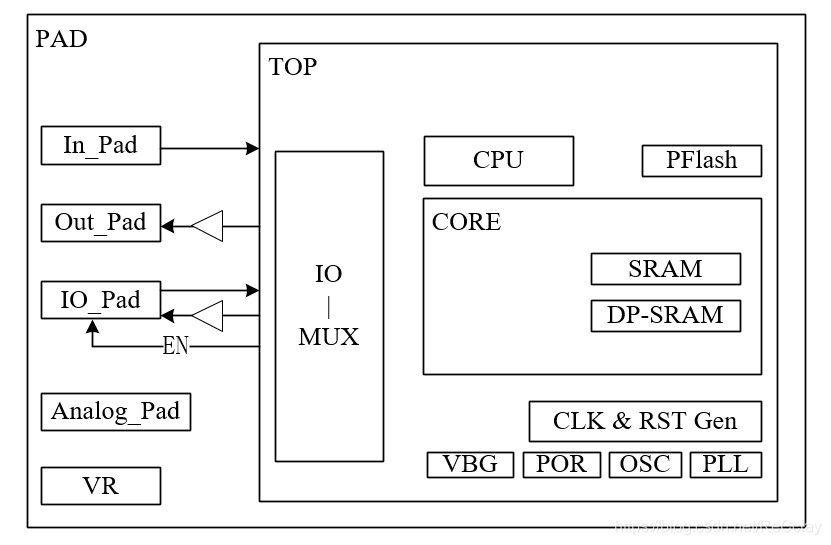

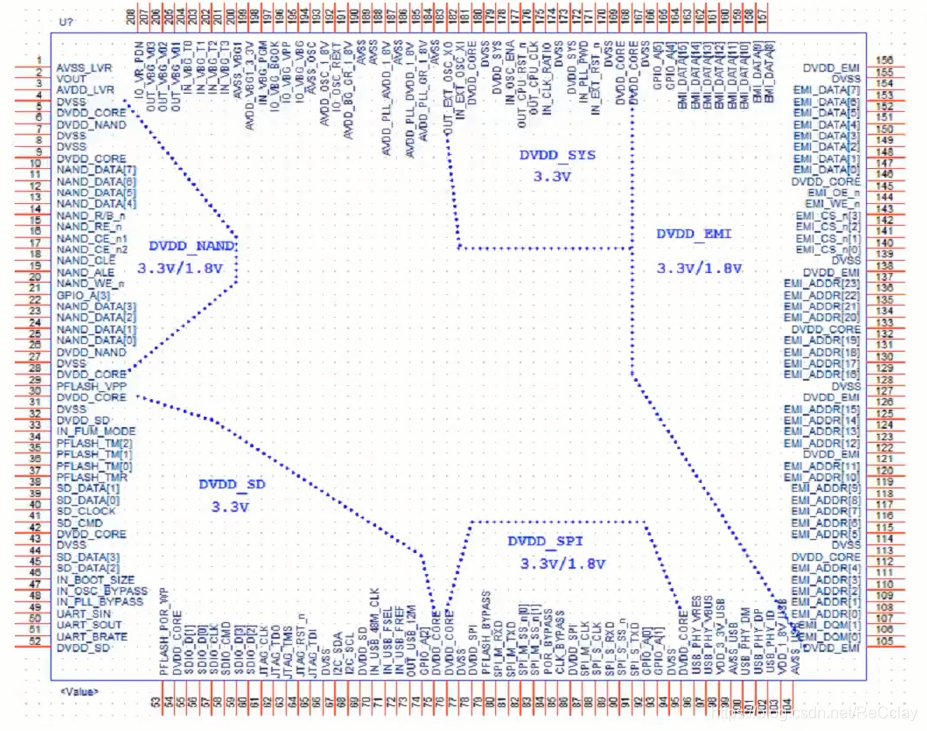

SoC 總的架構圖如下:

1.1、SoC - 核 CORE對于核來講,現在主流的核有三類:

x86 為代表,公司有 AMD 和 INTEL,PC 和 Server 用這類核比較多。

ARM-R 系列:中端,常用在實時場景,如醫療器械,路由交換機

ARM-A 系列:高端,常用在高端應用場景,如手機芯片

ARM 為代表,手機芯片、嵌入式系統等用這類核比較多。

CISC(Complex Instruction Set Computer - 復雜指令集計算機)

RISC(Reduced Instruction Set Computing - 精簡指令集計算機)

基于 ARM 和 x86 之間,可以進行靈活的切換和組裝

暫沒有成熟的商用體系,沒有生態支撐

RISC-V(開源)

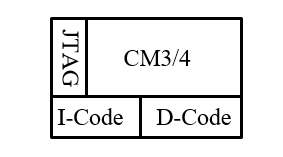

架構圖,左上角為 SoC 系統的核,此處使用的是 ARM 公司的 Cortex-M3/M4 內核。

同時,I-Code 表示指令代碼,D-Code 表示數據代碼。JTAG 用來調試芯片,下載調試程序使用。

注:I-Code、D-Code 即 I-Cache、D-Cache,這個可選的,并不是每個 SoC 都會用到,需要根據實際芯片的規模和需求!

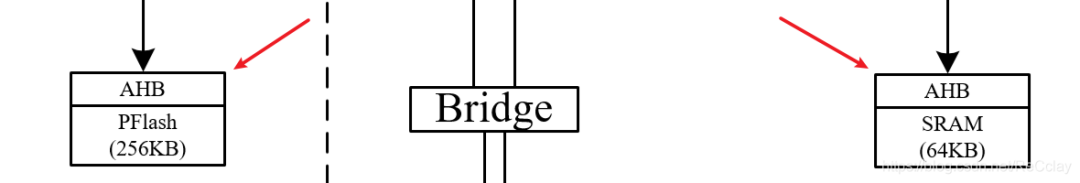

1.2、SoC - 存儲 MEM架構圖,中間部分為 SoC 系統的存儲,此處包含 PFlash 和 SRAM 兩種。

如果 PFlash 不夠用,可以外擴 Flash,如NFC(Nand Flash Controller)

SRAM 是靜態隨機存儲器(Static Random Acess Memory),與之相對的還有一種是動態隨機存儲器(Dynamic Random Acess Memory)。DRAM 需要不斷的刷新才能保持住數據,SRAM 是不需要刷新的!

DRAM 的密度很高,所以當存儲數據容量很大的時候組出來的 Memory 面積就會小一些!SRAM 通常用在小的 SoC 中!

如果 SRAM 不夠用,可以外擴 SRAM,比如上圖中的Ext_SRAM

PFlash(硬盤)中的數據掉電不丟失

SRAM(內存)中的數據掉電丟

即 BootLoader 放在 PFlash 中,一上電便會將其 load 至 SRAM 中,CPU 來 SRAM 取指來執行我們的程序!

core 上電后,會到 PFlash 中取它的指令,來讀取系統要運行的 “軟件”(代碼),在 PFlash 啟動之后,把所需的軟件下載至 SRAM 中,最終在 SRAM 里運行 “軟件”。

SRAM 存儲速率較 PFlash 速率快,故上電跑的程序是放在 SRAM 中,啟動程序以及不需要的數據會存在 PFlash 中。

1.3、SoC - 外設 IO外設 IO 分為兩部分:

一個是高速外設 IO(AHB 100MHz):DMA、Ext_SRAM Controller、SD_Memory、SD_Host

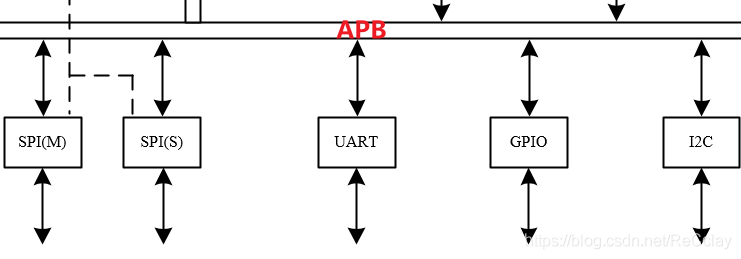

一個是低速外設 IO(APB 50MHz):SPI、UART、GPIO、I2C

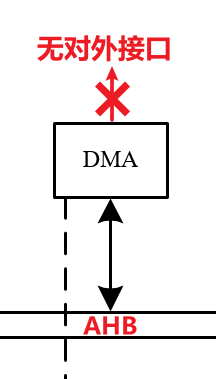

1.3.1、 DMADMA(Direct Memory Access,直接存儲器訪問),使用場景如下:當 CPU 需要搬移 SRAM 中的大量數據時,此時如果使用 CPU 搬移,則會先將 SRAM 中的數據搬移至 CPU 的寄存器中,然后再取指令寫操作等方式搬移至目的地。該方法效率較低,且占用了 CPU 的寶貴處理時間。此時就有了 DMA 的登場,CPU 只需告訴 DMA 引擎,你需要從哪個地址搬移多少個數據到哪個地址,這樣 DMA 就自己聽話地去工作了,不再需要 CPU 的參與,減輕 CPU 的負荷。 DMA 對外沒有接口,這個也可以從架構圖中看出。

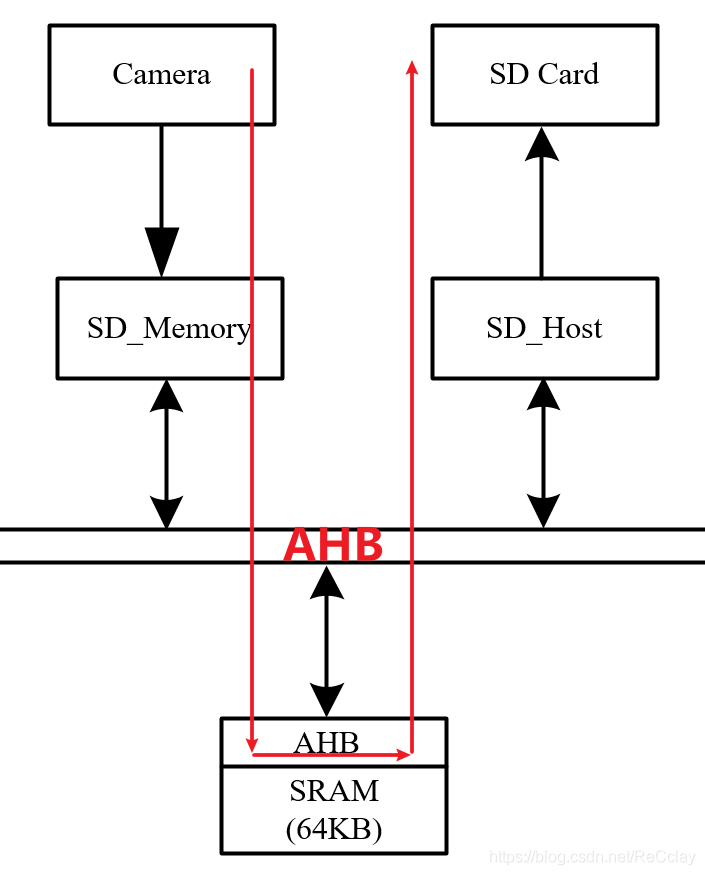

1.3.2、 Ext_SRAM Controller、SD_Memory 與 SD_HostExt_SRAM Controller:通常是 SRAM 大小不夠時,用作擴展使用。 通常 SD_Memory 連接一個諸如 Camera 的設備,將拍到的照片數據通過 SD_Memory 接口存儲到 SRAM 中,然后 SD_Host 接口將 SRAM 中的數據保存至 SD Card 中,取出 SD 卡插入 PC,就可以看到讀取的照片了!

1.3.3、典型低速外設典型的 3 個低速外設接口:I2C、UART、SPI,差異如下:

UART 常用于長距離傳輸,但是速率較低。

I2C 比 UART 速率快,但是速率不會太長;且 I2C 在短距離傳輸時,可以接多個 Slave。UART 是點點通信,1 個 UART 接口只能接 1 個 UART Slave。1 個 I2C Master 接口,可以接多個 I2C Slave;

SPI 相較于 UART 和 I2C 速度會更高;1 個 SPI Master 接口,可以接多個 SPI Slave;SPI 占用的 IO 數也較 I2C 多!

外設與 CPU 進行通信,有兩種方式:

CPU 來查詢我們的狀態

直接給 CPU 發送中斷,CPU 收到中斷后會去處理中斷程序

BootLoader 程序和中斷程序是事先寫好的程序,放到 FLASH 中,一旦啟動后便會將其 LOAD 至 SRAM 中!一旦發生某個中斷,便會根據中斷向量號去查詢中斷程序去執行它。(了解即可)

注:主動發起數據我們稱之為 master;被動接受數據我們稱之為 slave。

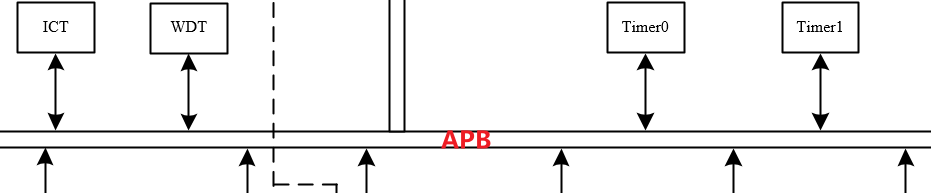

1.3.4、內部組件WDT:看門狗。我們的內核每隔一段時間喂一次狗,如果內核掛掉,看門狗溢出會產生一個中斷,告訴外界,芯片已經掛死,需要處理。 Timerx:硬件計數器。CPU計數精讀低,通常是 us 級,很難達到 ns 級。而我們的硬件計數器精度可以達到 ns 級別;另外,硬件計數,可以減小 CPU 的開銷。 ICT:指令的計數,統計用的!

System Controller:系統控制器

POR:Power On Reset,上電復位(模擬 IP)

OSC:Oscillator,晶振

PLL:Phase Locked Loop,鎖相環

VBG:電源管理

VR:Voltage Regulater,電壓調節器

上述講的 IO 小模塊,以及本節介紹的模擬組件,我們一般都稱之為IP。

1.4、SoC - 總線 BUS將上述介紹的 IP 進行互聯的線,我們將其稱之為總線。這里使用的是 AMBA 2.0 總線,包括 AHB、APB 兩部分。

1.5、其他模塊

1.5.1、MemBistMemBist 主要針對 Memory,如 SRAM。在制造過程中,可能會存在缺陷,當芯片回來之后,我們要進行一些制造型測試!MemBist 是進行內建自測試! 這種內建自測試與其他 IP 外設測試不一樣,其他 IP 外設測試通常是通過 GPIO 灌激勵,然后將經過這些邏輯之后的激勵通過另外一些 GPIO 引出,然后去對比 Partner。而內建自測試是我這個測試,對 SRAM 的測試不需要通過外部的管腳,在 SRAM 外部會包一層 Bist 邏輯,然后相當于在內部觸發一個使能信號,然后它就可以往 SRAM 中灌各種激勵,然后把經過邏輯之后的激勵輸出,就可以完成這樣一個內建自測試。這就是 MemBist 的功能。

1.5.1、Spare CellsSpare Cells 主要是放在頂層,用于芯片后期,在投片時忽然發現有 BUG,這時候要做一個叫 ECO(Engineering Change Order,手動修改集成電路的過程)的東西,這個時候就可能會涉及到一些 cell 的替換,如果之前已經放了 Spare Cells 的話,就可以直接用 Spare Cells,不需要再重新增加 cell。如果增加 cells,可能會導致整個 Die 的面積放不下!所以相當于是提前預留放了一些為我們做 ECO 準備的 Spare Cells,把面積在那占著,這樣的話,整個 FloorPlan 就不用了動了!Cell 在那放著,盡可能最小的去影響我們最終的 FloorPlan。

1.5.1、IO MUX管腳復用,類比 STM32。

1.6、SoC IP

二、SoC 架構圖:簡述 SoC 的功能及應用場景

這種應用在記者、攝影愛好者,數碼相機愛好者等有應用需求。當把數碼相機中的圖片下載到手機上后,可以通過移動網絡,上傳至社交媒體;現場記者,則可以通過將照片及時發送給電視臺、媒體等提供及時的照片素材。

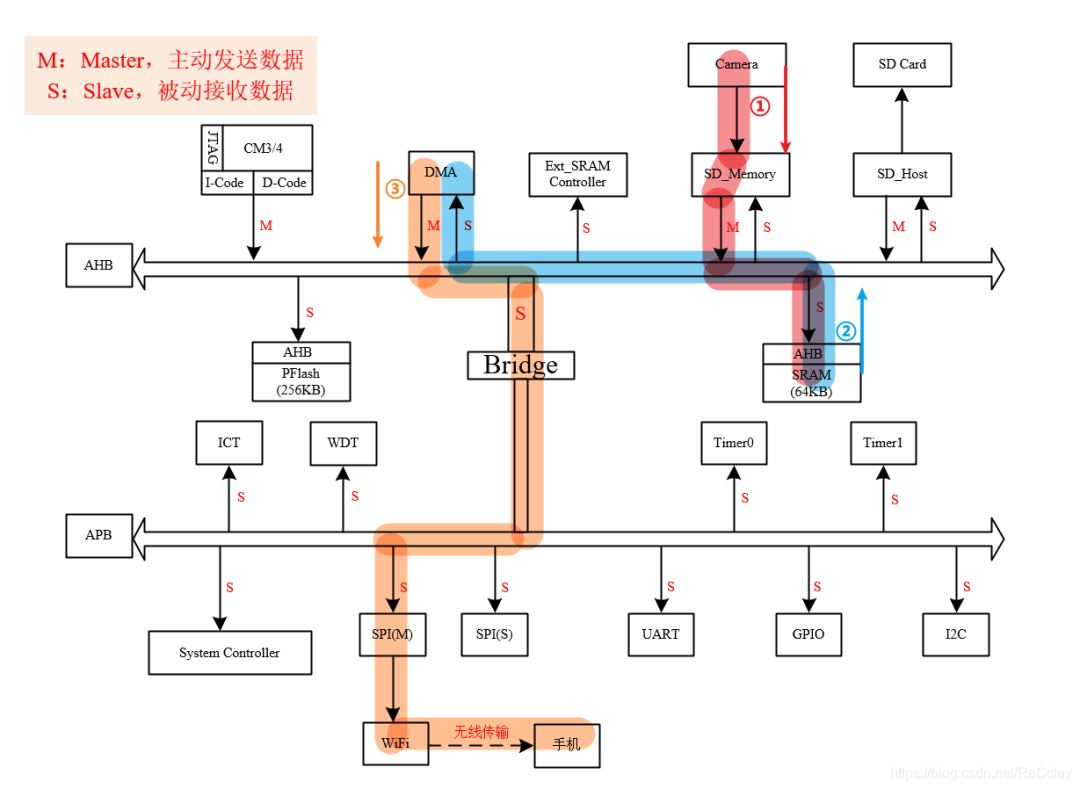

無線通信功能是通過 APB 總線上的 SPI 接口外接一個 WIFI 芯片,實現無線通信和數據傳輸功能。

數據存儲功能主要是 NandFlash 控制器,實現存儲功能。但是該芯片采用了替換方案,使用了 SD-Host 接口,外接 SD Card 的方式進行存儲數據。

典型的應用場景是:數碼相機拍照時,將照片通過 SD-Memory 控制器接口,放入 SRAM 暫存,最后通過 SD Host 接口,將照片存儲到外接的 SD memory 卡中,然后手機 / PC 端用戶,可以連接到 WiFi 上,通過手機 / PC 下載 SD Card 中存放的視頻到手機 / PC。

該芯片是一個 SoC 芯片,主要功能是無線通信和數據存儲功能,主要的應用場景是數據相機的存儲卡。

隨著智能手機的發展,尤其是高清攝像頭的發展,這種無線存儲芯片方案的應用場景在萎縮。

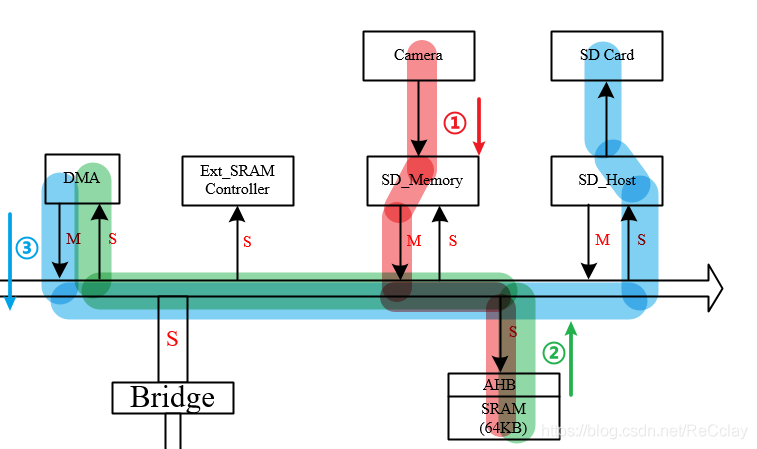

2.1、數據存儲 數據流數據存儲功能的數據流向示意圖(以 DMA 搬移 SRAM 數據為例):數據流按照箭頭,依次是:紅 -> 綠 -> 藍。(下圖標號所在位置是該顏色起始位置)

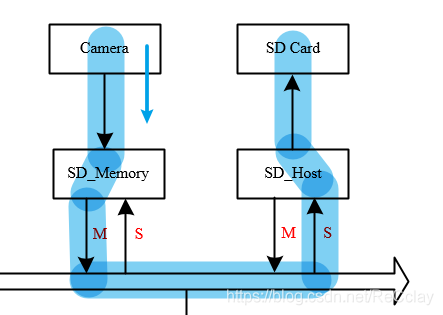

問:為什么不直接從 Camera -> SD Card?如下圖:

答:數據通路是可以通的,但是 Camera 發送數據的速率與 SD Card 存儲數據的速率,這兩個并不一定是完全一樣的,這樣就可能導致數據錯誤。將數據存入 SRAM,相當于起一個緩沖的作用!這樣我數據存進來之后,是存至 SD Card 還是通過 WiFi 進行無線傳輸,都可以通過 CPU 進行靈活控制!

2.2、無線傳輸 數據流無線傳輸功能的數據流向示意圖(以 DMA 搬移 SRAM 數據為例):數據流按照箭頭,依次是:紅 -> 藍 -> 棕。(下圖標號所在位置是該顏色起始位置)

2.3、關于 Master 和 Slave

CPU 通常是一個 Master,數據的發起者;

存儲系統(PFlash、SRAM)是一個 Slave,被動的接收別人發過來的命令,要來讀哪個地址的數據了;

兩個 AHB 高速外設:SD_Memeory 和 SD_Host。既有 Master 口,又有 Slave 口。SD_Memory 模塊工作時,數據是通過 Master 口進行傳輸,Slave 口更多指的是 CPU 對其進行一些配置(IP 可以工作在多種模式,控制信號可以通過 Slave 口對其進行配置);SD_Host 模塊同理。

慢速外設:SPI/UART/GPIO/I2C/Timer/WDT/ICT 等,都是 Slave 口,是 CPU 來告訴他們要傳什么數據出去(CPU 對其進行配置)。

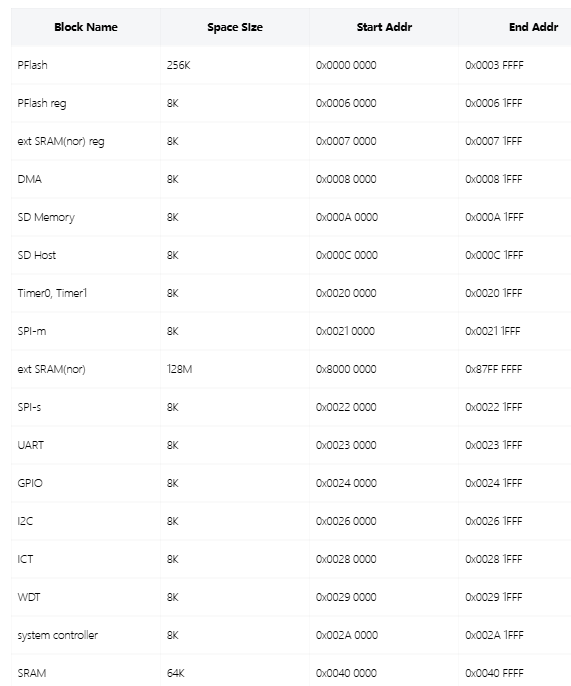

三、SoC 架構圖:IP 總線地址映射基地址:Base Address偏移地址:Offset Address

注:基地址 + 偏移地址 可類比 區號 + 號碼。低 16 位是偏移地址,高 16 位是基地址。

每一次的訪問都是基于地址空間進行訪問的,所以會把每一個系統進行劃分,劃分成為一個地址空間。 各個外設地址如下表:

軟件工程師寫模塊時,通常只關注偏移地址!

一般一個地址空間可以存儲 8bit 數據,故上述單位是KB

四、SoC 架構圖:Pin-MUX & PAD

①、PAD 本身就挺大的,PAD 過多,很占邊長,造成規劃的 Die 放不下。【芯片外圍邊長留足夠的余量】

②、PAD 本身是模擬器件,PAD 過多,會增加功耗!【總體功耗也會有收益】

PAD:芯片與外部通信的一個接口

PIN-MUX:主要用來減少 PAD 數目,為什么要減少 PAD?

上圖展示的三種數字PAD,從上到下分別是:Input Only、Output Only、Bidirection 三種。工程上通常上都是 Bidirection ,使用的時候直接控制 EN 信號,來使其輸入或輸出!

模擬 PAD:如 LVDS;

VR(電壓調節器) PAD

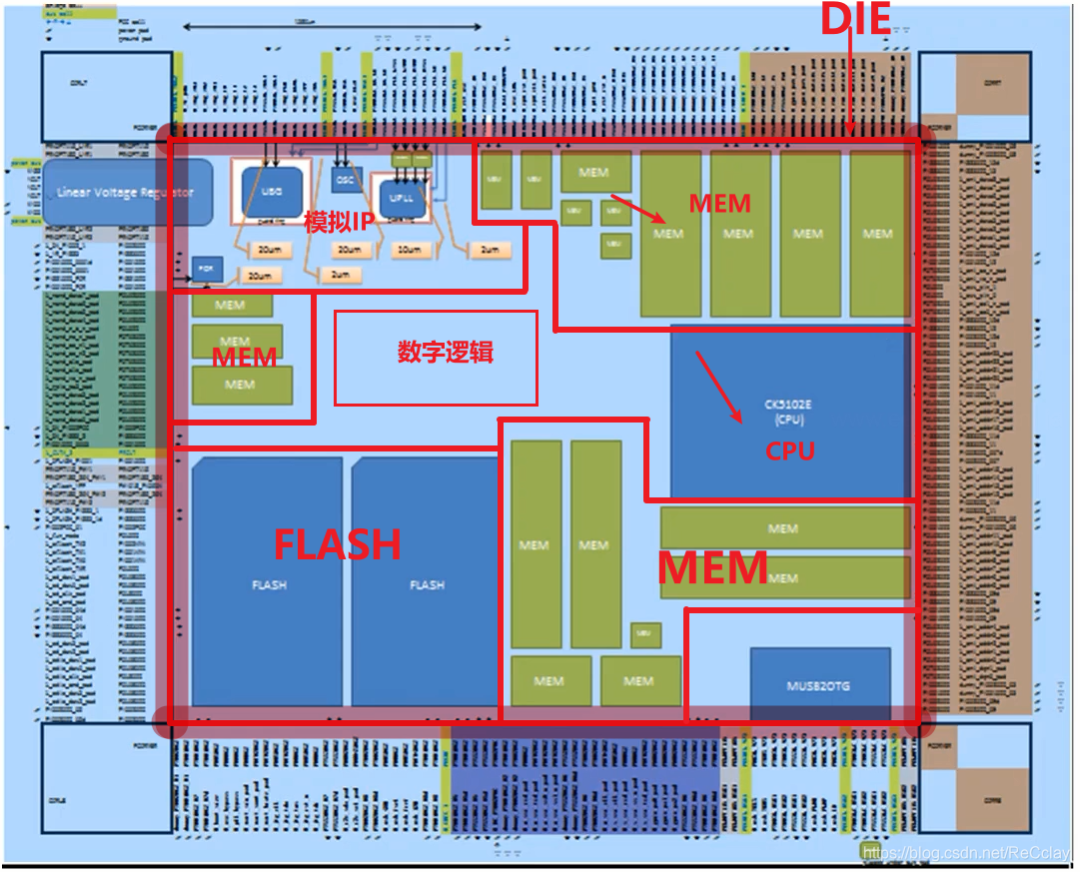

五、SoC 架構圖:版圖布局 Floorplan

注:版圖布局 Floorplan 布局可類比 PCB 的布局!

Floorplan 中可以看到的是各個 Cell(數字電路)和各個 IP(模擬電路)。

模擬IP (MEM/FLASH)放到靠近 DIE 的邊角上,提高空間利用率

DIE 的內部會放數字邏輯

這樣的放置原則是為了提高整個空間的利用率!MEM 這個模擬 IP,可以認為是一個硬核,如果它放中間,那么周圍的繞線就會很麻煩。如果是數字的話,那就是各個離散的 Cell,走線容易,空間利用率高!

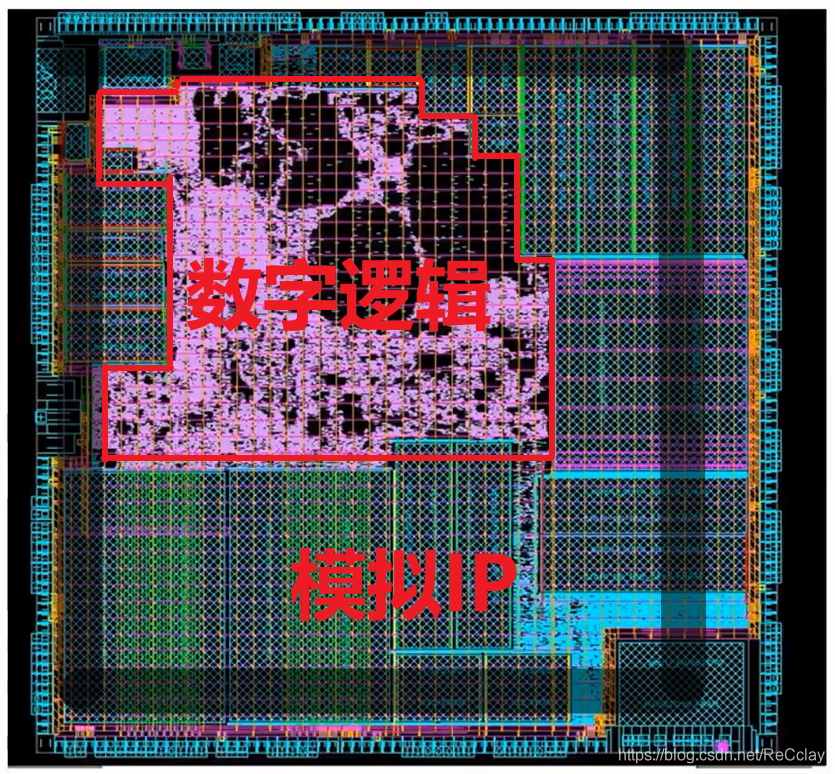

六、SoC 架構圖:版圖 layout - GDSII

注:版圖 layout 可類比 PCB 的布線!

下面的版圖 layout 中,中間紫色部分的就是對應 Floorplan 中標注的數字邏輯部分,周圍靠近 Die 的就是模擬 IP!

工藝水平:110nm e-flash

DIE 大小:3mm x 4mm = 12 mm^2

晶圓 wafer 大小:8 英寸,可以生成 3600 片 DIE(3mm x 4mm),1 個 wafer 的制造成本在 1000 美金。

良率(yield)【wafer 中有多少個 DIE 是可用的】:>95%(通過 ATE 去篩選不能用的 DIE)

六、SoC 架構圖:Pin & 電源電壓下圖為外圍的原理圖,從中可以看到管腳分布和電壓域劃分。

電壓域的劃分工作通常由架構師完成,前端人員是接觸不到這個東西的!

電壓域通常可劃分為:數字電壓域(CORE、IO)、模擬電壓域(不同模擬 IP,不同的電壓)

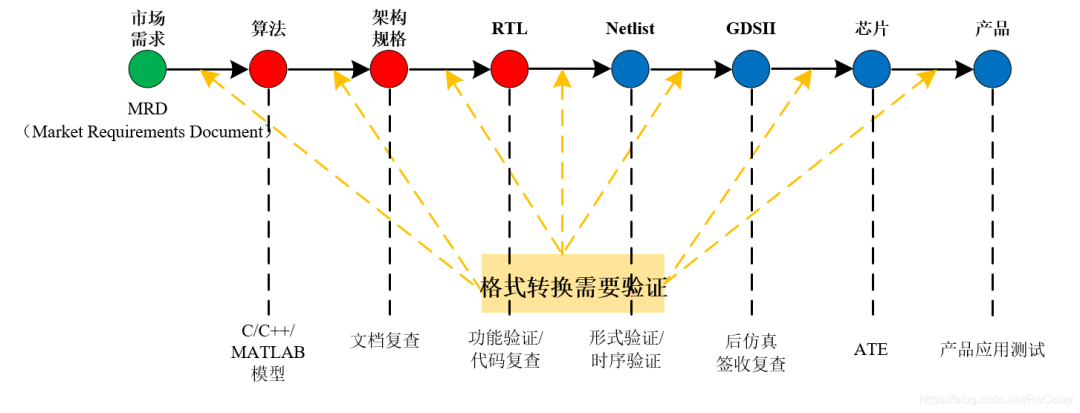

七、數字系統設計節點(SoC Design Node)芯片的誕生,從前期到后期的整個流程:

①、進行市場調研,有沒有市場需求,具不具備很好的商業價值,做芯片很燒錢,1 個 wafer1w 美金,還要買一些 IP 等都要花錢!做出來之后能否賺錢,有沒有人買單,這個很重要!

②、根據市場需求,算法團隊根據要實現的功能,做一個算法模型,算法可以實現(仿真成功),可以達到市場需求,則進行下一步。

③、進行芯片的實現架構設計,包括:軟硬件劃分(哪些部分用軟件實現,哪些部分用硬件實現)、硬件上劃分多少個模塊等,編寫架構文檔(AS,Architecture Specification),架構也分為好多層次,比如系統級,電路級等。接下來還有編寫一個設計文檔(DS,Design Specification)

④、編寫 RTL 代碼,進行功能驗證(EDA 仿真驗證、FPGA 原型驗證)和代碼復查

⑤、通過綜合工具,將其轉化為 Netlist,即將 RTL 代碼映射(MAP)成門級網表(STD CELL),同時進行形式驗證(RTL 邏輯功能和 Netlist 的邏輯功能對比,看看綜合工具是否把 RTL 某些功能給優化掉),時序驗證(實現 Netlist 后,timing setup 能否滿足)

⑥、接下來進行物理實現,GDSII 也是一個網表,只不過是包含了器件位置信息的網表。Netlist 僅僅只是邏輯信息。然后進行一些后仿真和簽收復查。

⑦、投片,在 wafer 上生成我們的芯片。生產過程有沒有問題,通過 ATE 測試,ATE 測試的 partner 是在前面做 RTL 時的 DFx 做的,Membist,Scan 掃描,都是在前期做好的設計,芯片回來之后,會把這些電路啟動,進行 ATE 測試!測芯片本身,有沒有制造功能的問題!

⑧、最后進行應用測試,即功能測試。投放市場。

從上圖看出

①、芯片的實現是需要很多的團隊,很多個環節,一步步實現的。

②、每一個環節的交付件(交付標準)是變化的,每一步都是需要有不同的方法驗證。做 IC 驗證,主要進行 RTL 的功能驗證,要明確從事的工作在整個設計流程中的位置!

參考文獻

芯片測試術語 ,片內測試 (BIST),ATE 測試

-

sram

+關注

關注

6文章

819瀏覽量

117458 -

soc

+關注

關注

40文章

4576瀏覽量

229121 -

通用處理器

+關注

關注

0文章

15瀏覽量

7284

原文標題:了解 SoC 的架構

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文看懂:線束接頭氣密性試驗儀工作原理

新思科技EDA工具和車規IP助力芯粒架構汽車SoC設計

RK3576 能否替代 RK3588?一文看懂 6TOPS 工業 AI SoC 的真實性能差距與選型邏輯

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

高集成度、全數字化架構!SPAD-SoC優勢和技術路線

人臉識別和AES加密協同的SOC設計架構

主流廠商揭秘下一代無線SoC:AI加速、內存加量、新電源架構等

一文看懂芯片的設計流程

高通SoC陣列服務器

SoC集群服務器 與 ARM架構陣列服務器 關系

一文看懂SoC的架構

一文看懂SoC的架構

評論