基于XC7A100T的PCIe千兆電口以太網收發卡

一、板卡概述

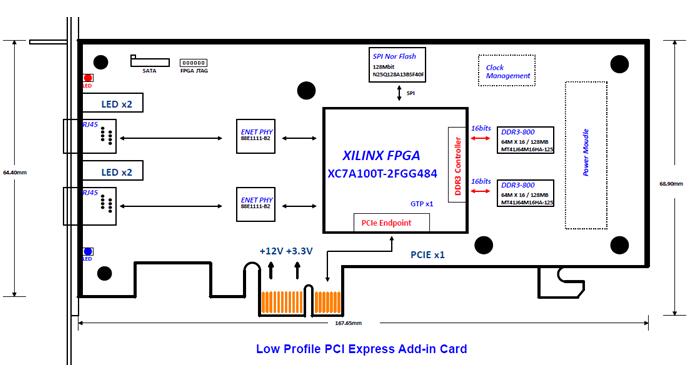

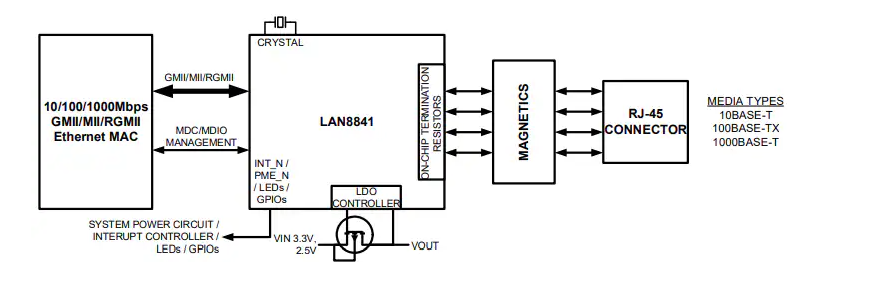

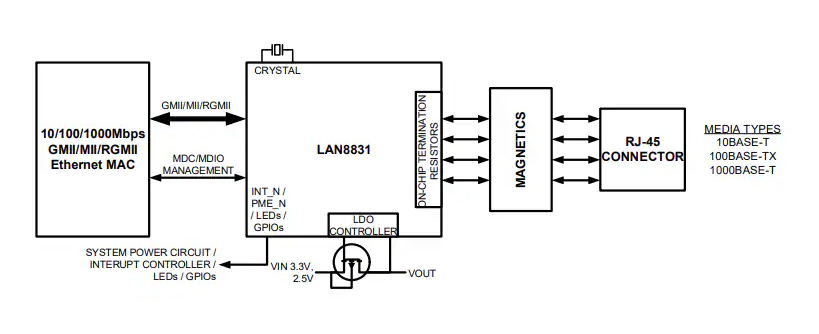

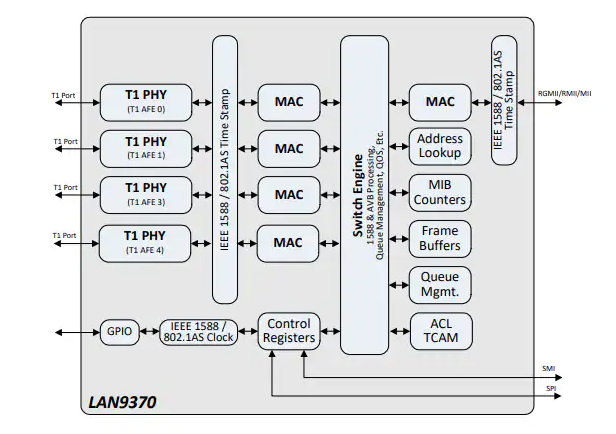

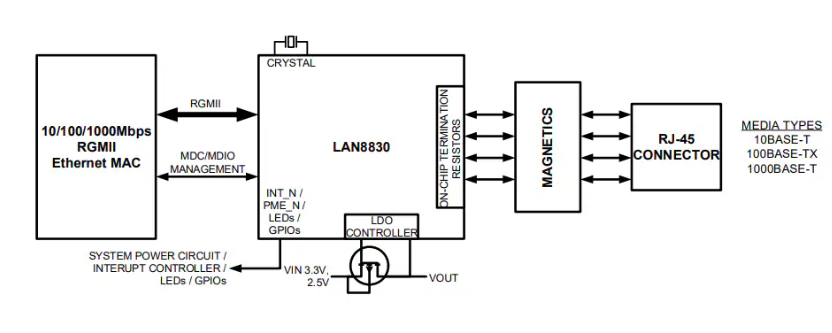

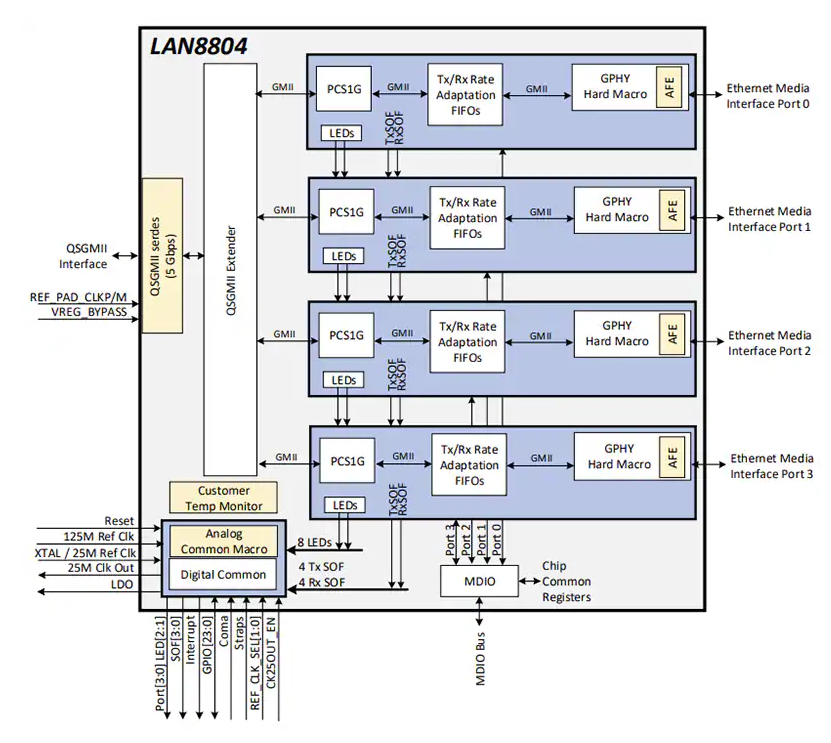

本板卡采用Xilinx公司的Artix7系列的XC7A100T-2FGG484芯片作為主處理器。北京太速科技板卡包含雙路千兆電口網絡,雙組DDR,PCIeX1V1.1接口,板卡設計滿足工業級要求。

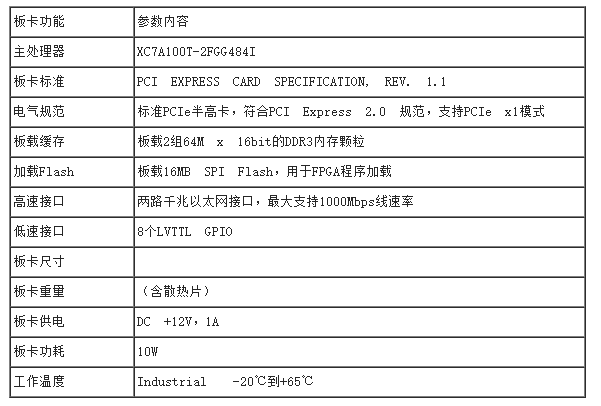

二、功能和技術指標:

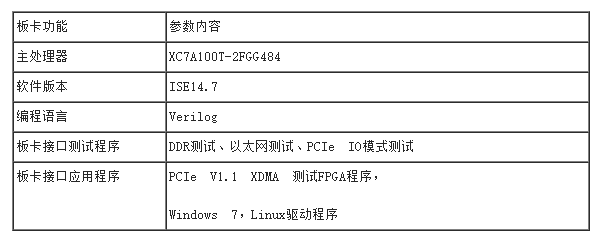

三、接口測試軟件:

板卡功能

審核編輯 黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

以太網

+關注

關注

41文章

5998瀏覽量

180872 -

光電

+關注

關注

8文章

841瀏覽量

83103 -

脈沖

+關注

關注

20文章

908瀏覽量

99762 -

板卡

+關注

關注

3文章

176瀏覽量

17483

發布評論請先 登錄

相關推薦

熱點推薦

數據采集IO卡設計原理圖:136-KC705E增強版基于FMC接口的 Kintex-7 XC7K325T PCIeX8 接口卡

FMC子卡模塊, Kintex-7 XC7K325T板卡, 高速信號處理, 軟件無線電處理平臺, 數據采集IO卡

6UCPCI板卡設計方案:8-基于雙TMS320C6678 + XC7K420T的6U CPCI Express高速數據處理平臺

C6678, C6678板卡, C6678圖像處理板, 高速數據處理平臺, XC7K420T處理板

DP83847 DsPHYTER II:單10/100以太網收發器的全面解析

DP83847 DsPHYTER II:單10/100以太網收發器的全面解析 在當今的網絡通信領域,以太網收發器扮演著至關重要的角色。DP8

一代蜂鳥E203移植普通Artix7核心板中IDE的cfg配置文件修改

XC7A100T的核心板;

在調整好PL蜂鳥SoC的工程后(注釋部分無效代碼,適配對應時鐘,修正引腳約束等),本文中不做展開。然后打開NucleiStudio,新建工程,找到工程中的cfg文件

發表于 10-29 06:45

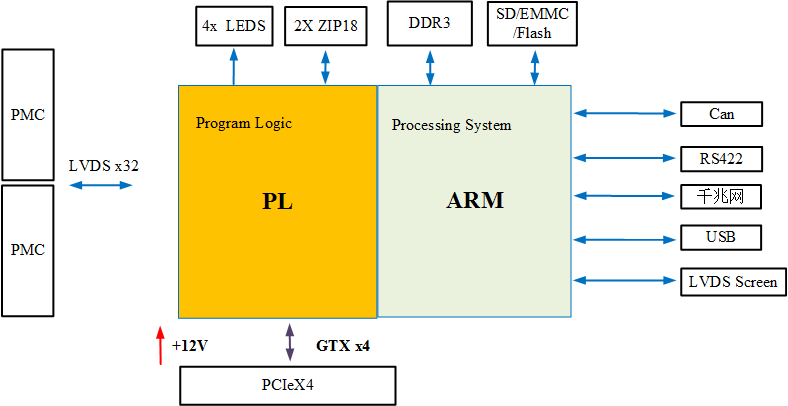

PCIe接口卡設計原理圖:124-基于XC7Z015的PCIe低速擴展底板

板卡由SoC XC7Z015芯片來完成卡主控及數字信號處理,XC7Z015內部集成了兩個ARM Cortex-A9核和一個Artix 7的F

fpga開發板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T開發板用戶手冊-學習板

方式(USB Type-C或40P擴展口)。板載包括:1GB DDR3、128Mb QSPI Flash、64Kbit EEPROM、千兆以太網、HDMI輸出、MIPI接口(除PA35T

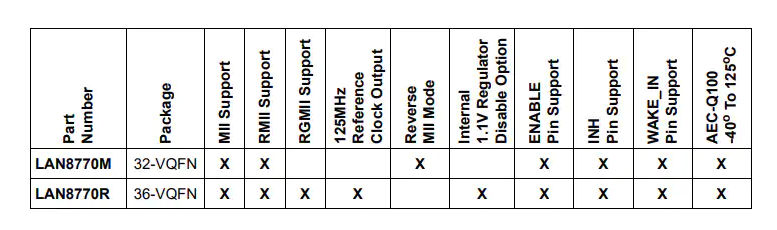

LAN8770 100BASE-T1以太網PHY收發器技術解析

Microchip Technology LAN 8770100 BASE-T1 以太網 PHY 收發器是緊湊型、高性價比、單端口器件,符合 IEEE 802.3bw-2015 規范。LAN8770通過單個非屏蔽雙絞線 (UTP

VPX處理板設計原理圖:9-基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡 C6678板卡, XC7VX690T板卡, VPX處理板

AI邊緣計算,, C6678板卡, PCIe信號, VPX處理板, XC7VX690T板卡

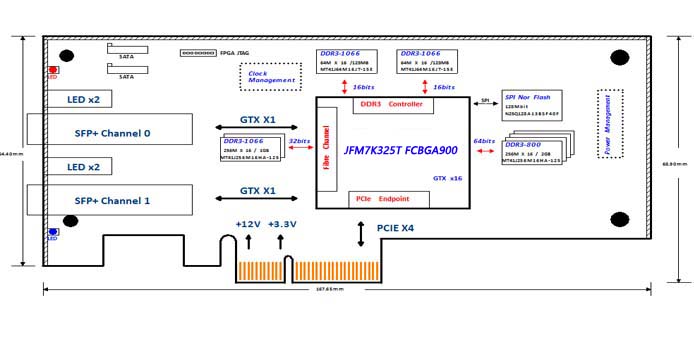

國產化板卡設計原理圖:2295-基于 JFM7K325T的半高PCIe x4雙路萬兆光纖收發卡

JFM7K325T, JFM7VX690T板卡, Ultrasacle萬兆網絡光纖, 高速數據采集系統, 光纖隔離網閘

XC7A100T板卡設計原理圖:297-基于XC7A100T的PCIe千兆電口以太網收發卡

XC7A100T板卡設計原理圖:297-基于XC7A100T的PCIe千兆電口以太網收發卡

評論