?

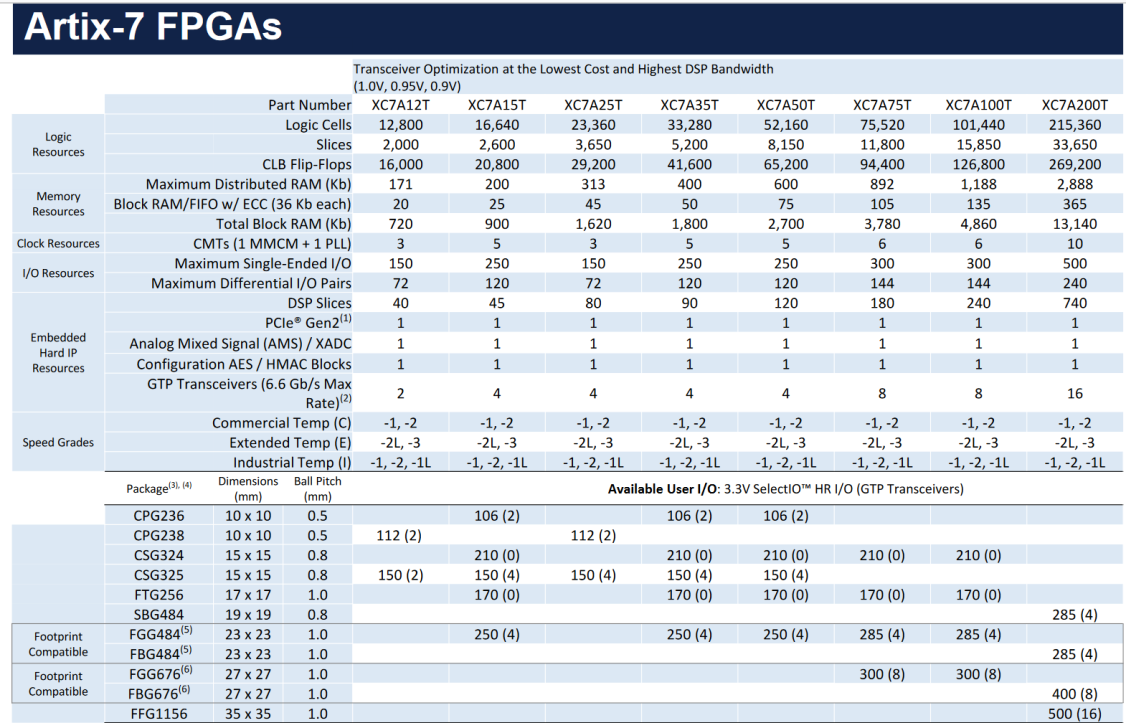

**** 第一章:**** Artix-7 系列介紹

Artix-7 系列:相對于 Spartan-6 系列而言,Artix-7 系列功耗降低了一

半, 成本降低了 35%,采用小型化封裝、統一的 Virtex 系列架構,能滿足低成本 大批量市場的性能要求,這也正是此前 ASSP、ASIC 和低成本 FPGA 所針對的市場 領域。新產品系列既能滿足電池供電的便攜式超聲波設備的低功耗高性能需求,又 能滿足商用數碼相機鏡頭控制的小型、低功耗要求,還能滿足軍用航空電子和通信 設備嚴格的 SWAP-C(大小、重量、功耗和成本

?編輯

Artix-7 器件資源如下表列出,我們選用35/75/100/200 做為開發板的主控芯片:

?編輯

[]() []()第二章:PA-Starlite **** 開發板概述****

[]()2.1.板卡概述

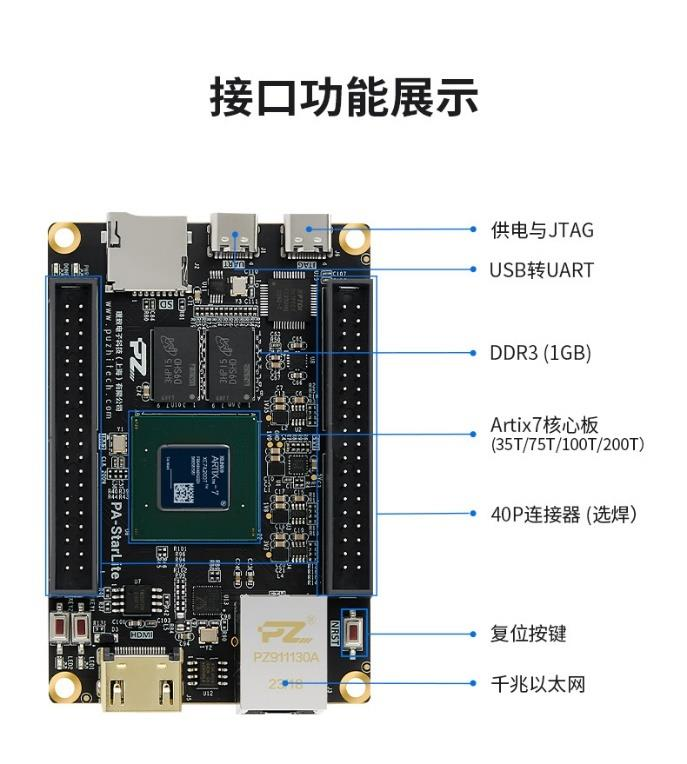

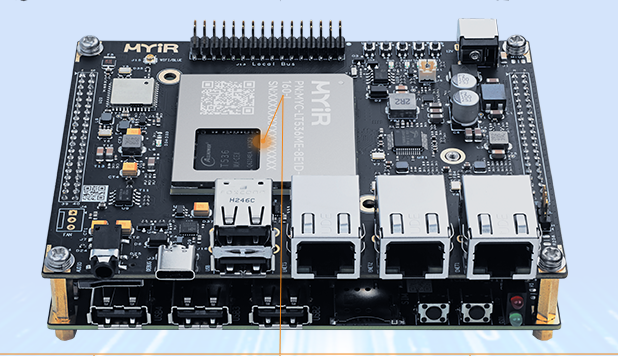

璞致電子科技 Artix-7 系列開發板提供了四個版本,使用XILINX 公司的

XC7A35T-2FGG484I/XC7A75T-2FGG484I/XC7A100T-2FGG484I/XC7A200T-2FBG484I 作 為主控制器,我們根據主控芯片的不同分別命名開發板名字為 PA35T-Starlite

/PA75T-Starlite/PA100T-Starlite/PA200T-Starlite,其中 PA35T-Starlite 不帶 Mipi 接口,其他三款管腳完全兼容。

璞致電子科技 PA-Starlie 系列開發板每款板卡都提供帶 40P 連接器和不帶 40P 連接器兩個版本。方便了用戶作為開發板或者當成項目核心板使用。

另外,開發板集成了豐富的外設資源,提供了詳盡的開發例程,加速了用 戶學習進度。除此之外,開發板還集成了 JTAG 調試器,做到了一根 USB 線就可 以實現供電和調試兩用,使用更加便捷。

關于開發板的詳細說明,可以查閱下文對應章節。

?編輯

?編輯

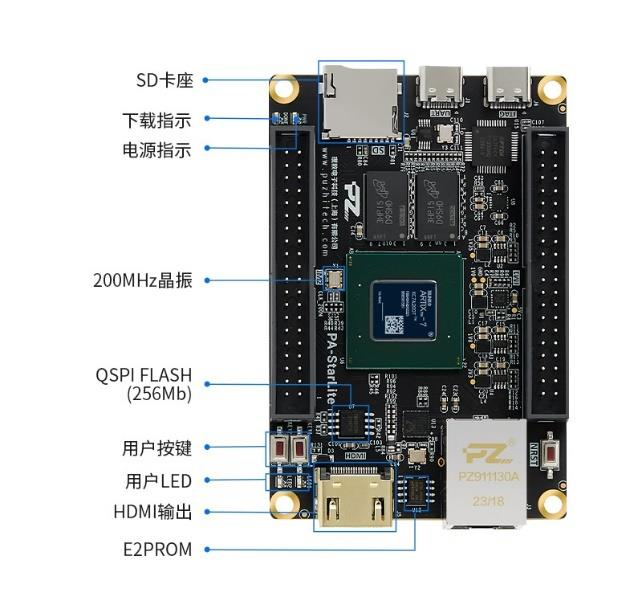

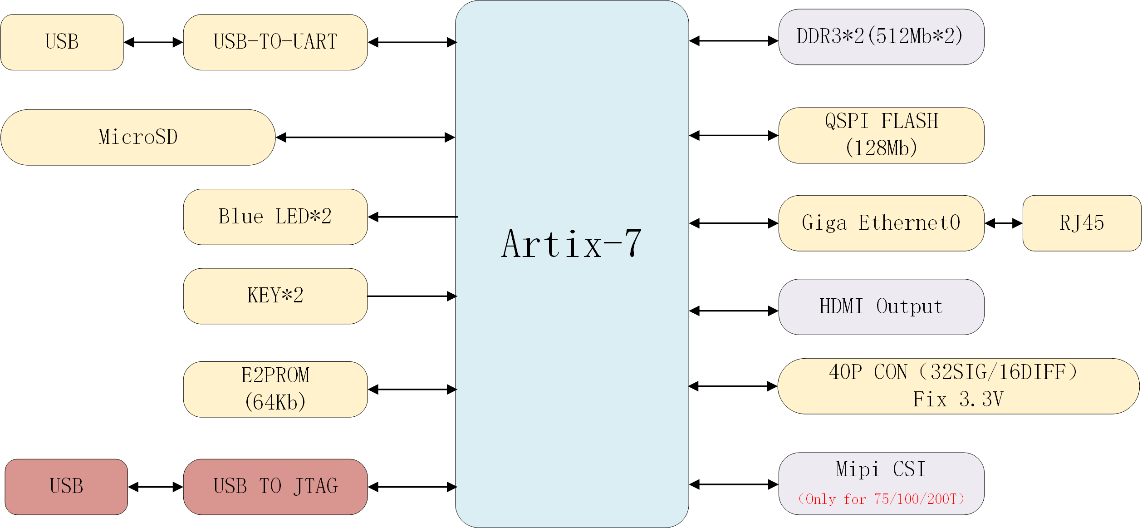

[]()2.2.開發板資源和框圖

如下分別為開發板的框圖和板載資源表,用戶可對比查看。

?編輯

?編輯

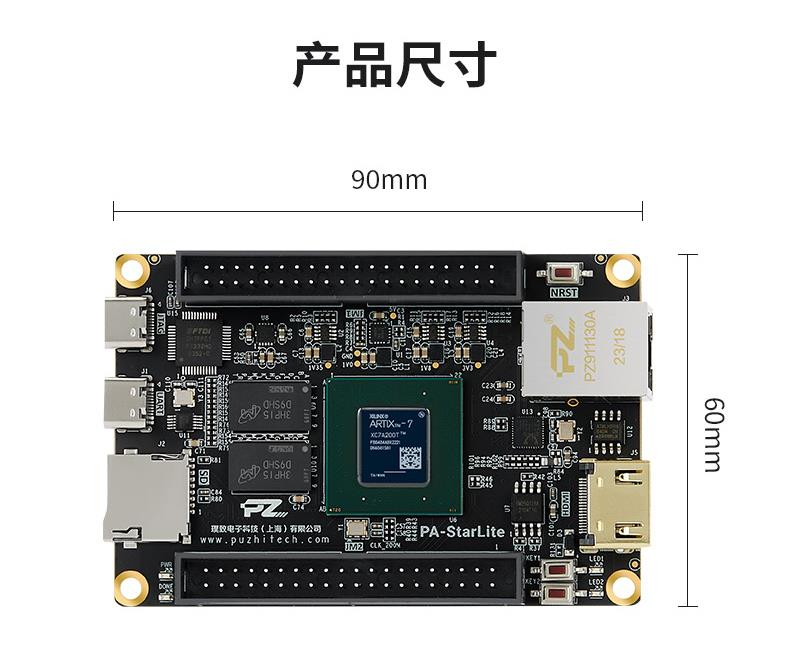

[]()2.3.開發板尺寸

如下圖標出開發板尺寸為 90x60mm,開發板的四個角各放置一個固定孔,用 于安裝支撐柱或固定單板,孔徑為 3.5mm。如下圖以 PA200T-Starlite 為例,其 他三款尺寸跟 PA200T-Starlite 一樣大。

?編輯

[]() []()第三章:璞致 **** PA-Starlite 開發板接口說明****

[]()3.1.關于供電

璞致 PA-Starlite 系列開發板提供了兩種供電方式:一種是用 TypeC 線連 接電腦給板卡提供 5V 電源;另一種是通過 40P 連接器上的排針給板卡提供 5V 電源。兩種供電方式二選一,根據用戶實際需求來選用哪種供電。

采用 USB 線給板卡供電,即是當成開發板使用。采用40P 連接器供電,用 戶可以把板卡當成核心板,用戶設計擴展底板,擴展其他功能。

?編輯

[]()3.2.系統時鐘

開發板提供了一路 200M 差分時鐘給主控芯片,連接的管腳名稱分別為

IO_L13P_MRCC_34/ IO_L13N_MRCC_34,對應的管腳位置為 R4/T4。更詳細說明可參考 璞致提供的開發板原理圖。

[]()3.3.開發板復位

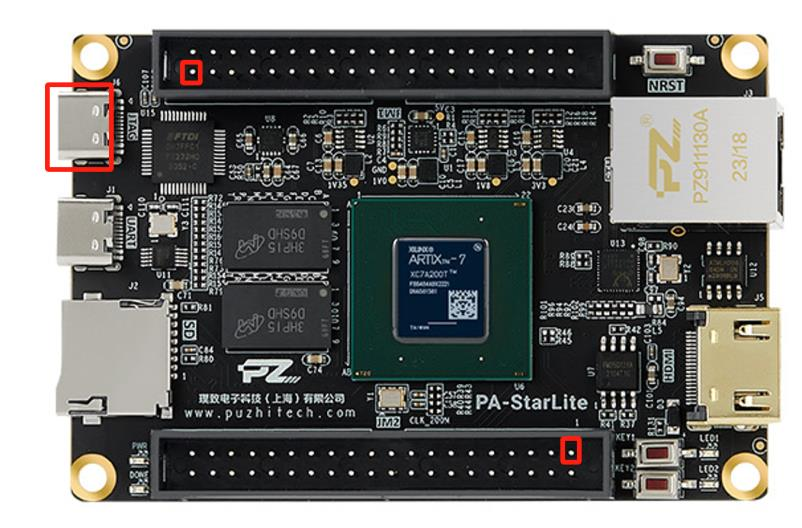

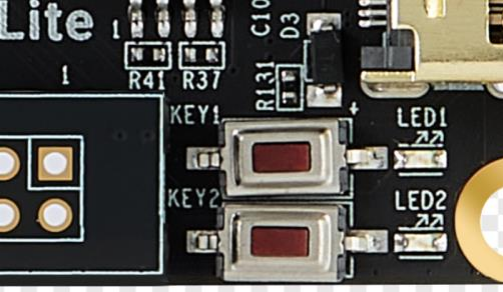

開發板上設計了一路復位按鍵,按鍵所在位置如圖示,對應的管腳名稱為 IO_L19N_14,管腳位置為 R14。更詳細說明可參考璞致提供的開發板原理圖。

?編輯

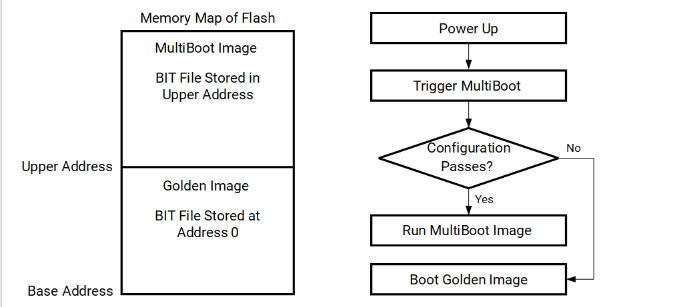

[]()3.4.開發板啟動方式

主芯片的啟動模式分別是 JTAG、QSPI Flash,默認配置為 QSPI Flash 啟動,但 JTAG 模式優先級要高于 QSPI Flash,所以當用戶連接了 JTAG 接口芯片優先從 JTAG 啟動,不用做啟動模式切換。核心板上 QSPI Flash 容量為 128Mb,更詳細說明可參考 璞致提供的開發板原理圖。

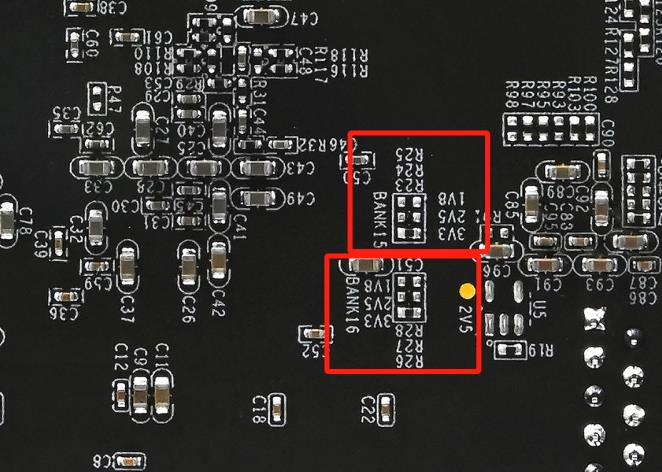

[]()3.5.BANK********電平選擇

開發板上連接到 40P 連接器上的 BANK15/16 為 HR BANK,為方便用戶使用,我們 設計了 IO 電平可以在 1.8/2.5/3.3V 三種電平下選擇,默認電平為 3.3V,用戶需要調 節其他電平可以開發板上位置指示來調整 BANK 電平。 更詳細說明可參考璞致提供的 開發板原理圖。

?編輯

[]()3.6.DDR3********資源

主芯片配置了兩顆 DDR3,單顆容量 512Mb,共計 1GB,DDR3 管腳分配參見下表, 更詳細信息可參考璞致提供的原理圖或者例程。

| DDR3********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DDR3_DQ0 | IO_L2P_35 | C2 |

| DDR3_DQ1 | IO_L5P_35 | G1 |

| DDR3_DQ2 | IO_L1N_35 | A1 |

| DDR3_DQ3 | IO_L6P_35 | F3 |

| DDR3_DQ4 | IO_L2N_35 | B2 |

| DDR3_DQ5 | IO_L5N_35 | F1 |

| DDR3_DQ6 | IO_L1P_35 | B1 |

| DDR3_DQ7 | IO_L4P_35 | E2 |

| DDR3_DM0 | IO_L4N_35 | D2 |

| DDR3_DQS_P0 | IO_L3P_35 | E1 |

| DDR3_DQS_N0 | IO_L3N_35 | D1 |

|---|---|---|

| DDR3_DQ8 | IO_L11P_35 | H3 |

| DDR3_DQ9 | IO_L11N_35 | G3 |

| DDR3_DQ10 | IO_L8P_35 | H2 |

| DDR3_DQ11 | IO_L10N_35 | H5 |

| DDR3_DQ12 | IO_L7N_35 | J1 |

| DDR3_DQ13 | IO_L10P_35 | J5 |

| DDR3_DQ14 | IO_L7P_35 | K1 |

| DDR3_DQ15 | IO_L12P_35 | H4 |

| DDR3_DM1 | IO_L8N_35 | G2 |

| DDR3_DQS_P1 | IO_L9P_35 | K2 |

| DDR3_DQS_N1 | IO_L9N_35 | J2 |

| DDR3_DQ16 | IO_L18N_35 | L4 |

| DDR3_DQ17 | IO_L16P_35 | M3 |

| DDR3_DQ18 | IO_L14P_35 | L3 |

| DDR3_DQ19 | IO_L17N_35 | J6 |

| DDR3_DQ20 | IO_L14N_35 | K3 |

| DDR3_DQ21 | IO_L17P_35 | K6 |

| DDR3_DQ22 | IO_L13N_35 | J4 |

| DDR3_DQ23 | IO_L18P_35 | L5 |

| DDR3_DM2 | IO_L16N_35 | M2 |

| DDR3_DQS_P2 | IO_L15P_35 | M1 |

| DDR3_DQS_N2 | IO_L15N_35 | L1 |

| DDR3_DQ24 | IO_L20N_35 | P1 |

| DDR3_DQ25 | IO_L19P_35 | N4 |

| DDR3_DQ26 | IO_L20P_35 | R1 |

| DDR3_DQ27 | IO_L22N_35 | N2 |

| DDR3_DQ28 | IO_L23P_35 | M6 |

| DDR3_DQ29 | IO_L24N_35 | N5 |

| DDR3_DQ30 | IO_L24P_35 | P6 |

| DDR3_DQ31 | IO_L22P_35 | P2 |

| DDR3_DM3 | IO_L23N_35 | M5 |

| DDR3_DQS_P3 | IO_L21P_35 | P5 |

| DDR3_DQS_N3 | IO_L21N_35 | P4 |

| DDR3_A0 | IO_L11N_34 | AA4 |

| DDR3_A1 | IO_L8N_34 | AB2 |

| DDR3_A2 | IO_L10P_34 | AA5 |

| DDR3_A3 | IO_L10N_34 | AB5 |

| DDR3_A4 | IO_L7N_34 | AB1 |

| DDR3_A5 | IO_L6P_34 | U3 |

| DDR3_A6 | IO_L5P_34 | W1 |

| DDR3_A7 | IO_L1P_34 | T1 |

| DDR3_A8 | IO_L2N_34 | V2 |

| DDR3_A9 | IO_L2P_34 | U2 |

|---|---|---|

| DDR3_A10 | IO_L5N_34 | Y1 |

| DDR3_A11 | IO_L4P_34 | W2 |

| DDR3_A12 | IO_L4N_34 | Y2 |

| DDR3_A13 | IO_L1N_34 | U1 |

| DDR3_A14 | IO_L15N_34 | W5 |

| DDR3_BA0 | IO_L9N_34 | AA3 |

| DDR3_BA1 | IO_L9P_34 | Y3 |

| DDR3_BA2 | IO_L11P_34 | Y4 |

| DDR3_nCS | IO_L8P_34 | AB3 |

| DDR3_nWE | IO_L7P_34 | AA1 |

| DDR3_nRESET | IO_L15P_34 | W6 |

| DDR3_CLK_P | IO_L3P_34 | R3 |

| DDR3_CLK_N | IO_L3N_34 | R2 |

| DDR3_nWE | IO_L7P_34 | AA1 |

| DDR3_nRAS | IO_L12P_34 | V4 |

| DDR3_nCAS | IO_L12N_34 | W4 |

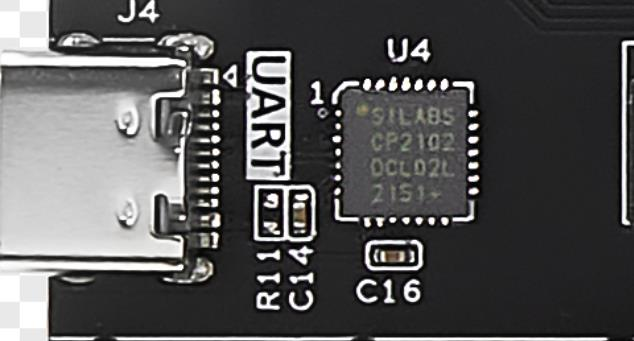

[]() 3.7.USB********轉串口

開發板使用CH340E 芯片實現 USB 轉 UART, USB 接口采用 TypeC 接口,用戶只要 用一根 USB 線連接到 PC 上即可進行串口通信。

UART 的 TX/RX 信號與 FPGA 的 BANK14 相連,接口電平為 3.3V。 如下是信號對應 關系表和原理圖。

| UART********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| UART_TX | IO_L22P_14 | P15 |

| UART_RX | IO_L19P_14 | P14 |

?編輯

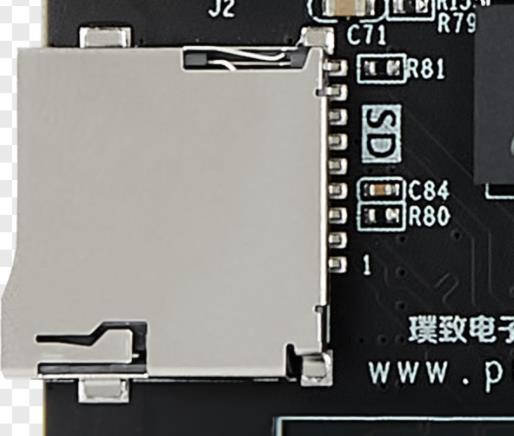

[]()3.8.SD********卡

開發板上放置了一個 SD 卡座(開發板背面), SD 卡信號連接到 FPGA 的 BANK14 上,接口電平為 3.3V。如下是信號對應關系,詳細電路可以參考開發板原理圖。

| SD********卡引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| SD-CLK | IO_L8P_14 | AA20 |

| SD-CMD | IO_L10P_14 | AB21 |

| SD-DATA0 | IO_L17N_14 | AB18 |

| SD-DATA1 | IO_L17P_14 | AA18 |

| SD-DATA2 | IO_L10N_14 | AB22 |

| SD-DATA3 | IO_L8N_14 | AA21 |

?編輯

[]()3.9.E2********PROM

開發板上放置了一顆 64Kbit 的 EEPROM 芯片,型號為 AT24C64D-SSHM-T,E2PROM 通過 IIC 擴展芯片與 FPGA 的 BANK14 相連,接口電平為 3.3V。EEPROM 讀地址是 0xA1, 寫地址是 0xA0。操作代碼可參考璞致提供的例程,詳細電路可以參考開發板原理圖。

| E2********PROM | 管腳名稱 | 管腳位置 |

|---|---|---|

| E2PROM_I2C_SCL | IO_L23P_14 | N13 |

| E2PROM_I2C_SDA | IO_L23N_14 | N14 |

?編輯

[]()3.10.千兆以太網

開發板上設計了一路千兆以太網,以太網芯片與 FPGA 之間通過 RGMII 接 口互聯,連接 BANK14,接口電平是 1.8V,連接對應管腳見下表,網口地址是 PHY_AD[2:0]=001,詳細電路可以參考開發板原理圖。

| RMGII********信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| GPHY_TX_CLK | IO_L21N_14 | P17 |

| GPHY_TX_EN | IO_L22N_14 | R16 |

| GPHY_TXD0 | IO_L5P_14 | P19 |

| GPHY_TXD1 | IO_L24P_14 | P16 |

| GPHY_TXD2 | IO_L21P_14 | N17 |

| GPHY_TXD3 | IO_L24N_14 | R17 |

| GPHY_RX_CLK | IO_L12P_14 | W19 |

| GPHY_RX_DV | IO_L12N_14 | W20 |

| GPHY_RXD0 | IO_L18N_14 | U18 |

| GPHY_RXD1 | IO_L5N_14 | R19 |

| GPHY_RXD2 | IO_L20P_14 | R18 |

| GPHY_RXD3 | IO_L0_14 | P20 |

| GPHY_MDC | IO_L20N_14 | T18 |

| GPHY_MDIO | IO_L25_14 | N15 |

| GPHY_nRST | IO_L6N_14 | T20 |

?編輯

[]() 3.11.HDMI********接口

開發板設計了一路 HMDI 輸出接口,管腳定義如下表,詳細電路可以參考開發板 原理圖。

| HDMI********信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| HDMI_DATA0_P | IO_L14P_14 | V18 |

| HDMI_DATA0_N | IO_L14N_14 | V19 |

| HDMI_DATA1_P | IO_L15P_14 | AA19 |

| HDMI_DATA1_N | IO_L15N_14 | AB20 |

| HDMI_DATA2_P | IO_L16P_14 | V17 |

| HDMI_DATA2_N | IO_L16N_14 | W17 |

| HDMI_CLK_P | IO_L13P_14 | Y18 |

|---|---|---|

| HDMI_CLK_N | IO_L13N_14 | Y19 |

| HDMI_CEC | IO_L18P_14 | W22 |

| HDMI_I2C_SCL | IO_L4P_14 | T21 |

| HDMI_I2C_SDA | IO_L11P_14 | U20 |

?

?

編輯

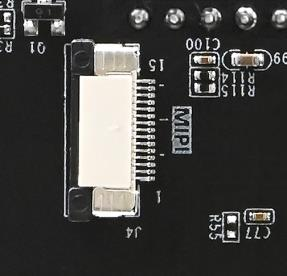

[]()3.12.MIPI********接口

開發板設計了一路 MIPI 接口,管腳定義如下表,詳細電路可以參考開發板原理 圖。

| MIPI********信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| MIPI_LP_DATA_P0 | IO_L10P_13 | V10 |

| MIPI_LP_DATA_N0 | IO_L10N_13 | W10 |

| MIPI_LP_DATA_P1 | IO_L9P_13 | AA10 |

| MIPI_LP_DATA_N1 | IO_L9N_13 | AA11 |

| MIPI_DATA_P0 | IO_L12P_13 | W11 |

| MIPI_DATA_N0 | IO_L12N_13 | W12 |

| MIPI_DATA_P1 | IO_L11P_13 | Y11 |

| MIPI_DATA_N1 | IO_L11N_13 | Y12 |

| MIPI_LP_CLK_P | IO_L14P_13 | U15 |

| MIPI_LP_CLK_N | IO_L14N_13 | V15 |

| MIPI_CLK_P | IO_L13P_13 | V13 |

| MIPI_CLK_N | IO_L13N_13 | V14 |

| MIPI_CAM_nRST | IO_L15N_13 | T15 |

| MIPI_CAM_CLK | IO_L15P_13 | T14 |

| MIPI_IIC_SCL | IO_L16P_13 | W15 |

| MIPI_IIC_SDA | IO_L16N_13 | W16 |

?編輯

[]()3.13.LED

開發板設計了兩路 LED。LED 高電平亮,低電平滅。詳細電路可參考開發板原理 圖。

| LED********位號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LED1 | IO_L7N_14 | W22 |

| LED2 | IO_L9N_14 | Y22 |

?編輯

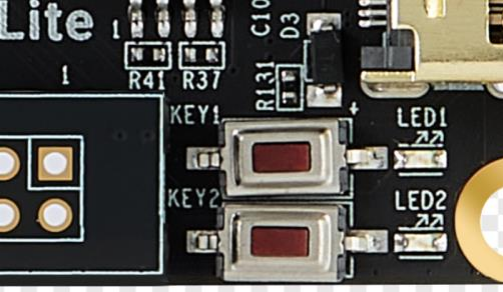

[]()3.14.按鍵

開發板設計了兩路用戶按鍵,一路復位按鍵。按鍵默認高電平,按下為低電平, 按鍵連到 PL 側,管腳位置如下表。

| 按鍵位號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| KEY1 | IO_L7P_14 | W21 |

| KEY2 | IO_L9P_14 | Y21 |

?編輯

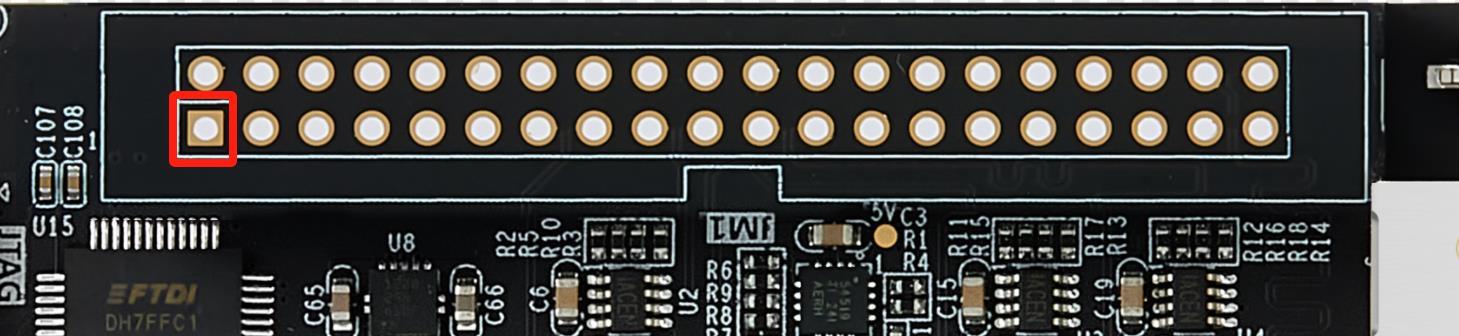

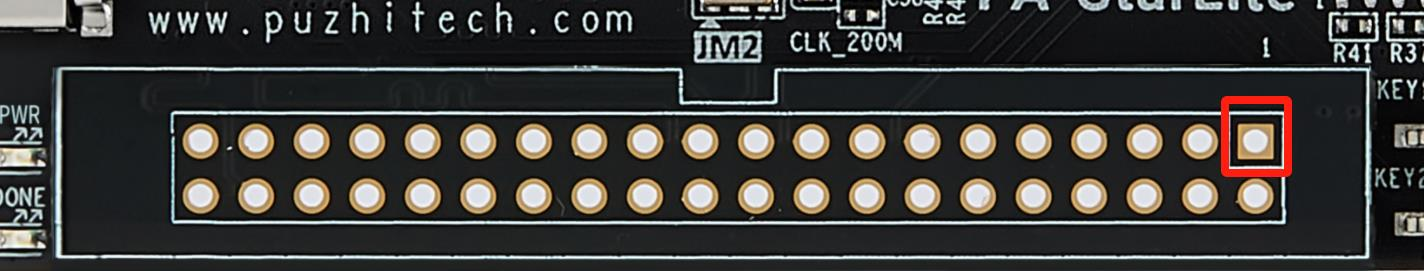

[]()3.15.40P********擴展口

開發板設計了一個 40P 2.54mm 間距的簡易牛角座,用于擴展信號的連接,信號 與 FPGA 的 BANK15/16 連接,電平為 3.3V。如下表標出了信號所在的芯片位置,詳細 連接關系參考原理圖部分,1腳位置已標注。

| JM1信號順序 | 管腳名稱 | 管腳位置 | JM1信號順序 | 管腳名稱 | 管腳位置 |

|---|---|---|---|---|---|

| 5 | IO_L5P_16 | E16 | 6 | IO_L1P_16 | F13 |

| 7 | IO_L5N_16 | D16 | 8 | IO_L1N_16 | F14 |

15 / 17

| 9 | IO_L8P_16 | C13 | 10 | IO_L6P_16 | D14 |

|---|---|---|---|---|---|

| 11 | IO_L8N_16 | B13 | 12 | IO_L6N_16 | D15 |

| 13 | IO_L10P_16 | A13 | 14 | IO_L3P_16 | C14 |

| 15 | IO_L10N_16 | A14 | 16 | IO_L3N_16 | C15 |

| 17 | IO_L9P_16 | A15 | 18 | IO_L4P_16 | E13 |

| 19 | IO_L9N_16 | A16 | 20 | IO_L4N_16 | E14 |

| 21 | IO_L11P_SRCC_16 | B17 | 22 | IO_L7P_16 | B15 |

| 23 | IO_L11N_SRCC_16 | B18 | 24 | IO_L7N_16 | B16 |

| 25 | IO_L12P_MRCC_16 | D17 | 26 | IO_L2P_16 | F16 |

| 27 | IO_L12N_MRCC_16 | C17 | 28 | IO_L2N_16 | E17 |

| 29 | IO_L13P_MRCC_16 | C18 | 30 | IO_L15P_16 | F18 |

| 31 | IO_L13N_MRCC_16 | C19 | 32 | IO_L15N_16 | E18 |

| 37 | IO_L14P_SRCC_16 | E19 | 38 | IO_L16P_16 | B20 |

| 39 | IO_L14_SRCC_N_16 | D19 | 40 | IO_L16N_16 | A20 |

?編輯

| JM2 信號順序 | 管腳名稱 | 管腳位置 | JM2 信號順序 | 管腳名稱 | 管腳位置 |

|---|---|---|---|---|---|

| 5 | IO_L4P_15 | G17 | 6 | IO_L15P_15 | N22 |

| 7 | IO_L4N_15 | G18 | 8 | IO_L15N_15 | M22 |

| 9 | IO_L2P_15 | G15 | 10 | IO_L6P_15 | H17 |

| 11 | IO_L2N_15 | G16 | 12 | IO_L6N_15 | H18 |

| 13 | IO_L3P_15 | J14 | 14 | IO_L5P_15 | J15 |

| 15 | IO_L3N_15 | H14 | 16 | IO_L5N_15 | H15 |

| 17 | IO_L1P_15 | H13 | 18 | IO_L10P_15 | M21 |

| 19 | IO_L1N_15 | G13 | 20 | IO_L10N_15 | L21 |

| 21 | IO_L11P_SRCC_15 | J20 | 22 | IO_L8P_15 | H20 |

| 23 | IO_L11N_SRCC_15 | J21 | 24 | IO_L8N_15 | G20 |

| 25 | IO_L12P_MRCC_15 | J19 | 26 | IO_L9P_15 | K21 |

| 27 | IO_L12N_MRCC_15 | H19 | 28 | IO_L9N_15 | K22 |

| 29 | IO_L13P_MRCC_15 | K18 | 30 | IO_L7P_15 | J22 |

| 31 | IO_L13N_MRCC_15 | K19 | 32 | IO_L7N_15 | H22 |

| 37 | IO_L14P_SRCC_15 | L19 | 38 | IO_L16P_15 | M18 |

| 39 | IO_L14N_SRCC_15 | L20 | 40 | IO_L16N_15 | L18 |

?編輯

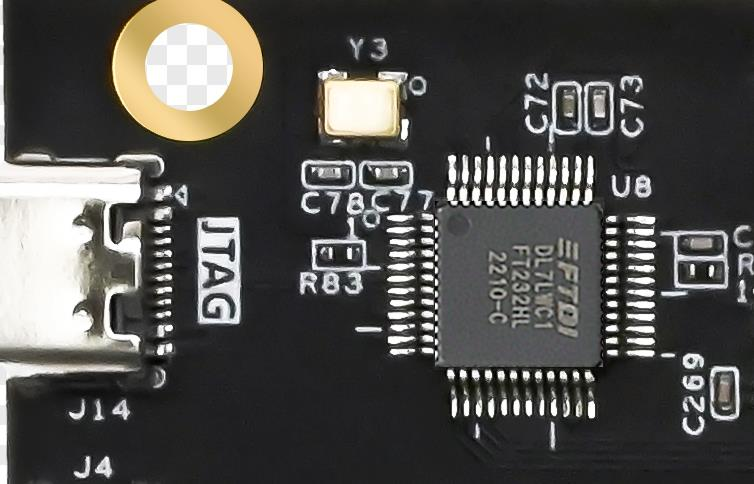

[]() 3.16.USB轉JTAG********下載器

開發板板載了一個 USB 轉 JTAG 下載器,安裝好 Vivado 軟件后使用USB 線連接好 JTAG 對應的 USB 口,即可實現調試下載,非常方便。如下是接口在開發板上的位置 圖。

?編輯

?審核編輯 黃宇

-

FPGA

+關注

關注

1662文章

22469瀏覽量

638152 -

Xilinx

+關注

關注

73文章

2204瀏覽量

131673 -

FPGA開發板

+關注

關注

10文章

130瀏覽量

32495

發布評論請先 登錄

新品!從MINI到工業板:米爾T153開發板工業場景全覆蓋

【ALINX 教程】FPGA Multiboot 功能實現——基于 ALINX Artix US+ AXAU25 開發板

Renesas RX66T 開發板:功能、配置與使用指南

Renesas FPB - RA2T1快速原型開發板:開啟高效設計之旅

請問如何將蜂鳥E203移植到Xilinx NEXYS A7 FPGA 開發板上?

蜂鳥E203在黑金XC7A200T型FPGA上的移植工作

基于FPGA開發板DE10-Standard和T-Core的串口通信設計

fpga開發板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開發板用戶手冊

【作品合集】合眾HZ-T536開發板測評

【PZ7020-StarLite 入門級開發板】——FPGA 開發的理想起點,入門與工業場景的雙重優選

【HZ-T536開發板免費體驗】開箱評測

基于米爾全志T536開發板的多協議物聯網關的方案測試

fpga開發板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T開發板用戶手冊-學習板

fpga開發板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T開發板用戶手冊-學習板

評論