PCIe(Peripheral Component Interconnect Express)信號完整性問題可能導致數據傳輸錯誤、系統不穩定甚至完全失效。以下是一些針對PCIe信號完整性問題的解決方案:

一、檢查和優化硬件連接

- 確保連接器和插槽正確接觸 :

- 檢查PCIe設備(如顯卡、固態硬盤等)與主板上的PCIe插槽之間的連接是否牢固,確保所有連接器都正確插入且沒有物理損傷。

- 使用高質量的材料和工藝 :

- 選擇高質量的PCIe插槽和連接器,確保它們具有良好的導電性和耐久性。

- 使用高質量的電路板材料,以減少信號路徑上的阻抗不匹配和信號損失。

- 優化線路布局和設計 :

- 分析線路布局和設計,確保信號路徑適合高速操作。

- 如果可能,縮短信號路徑,以減少信號衰減和干擾。

- 避免高速信號走線并行,以減少串擾。

二、電源管理和噪聲抑制

- 檢查電源供應是否穩定 :

- 使用電源分析儀測量供電線路的噪聲,確保電源供應穩定且沒有過多的噪聲干擾。

- 使用電源濾波器 :

- 在電源輸入端添加電源濾波器,以抑制電源噪聲和干擾。

- 確保設備在推薦的溫度范圍內操作 :

- 高溫可能導致設備性能下降和信號質量惡化,因此應確保設備在推薦的工作溫度范圍內操作。

三、信號再生和補償

- 使用Retimer芯片 :

- Retimer芯片通過對信號的重定時和均衡,可以恢復衰減信號的幅度和質量,從而減小信號失真。

- Retimer還能夠補償鏈路插損,延長傳輸距離,確保數據傳輸的穩定性、完整性和低延遲表現。

- 優化端接和電路設計 :

- 采用適當的端接方式(如片內端接On Die Termination,簡稱ODT),以消除信號反射。

- 優化電路設計,以減少電源噪聲和串擾對信號質量的影響。

四、軟件配置和更新

- 檢查BIOS或固件設置 :

- 確保BIOS或固件設置正確,PCIe插槽已啟用。

- 檢查是否有與PCIe設備相關的配置錯誤或沖突,并進行必要的調整。

- 更新驅動程序和固件 :

- 確保PCIe設備的驅動程序和固件是最新版本,以兼容最新的操作系統和硬件。

- 驅動程序和固件的更新可以解決一些與硬件兼容性和性能相關的問題。

五、故障排除和診斷

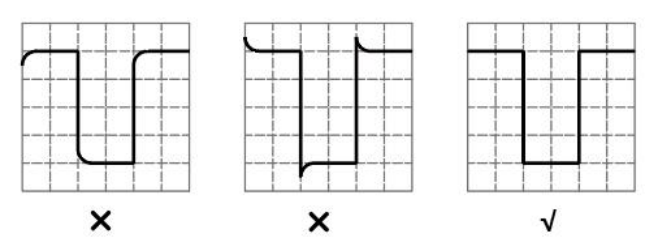

- 使用TDR(時域反射儀)檢查阻抗匹配情況 :

- TDR可以幫助識別信號路徑上的阻抗不匹配點,從而指導解決阻抗不匹配問題。

- 進行誤碼率測試 :

- 使用測試設備對PCIe信號進行誤碼率測試,確保誤碼率在可接受范圍內。

- 如果誤碼率超標,應進一步排查信號完整性問題。

- 檢查時鐘同步 :

- 確保時鐘源準確、無漂移,并且與所有設備同步。

- 時鐘同步問題可能導致數據傳輸錯誤和信號完整性問題。

綜上所述,解決PCIe信號完整性問題需要從硬件連接、電源管理、信號再生和補償、軟件配置以及故障排除和診斷等多個方面入手。通過綜合運用這些解決方案,可以顯著提高PCIe信號的穩定性和可靠性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

連接器

+關注

關注

104文章

16139瀏覽量

147038 -

數據傳輸

+關注

關注

9文章

2201瀏覽量

67582 -

信號完整性

+關注

關注

68文章

1486瀏覽量

98099 -

PCIe

+關注

關注

16文章

1461瀏覽量

88418

發布評論請先 登錄

相關推薦

熱點推薦

IDT信號完整性產品:解決高速信號傳輸難題

特性的影響,到達終端接收器時可能會惡化到不可接受的水平。Integrated Device Technology(IDT)的信號完整性產品(SIP)系列,包括中繼器(Repeaters)和重定時器(Retimers),為解決這些問題提供了有效的

PK6350無源探頭在高速數字總線信號完整性測試中的應用案例

一、應用背景 在現代電子設備架構中,PCIe、USB 3.0等高速數字總線是實現數據高速傳輸的核心載體,其信號完整性測試已成為保障設備性能穩定性與運行可靠性的關鍵環節。隨著數據傳輸速率的持續攀升

Cadence工具如何解決芯粒設計中的信號完整性挑戰

在芯粒設計中,維持良好的信號完整性是最關鍵的考量因素之一。隨著芯片制造商不斷突破性能與微型化的極限,確保組件間信號的純凈性與可靠性面臨著前所未有的巨大挑戰。對于需要應對信號

技術資訊 I 信號完整性與阻抗匹配的關系

本文要點PCB走線和IC走線中的阻抗控制主要著眼于預防反射。防止互連路徑上發生反射,可確保功率傳輸至負載,同時避免其他信號完整性問題。使用集成場求解器的PCB設計軟件可以評估阻抗匹配并提取互連網

了解信號完整性的基本原理

作者:Cece Chen 投稿人:DigiKey 北美編輯 隨著支持人工智能 (AI) 的高性能數據中心的興起,信號完整性 (SI) 變得至關重要,這樣才能以更高的速度傳輸海量數據。為確保信號

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

前言 在這一期的Samtec虎家大咖說節目中,Samtec信號完整性(SI)和電源完整性(PI)專家Scott McMorrow、Rich Mellitz和Istvan Novak回答了觀眾的提問

發表于 05-14 14:52

?1196次閱讀

受控阻抗布線技術確保信號完整性

核心要點受控阻抗布線通過匹配走線阻抗來防止信號失真,從而保持信號完整性。高速PCB設計中,元件與走線的阻抗匹配至關重要。PCB材料的選擇(如低損耗層壓板)對減少信號衰減起關鍵作用。受控

信號完整性測試基礎知識

在當今快速發展的數字時代,高速傳輸已成為電子設備的基本要求。隨著數據傳輸速率的不斷提升,信號完整性(Signal Integrity,簡稱SI)問題變得越來越重要。信號完整性是高速互連

普源示波器在信號完整性分析中的應用研究

信號完整性(Signal Integrity, SI)是電子工程領域中一個至關重要的概念,它指的是信號在傳輸過程中保持其原始特征的能力。在高速數字電路和通信系統中,信號

PCIe信號完整性問題解決方案

PCIe信號完整性問題解決方案

評論