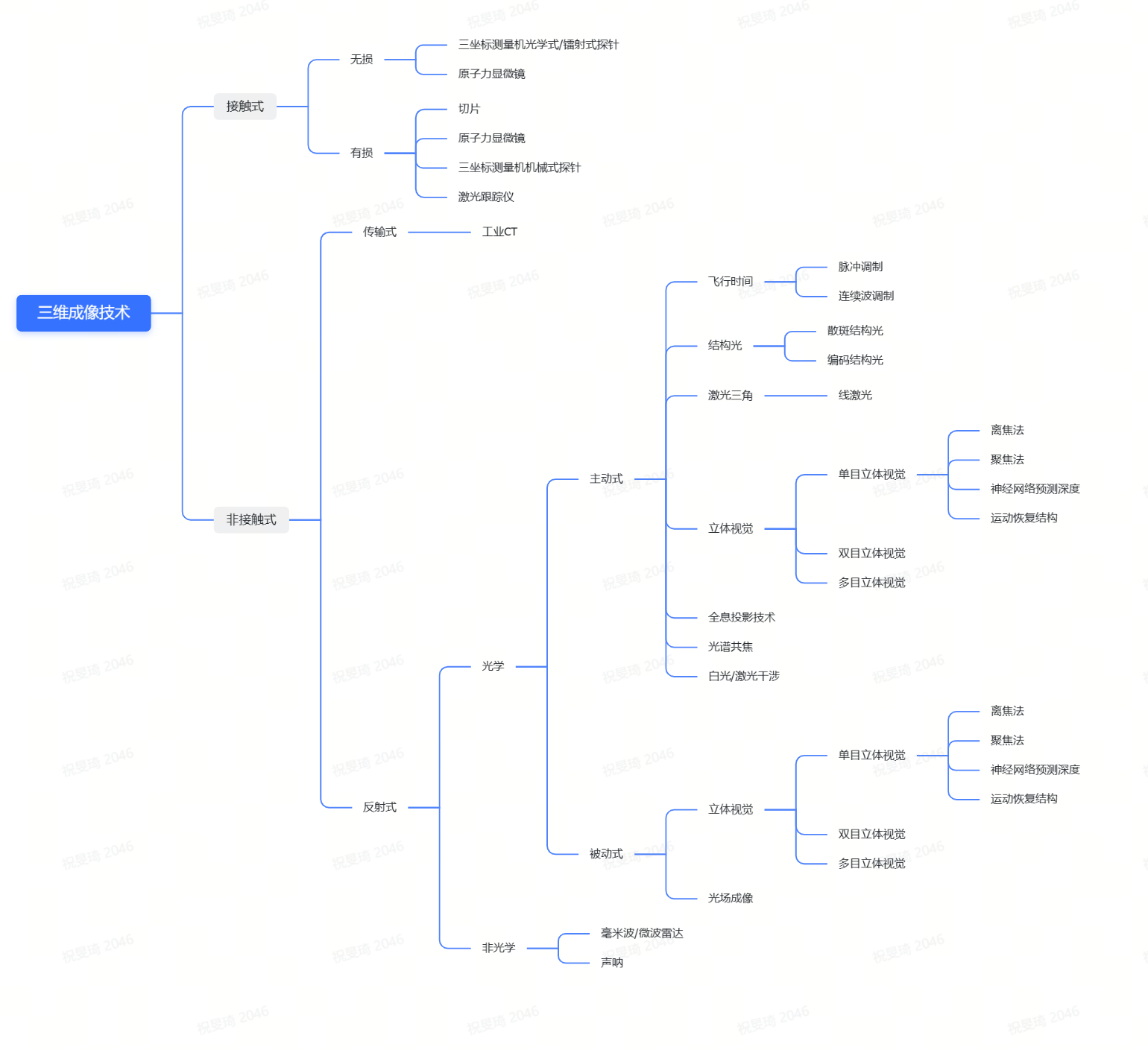

本文回顧了過去的封裝技術、介紹了三維集成這種新型封裝技術,以及TGV工藝。

一、半導體技術發展趨勢

以集成電路芯片為代表的微電子技術不僅在信息社會的發展歷程中起到了關鍵性作用,也在5G通信、人工智能等前沿科技領域和無人駕駛、物聯網等新興應用領域扮演著至關重要的角色。

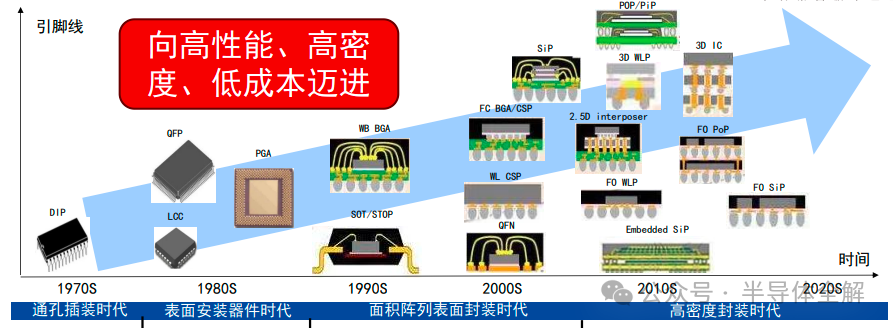

電子元器件逐步向著低成本、小型化、高度集成化的方向發展。這也要求集成電路技術(Integratedcircuit, IC)應該具有更高的I/O密度和更短的線寬、線距來提高芯片集成度。

目前最前沿的光刻技術已進入到3-5nm階段且后續尺寸縮小進展緩慢,芯片特征尺寸開始接近物理極限。過去微電子技術的發展歷程,性能的提升很大程度上依賴于光刻技術的進步所帶來的晶體管特征尺寸的減小。然而近年來隨著技術節點的不斷演進,晶體管的特征尺寸已逐漸逼近物理極限,想要繼續延續“摩爾定律”縮減特征尺寸越來越困難。

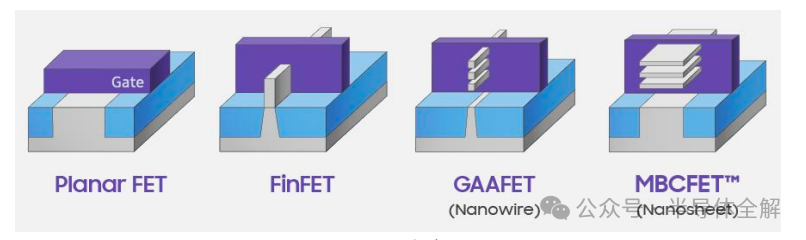

為了繼續提升集成電路性能,半導體產業界近年來一方面繼續減小晶體管特征尺寸,通過改進制造工藝來提升晶體管性能。

其中,鰭式場效應管(FinFET)及其衍生技術自22nm技術節點以來在晶體管特征尺寸的縮減中扮演了重要角色。如圖所示,相比于傳統平面型晶體管,FinFET晶體管的柵極對溝道形成了三面環繞,從而增強了柵電壓對溝道載流子的調控能力,減小了漏電流,提升了晶體管的電性能。

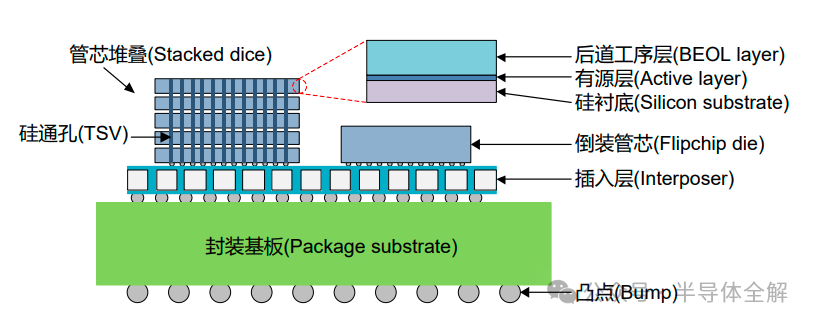

另一方面是采用新型封裝技術來提升集成電路的整體性能,例如系統級封裝(SiP)、三維集成(3-D integration)等通過將多層管芯(die)垂直堆疊,并使用硅通孔(TSV)實現管芯間的垂直互連,可大幅減小全局互連長度,從而減小延時和功耗,提升集成電路的整體性能。

接下來可以看下二維封裝到三維封裝的技術演變。

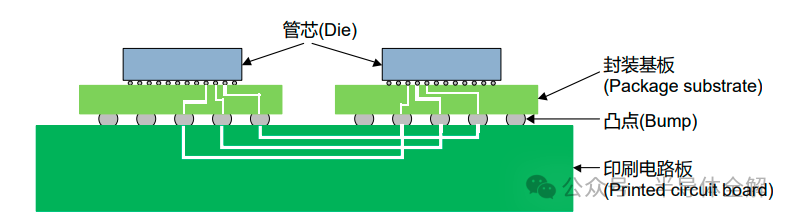

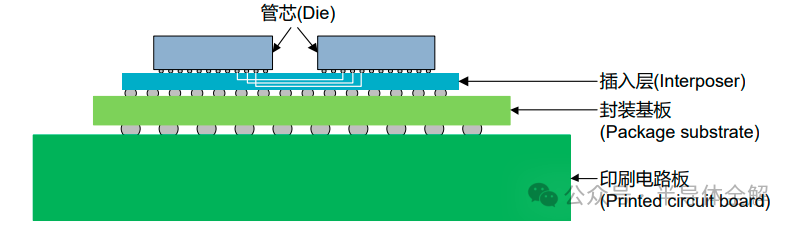

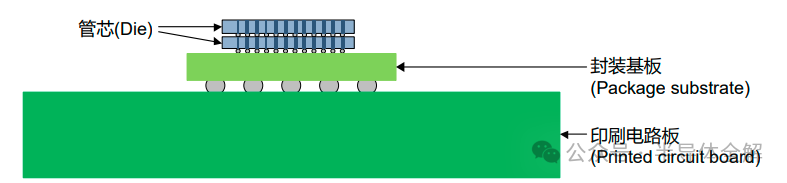

下圖是傳統二維封裝方式:

下圖是SIP(系統級封裝)方式:

下圖是三維集成封裝方式:

其中,三維集成是非常有潛力的一種新型封裝技術,近年來逐漸在實際產品中得到應用。

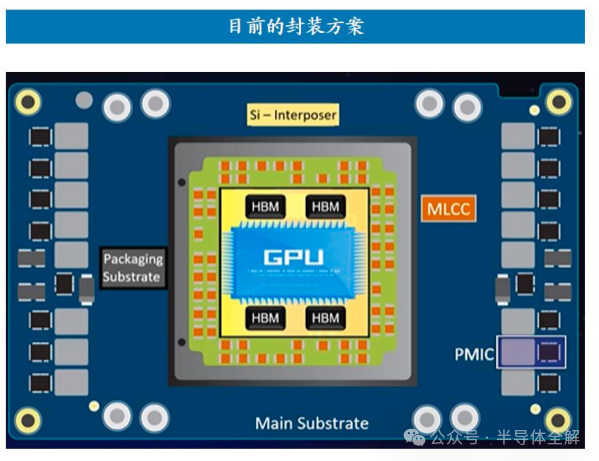

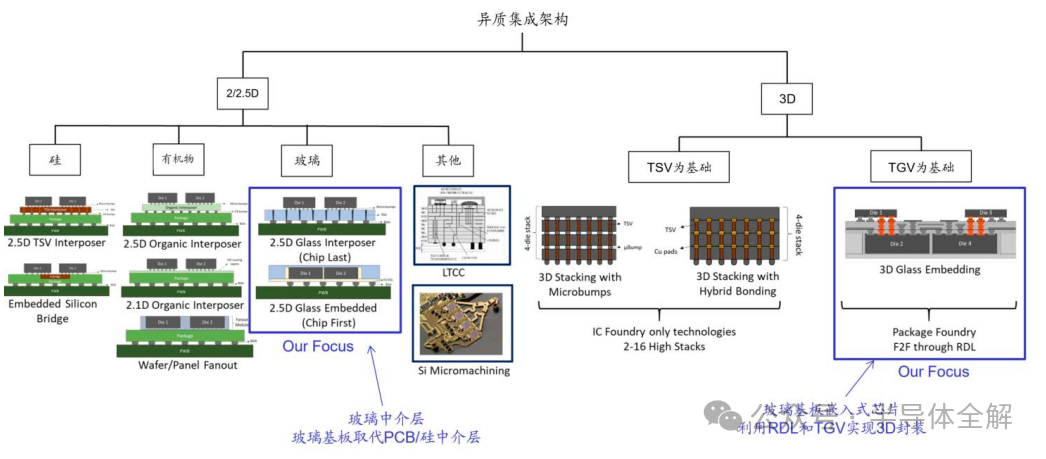

2.5D/3D先進封裝技術是芯片系統關于延續摩爾定律的有效解決方案之一,該技術主要目的是通過在垂直方向上堆疊芯片以實現更高密度的集成。

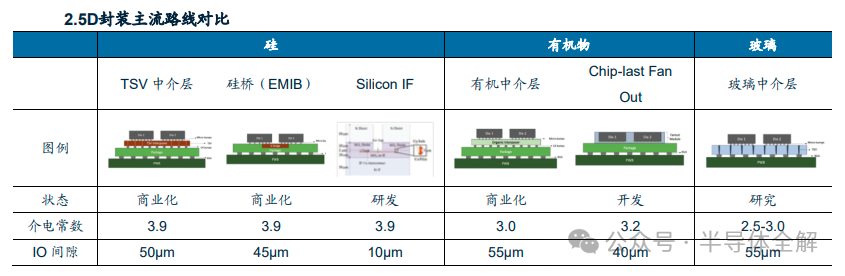

其中,3D封裝技術與2.5D封裝技術的差別主要在于3D封裝技術是通過硅通孔(Through Silicon Via, TSV)或玻璃通孔(Through Glass Via, TGV)把所有芯片都垂直連接,而2.5D封裝技術指的是將多個芯片平鋪在中介層上,中介層上有再布線層,用于芯片間的水平互連,而中介層再通過通孔把芯片與封裝基板相連,進而實現多個芯片的垂直互連,這種將多種不同材質、尺寸、功能封裝到一個系統內的技術也被稱作三維異質集成技術,其中實現中介層互連功能的關鍵工藝則是相應的通孔制備及孔金屬化。

2.5D封裝技術的關鍵之一是轉接板為主要構成的中介層,目前轉接板根據材料的不同有玻璃基、硅基、有機物三種類型,其中硅基轉接板技術相對成熟,已經在實際生產中實現應用,然而硅基轉接板在實際應用中存在高頻損耗高和成本昂貴等問題,因此人們開始尋找硅的替代品。

現在硅基轉接板最有潛力的替代者是玻璃基轉接板,玻璃基轉接板的優勢在于它是絕緣體,高電阻不僅帶來了更低的高頻損耗以及更少的信號串擾,還可以避免制備介質層,降低了工藝難度;其次玻璃的熱膨脹系數接近硅,這使得玻璃中介層與硅芯片構成的系統有著比有機中介層更高的熱穩定性和機械穩定性,提高了可靠性;最后是玻璃表面光滑平整,這對于高密度布線而言是十分重要的。

二、先進封裝技術

當前集成電路產品中很可能同時使用了三維集成技術和FinFET技術。

如圖所示為當前一種典型的三維集成技術場景——高帶寬內存(HBM),其中多層管芯堆疊之間的垂直互連由硅通孔實現,各層管芯的有源電路則可能是基于FinFET工藝制造。

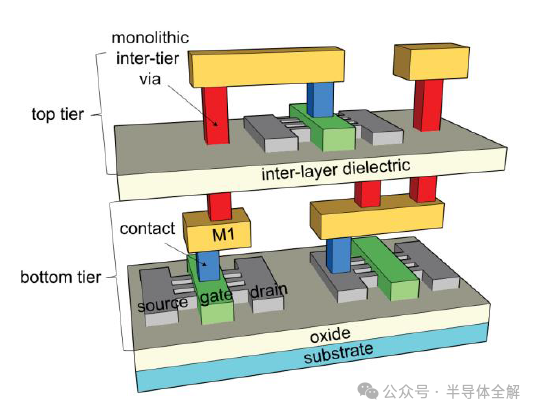

下圖為新興的單片三維集成(monolithic 3-D integration)技術,其中使用單片層間過孔來實現多層FinFET有源器件的互連,以實現更高的性能和更小的尺寸。其中,上下層Tier 之間由單片層間過孔(MIVs)實現互連。

由此可見,通過硅通孔實現垂直互連,每層管芯中的有源電路則可能是基于FinFET工藝制造,堆疊的管芯與倒裝管芯之間通過插入層實現互連。

此外,在以印制電路板(Printed circuit boards, PCB)為主要構成的外界系統方面,提高集成度的方案是高密度互連技術(High Density Interconnection, HDI)。

這種技術通過通孔、盲孔、埋孔的共同作用實現多層布線以及層間互連,以此來滿足器件小型化和高度集成化的需求。

孔金屬化過程主要包括制備金屬種子層和電鍍填孔兩個部分,其中金屬種子層的作用是使不導電基板覆蓋一層導體達到導電效果,金屬種子層的連續性及完整性是孔導通兩端、實現電信號互連的基礎。

三、TGV工藝介紹

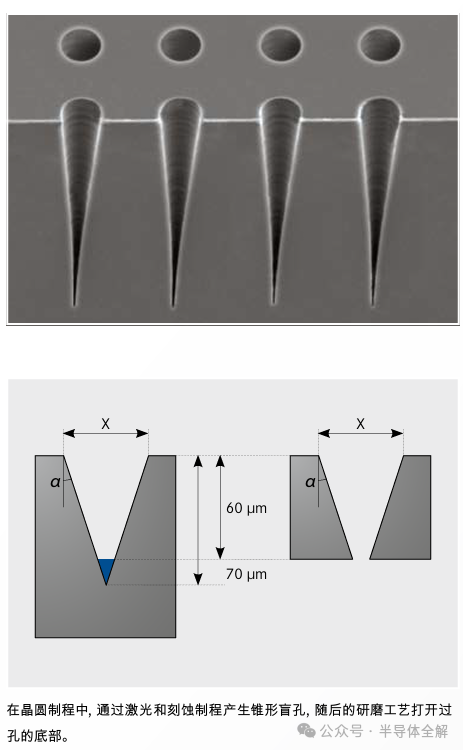

制備TGV玻璃通孔的方式很多,包括有噴砂工藝、超聲波鉆孔(ultra-sonic drilling, USD)、激光誘導深度刻蝕(laser induced deep etching, LIDE)等方法,其中應用最為廣泛的是激光誘導深度刻蝕的方法。

激光誘導深度刻蝕采用的超快激光光源,超快激光加工最顯著的特征就是熱影響區域小。對于傳統激光而言,由于使用的激光脈沖寬度達到納秒量級甚至更長,聚焦后的光斑為微米量級,因此在加工過程中,熱擴散現象非常明顯,嚴重影響加工精度。而超快激光的脈沖寬度非常窄,因此當超快激光作用在材料表面時,它的短脈沖時間意味著能量密度非常高,能夠在非常短的時間內將能量局部集中在材料表面上。由于能量密度非常高,材料瞬間被加熱到極高溫度,于是材料就被以汽相形式蒸發,并且會帶走部分材料內部的熱量,使得周圍區域的溫度變化非常小,所以周圍熱影響區域很小。

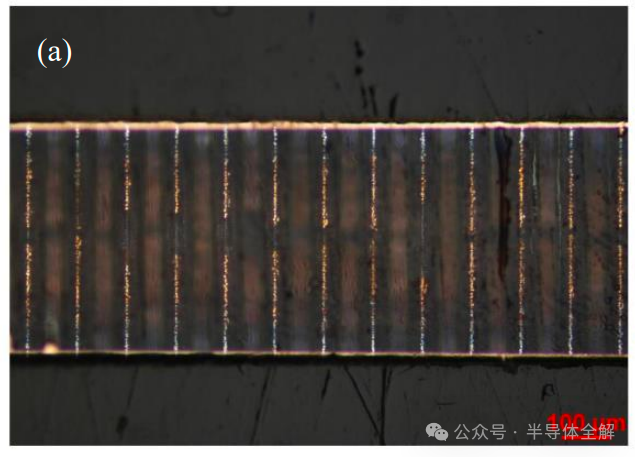

該方法采用不同頻率,不同聚焦類型的激光在玻璃上打出孔徑在1μm以下的小孔,之后在以氫氟酸為主要構成的刻蝕液中濕法刻蝕特定時間來制備相應大小的TGV。

該方法目前可以制備的TGV側壁垂直度和深寬比范圍廣,典型的TGV深寬比為1:10。此外,該制備方案還可以制備玻璃盲孔,經過金屬填充后的玻璃盲孔可以實現信號屏蔽的功能,在特定器件上起到關鍵性作用。

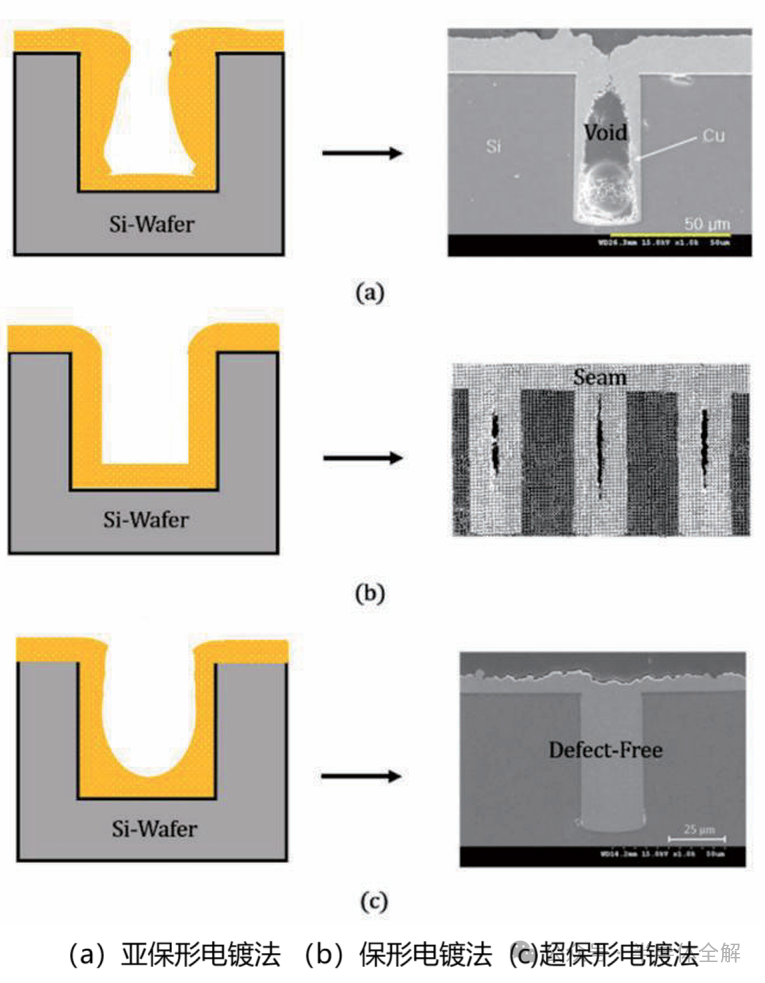

TGV的金屬化主要包括有制備金屬種子層和電鍍填孔兩個部分,其中電鍍填孔主要與孔的形狀、施加電流類型以及鍍液內的添加劑成分有著較強的關聯性。

制備金屬種子層則是TGV實現三維互連的關鍵技術之一,一方面金屬種子層是導電層進行電鍍的基礎,缺失了種子層的位置無法導電進行電鍍。另一方面,因為交流電環境下電流具有趨膚效應,大部分電流都會通過種子層進行流通,因此一個完整連續的金屬種子層對于TGV金屬化而言十分重要的。

四、TGV金屬化工藝

金屬種子層制備方式包括物理氣相沉積(Physical vapor deposition, PVD)、化學氣相沉積(Chemical vapor deposition, CVD)、原子層沉積(Atomic layer deposition, ALD)、化學鍍(Electroless plating)等,其中最常用于TGV金屬化的是磁控濺射工藝,該工藝是PVD工藝的一種。

磁控濺射技術

典型的磁控濺射工藝需要先在基板上濺射Ti、Ta及其氮化物作為阻擋層,在阻擋電鍍的Cu擴散至襯底的同時還作為粘附層加強Cu和玻璃間的結合力,這種方法在物件表面制備的薄膜均勻性好,沉積速率適中。

參考文獻

(1)閔球三維封裝集成電路中的電熱特性分析研究[D].

(2)龍致遠電子互連微孔金屬化方法及機理研究[D].

(3)王紫任高速電路與電子封裝中電連接故障對信號完整性影響研究[D].

(4)廣發證券半導體設備行業系列研究:玻璃基板從零到一,TGV為關鍵工藝[C].

(5)東方財富證券Chiplet與先進封裝共塑后摩爾時代半導體產業鏈新格局[C].

(6)華金證券 走進“芯”時代系列深度之六十七“25D、3D封裝”[C].

-

芯片

+關注

關注

463文章

54010瀏覽量

466175 -

封裝

+關注

關注

128文章

9249瀏覽量

148639

原文標題:一文了解芯片三維封裝(TSV及TGV)技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

OFDR技術與三維重構的協同價值

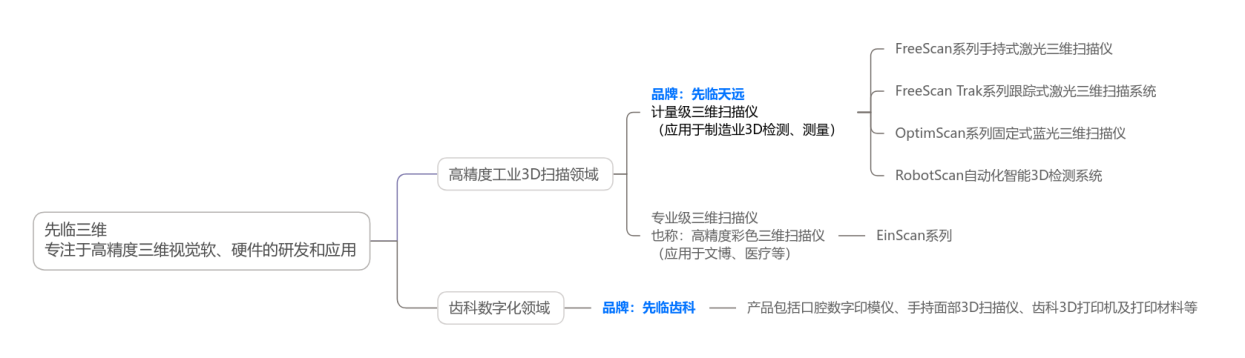

一文讀懂 | 三維視覺領域國家級制造業單項冠軍——先臨三維的品牌布局

TSV和TGV產品在切割上的不同難點

一文了解芯片三維封裝(TSV及TGV)技術

一文了解芯片三維封裝(TSV及TGV)技術

評論