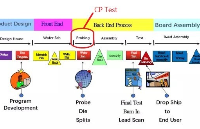

在集成電路(IC)制造與測試過程中,CP(Chip Probing,晶圓探針測試)和FT(Final Test,最終測試)是兩個重要的環(huán)節(jié),它們承擔了不同的任務,使用不同的設備和方法,但都是為了保證產品的質量與可靠性。

1. CP測試與FT測試的基礎概念

要理解CP和FT的區(qū)別,我們可以將整個芯片制造和測試過程比喻成“篩選和包裝水果”的過程。

CP測試:相當于在水果采摘(晶圓制造)之后,在采摘場對每個單獨的水果進行檢測。目的是先挑出壞的、不合格的水果(壞的Die),避免這些水果被送入下一步的包裝環(huán)節(jié)。這一步可以減少包裝與運輸(封裝)的成本,同時確保進入后續(xù)步驟的水果(Die)都是較為優(yōu)質的。

FT測試:類似于對包裝好的水果盒進行檢測。在包裝之后,確保每個盒子里的水果(芯片)沒有在運輸(封裝)過程中變壞,最終保證顧客收到的是合格的商品。這是對最終產品的質量進行嚴格把控的一個重要環(huán)節(jié)。

2. CP與FT的具體流程及測試項目

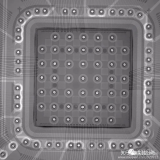

CP測試:晶圓級測試

CP測試發(fā)生在晶圓制造工藝的最后階段,是在晶圓層面進行的測試。在這一步,探針(Probe)接觸到晶圓上每個裸露的芯片(Die),通過電信號來測試其功能和基本參數。

目的:在CP階段,工程師希望通過測試剔除不合格的Die,以減少后續(xù)封裝不必要的成本。CP可以幫助判斷晶圓制造工藝的良率,也能用于檢測工藝中的問題,確保良品進入封裝環(huán)節(jié)。

測試項目:CP測試一般包括一些基礎的電氣參數,比如閾值電壓(Vt)、導通電阻(Rdson)、漏電流(Idss)、擊穿電壓(BVdss)等。這些都是半導體器件的基礎參數,因為此時沒有進行封裝,設備限制了測試電壓和功率,所以一些高功率測試項無法在CP階段進行。

比喻:可以將CP測試比作水果的初步篩選。例如,檢測每個水果的顏色、大小、是否有明顯的外觀損壞。雖然無法檢測水果的內部質量(類似于高電流或高溫測試),但可以通過表面特征來判斷哪些水果需要被剔除。

FT測試:封裝后的最終測試

FT測試發(fā)生在芯片被封裝成最終產品后。這時芯片已經通過封裝工藝,外殼保護了芯片的內部電路,因此需要使用不同的測試設備來完成。

目的:FT測試的目標是確保封裝后的芯片能在實際應用環(huán)境中正常工作,排除封裝過程帶來的潛在缺陷,同時確認芯片的功能性和可靠性。在一些情況下,FT測試還會進行環(huán)境測試,如高溫、低溫和正常溫度下的性能驗證(即三溫測試)。

測試項目:FT測試的項目包括功能測試、電氣特性測試以及一些特殊的耐久性測試。例如,高電流測試、待機測試、功耗測試等項目都需要在封裝后的FT階段進行,因為此時的芯片更接近實際應用場景,測試設備也能承受更大的電流和電壓。

比喻:FT測試相當于將包裝好的水果盒在不同的溫度下儲存一段時間,查看水果是否變質,確保每個盒子里的水果都可以送達客戶手中并保持新鮮。在這一階段,檢測的重點是整體包裝的質量以及在不同條件下的穩(wěn)定性。

3. 為什么有些公司省略CP測試?

在了解了CP和FT的區(qū)別后,許多人會問:既然CP測試可以剔除不合格的Die,為什么有些公司選擇省略這一步呢?

成本考慮:在一些工藝較為成熟、良率較高的情況下,晶圓制造中的缺陷率已經很低,進行CP測試可能會被認為是不必要的開支。因此,有些公司選擇只進行FT測試,尤其是當封裝和測試的良率較高時,直接省略CP可以節(jié)省制造成本。

風險與收益:不過省略CP測試也帶來了風險。例如,如果封裝成本較高,封裝壞Die會大幅度增加成本。因此,許多公司在封裝之前仍會進行CP測試,特別是在高成本的產品中,這樣可以確保最大限度地減少損失。

4. CP與FT的測試難點及挑戰(zhàn)

CP測試的難點

探針卡的制作:在CP測試中,探針卡的設計和制作是一個重要的技術挑戰(zhàn)。探針卡需要與晶圓上的每個Die精確對接,同時要保證測試的速度和精度。如果探針卡設計不當,會導致測試的干擾問題,甚至會損壞晶圓上的Die。

并行測試的干擾:在進行CP測試時,往往會采用并行測試技術,即一次測試多個Die。這種并行測試雖然可以提高測試效率,但容易引起信號干擾,影響測試結果的準確性。

大電流測試的限制:由于探針的電流限制,CP測試無法進行大電流測試(例如功率MOSFET的測試)。這部分只能留到FT測試中進行。

FT測試的難點

多溫度測試:FT測試中的三溫測試需要在不同溫度下對芯片進行功能性測試,模擬芯片在不同環(huán)境中的工作狀態(tài)。這種測試不僅復雜,而且對測試設備的要求較高,增加了測試的難度和成本。

高功率測試:FT測試需要對芯片進行高功率測試,測試設備必須能夠承受更高的電流和電壓,并且保證在嚴格的條件下芯片能夠正常工作。

5. CP與FT的相互補充關系

雖然CP和FT是兩個獨立的測試階段,但它們之間存在著緊密的聯(lián)系。CP測試是FT的前置步驟,負責剔除不良Die,降低后續(xù)封裝和FT的成本;而FT測試則確保了最終成品芯片的質量。

互相補充:CP測試幫助減少封裝不良品的概率,而FT測試則確保最終產品符合應用需求。一些測試項(如大電流測試)必須在FT階段進行,而有些在CP階段測試過的項目則可以在FT中省略,從而提高效率。

特定產品的優(yōu)化:對于某些產品,例如高良率的邏輯芯片,CP測試被省略,因為FT的良率已經足夠高;對于存儲器芯片memory),CP測試非常重要它可以通過MRA計算出需要修復的地址,通過激光修復工藝提升芯片的良率和可靠性。

6. 總結

我們可以將CP測試比作初步篩選水果,而FT測試則是對包裝后的水果盒進行檢測。兩者在測試目標、測試項目和測試設備上都有很大的不同。

CP測試的核心任務是剔除不合格的Die,減少后續(xù)封裝和FT測試的成本,同時監(jiān)控晶圓制造工藝的良率。而FT測試則主要是對封裝后的芯片進行功能和可靠性測試,確保最終產品能夠在不同環(huán)境下正常工作。

雖然有些公司選擇跳過CP測試以節(jié)省成本,但這并不適用于所有產品。對于高成本和高可靠性的產品,CP測試仍然是不可或缺的一步。最終,CP和FT測試共同確保了集成電路產品的質量和性能,二者缺一不可。

-

集成電路

+關注

關注

5452文章

12572瀏覽量

374569 -

測試

+關注

關注

9文章

6203瀏覽量

131368 -

晶圓

+關注

關注

53文章

5410瀏覽量

132297 -

芯片制造

+關注

關注

11文章

719瀏覽量

30466

發(fā)布評論請先 登錄

十年測試工程師復盤:CP與FT的邊界究竟在哪?

芯片FT測試是什么?

如何區(qū)分CP測試和FT測試

如何區(qū)分芯片CP測試和FT測試

芯片的幾個重要測試環(huán)節(jié)-CP、FT、WAT

CP測試與FT測試的區(qū)別

CP測試與FT測試的區(qū)別

評論