引言

多年以來,一直存在標準泛濫的現象,而我們電子業尤其嚴重。您是否曾經想過,為什么我們對有些奇怪的數字或測量計的東西建立標準?關于航天飛機的固體燃料火箭推進器的直徑是否真的源自于馬屁股的寬度的討論非常激烈。2相當的稀奇和有趣。但是,接受事實會更有成效:總是會有很多標準,我們必須找到使其很好配合的途徑。工程師和制造商均涉及到一個共同領域,其中標準的不兼容特別麻煩:原型平臺。幸運的是,有些方法可以緩解這些不兼容性。下文中我們將進一步分析討論。

開發板擴展標準

多年來,元件制造商一直提供開發系統,幫助其客戶采用其元件設計應用。對于可編程器件,例如FPGA和微控制器,始終存在與其它元件的接口,以便能夠與硬件同步或者早于硬件進行軟件開發。隨著時間推移,涌現出了關于這些“擴展接口”的非常松散的偽標準,其中有些標準的一致性相對較好。Xilinx等FPGA廠商推動這些標準,例如FMC,使客戶盡可能簡單地遷移到最新平臺。Xilinx也采用第三方標準,例如Digilent制定的Pmod標準,用于該接口的外圍設備選擇較廣。微控制器制造商的標準化略慢,許多采用自身的專用接口。然而,制造商動向和Arduino平臺普及等市場力量正驅使其也向偽標準靠攏。

Pmod非常適合FPGA

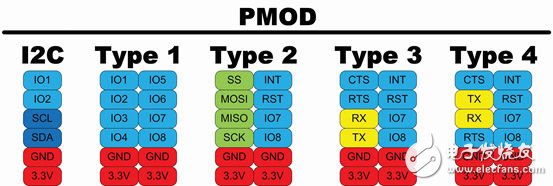

Pmod接口是將外設與FPGA開發板進行組合和匹配的很好方式,可利用方便、可手工焊接的連接器連接八個引腳以及電源和地。FPGA的靈活性允許將其八個信號引腳用于幾乎所有功能。盡管這提高了其對于FPGA的實用性,但也造成該接口難以配合那些外設功能分配給特定引腳的微控制器。為解決這一問題,Digilent定義了多種不同的Pmod引腳排列類型,不同的功能分配給特定的引腳(圖1)。

圖1. Pmod引腳排列類型將不同的功能分配給特定引腳。

類型定義使得微控制器板較容易使用Pmod接口標準,但仍然存在挑戰。利用許多微控制器有限的引腳復用能力,難以實現真正的通用接口,已被廢棄的Type 3 UART接口就是很好的例子。然而,即使存在局限性,對于原型或教育目的,Pmod接口是一種非常有用的擴展端口。

Arduino偽標準

Arduino偽標準是一個完全不同的老頑固,是出于各種原因為不同群體開發的不同平臺。最初的Arduino開發板僅提供簡單微控制器引腳,然后增加足夠的支持器件,從而使編程變得簡單,并且愛好者仍然可承受。由于其簡單性,原始引腳排列按照微控制器的性能定義。

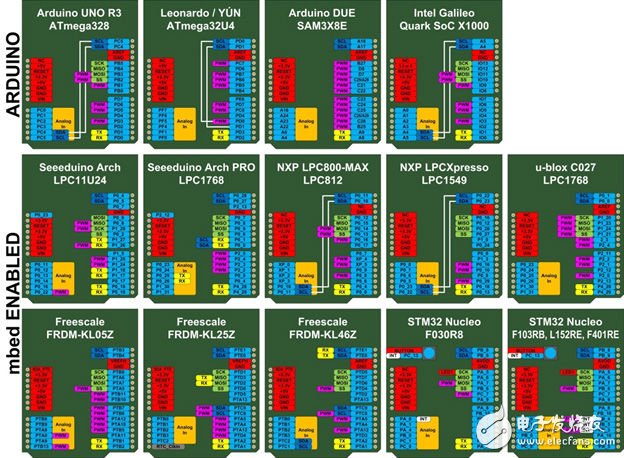

隨著平臺發展到支持功能更多的處理器,該偽標準逐漸碎片化,具有各種引腳復用組合,可以說是例外多于規則。有些問題,例如支持不同的I/O電壓以及I2C信號的不一致性,在第3版的UNO板中得到了解決。然而,在將擴展板與Arduino開發板(或任何Arduino衍生產品)配對使用時,必須仔細檢查兼容性。并且可供選擇的Arduino衍生產品很多(圖2),即使僅限于Arduino網站提供的官方開發板,引腳兼容性也并不簡單。但是,一般而言,每個具有特殊功能的Arduino引腳也可用作通用I/O (即GPIO)。

圖2 .Arduino開發板配置為多種衍生產品,以支持不同的設計和應用。

與Pmod接口中一個引腳可用作多種特殊功能不同,大多數Arduino引腳通常執行單一的特殊功能。從根源上講,Arduino偽規范比Pmod接口更適合于微控制器。所以,這就是Arduino規格的微控制器板比Pmod連接器的微控制器板更容易找到的原因。

Pmod與Arduino接口之間的映射

我們可以采用Pmod接口和Arduino偽標準,兩者各有眾多來源可供使用。是否能夠使某個平臺的外設與另一平臺的控制器進行通信呢?當然,一切皆有可能,但有時候治療比疾病本身更糟糕。

如果將Arduino UNO第3版引腳排列與Pmod規范進行比較,您馬上會發現Arduino板上有22個信號引腳,而Pmod連接器上只有8個引腳。從技術上講,有可能將全部22個引腳串行化,使其通過Pmod提供的8個引腳,然后在另一側對其進行解串,但我們將這一工作留給讀者。將22個Arduino信號自適應映射到Pmod規范定義的不同類型(見圖1),是可以做到的,但仍不輕松。以上圖1所示為5種不同類型的Pmod接口。許多信號采用電平觸發,可由軟件通過GPIO引腳控制。然而,有些信號采用時間觸發協議,利用微控制器內部的外設更容易控制。所以,困難在于將微控制器的所有專用引腳映射到Pmod規范定義的引腳。

建議方案:使用串行控制交叉點開關

解決映射問題的一種途徑是在電路板上安裝配置跳線陣列。這種方法盡管很簡單明了,但既不美觀也不人性化。適合Arduino板尺寸的說明文字字體會非常模糊難辨。許多引腳可能是雙向的,所以簡單的邏輯門不是信號連接的好選擇。模擬開關能起作用,但沒有足夠的附加引腳來對其進行獨立控制。利用I2C端口擴展器,可解決引腳短缺的問題。誠然,這種方法不比跳線更巧妙,但可通過軟件配置。

如果沒有串行控制16:2多路復用器,MAX14661,這種方法似乎毫無希望。咋一看,支持所有不同類型的Pmod好像需要四片器件,那么這種方法很難說比端口擴展器方案好多少。實際情況真的會是這樣,除非...MAX14661具有特殊功能。該器件允許同時激活任意開關組合,所以可用作8:8交叉點開關。

至此為止,一切順利。但是,不可否認,8:8交叉點配置有一個局限性:同時只能傳輸兩路獨立信號,每個COM引腳一路。但同時兩路信號有什么好處?如上所述,大多數信號可由GPIO驅動,只有少數信號要求內部外設控制器。如果每個引腳分配一路GPIO,只有時間觸發的串行線路需要通過復用器連接。UART和I2C為2線總線,所以不適合通過復用器的唯一串行總線是SPI。SPI只有一種接口定義,所以將SPI信號直接連接至連接器,作為這些接口的GPIO連接。當其中某個引腳需要用作時間觸發功能時,只需將GPIO置于三態。

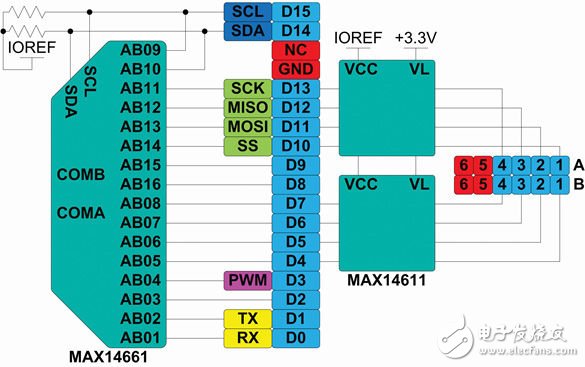

信號電平怎么樣呢?最初的Arduino設計及許多后來者使用5V信號電平,但現在5V信號沒有以前那么常見。為解決這一問題,后來的Arduino版增加了IOREF引腳,以表示基于較低電壓微控制器的衍生品。Pmod連接器沒有IOREF引腳,但其絕大多數模塊支持3.3V信號。幸運的是,MAX14611等雙向電平轉化器解決了這一問題。只需將Arduino信號連接至由IOREF供電的電平轉換器的一側。然后將另一側連接至由Arduino板上專用3.3V電平供電的Pmod連接器。MAX14661多路復用器采用1.8V至5V的電源供電時可承受及傳輸-5V至+5V的任何信號,所以可安裝在電平轉換器的任何一側。由于至多路復用器的Arduino連接多于Pmod連接,所以將MAX14611安裝在電平轉換器的Arduino很有意義。按照這種方式,Pmod連接器處只需要兩片4通道器件(圖3)。

圖3. 建議方案的邏輯圖。

方案評估

該方案的關鍵是每個通道支持同時多個連接。COM引腳不連接,但在復用器內部用于選擇連接。MAX14661的16個復用連接中的8個專用于Pmod連接器,也連接至4路支持SPI的信號和4路其它GPIO(圖3)。其它8個復用連接綁定至2線串行總線和其它時間關鍵信號,例如PWM或定時器引腳。例如,為實施I2C類型,只需配置復用器,在通道A上使能SDA引腳和Pmod引腳4,在通道B上使能SCL和Pmod引腳3。通道A和B是任意選擇的,可隨意交換。實際上,甚至可以使能Pmod連接器上第二排的引腳3和4,以訪問另外的6引腳I2C Pmod。如果I2C器件的地址不同,甚至可使兩個端口保持工作狀態,或者動態激活,以支持相同地址的兩個器件。使用跳線方法,根本不可能在兩個具有相同地址的器件之間進行動態切換。使用MAX14661,能夠以編程方式配置所有指定的Pmod類型,甚至非標準類型,而只需單片尺寸僅為4mm X 4mm的有源器件。

為什么有人設計非標準Pmod?原因之一是與微控制器相同的引腳復用問題。例如,MAX14661支持I2C和SPI控制,取決于配置引腳的狀態。MAX14661的外設模塊的引腳排列與SPI Pmod類型相匹配,但時鐘和數據引腳與Digilent Pmod規范規定的I2C引腳不匹配。適配卡上的MAX14661可將SDA和SCL信號映射到任意Pmod引腳,可用于支持非標準MAX14661外設模塊、I2C引腳映射。MAX14661也有兩個地址引腳,以支持4個不同的I2C器件地址。因此,可將系統設計為支持同一總線上的多個器件。

使用MAX14661復用I2C總線時,在帶內發送命令。切換將與I2C總線同步生效。當然,在帶外復用I2C總線具有挑戰性,因為如果不小心,會在從機將SDA線拉低時斷開;下次選擇該總線分支時,分支可能鎖死。MAX14661始終在I2C寫命令結束時轉換總線,此時開關另一側的器件應為空閑。

-

FPGA

+關注

關注

1660文章

22409瀏覽量

636252 -

Arduino

+關注

關注

190文章

6526瀏覽量

196914 -

Pmod

+關注

關注

0文章

22瀏覽量

8476

發布評論請先 登錄

基于AMD FPGA的HDMI2.1接口實現

Altera FPGA的Avalon MM總線接口規范介紹

DMA彈性映射功能

【瑞薩RA6E2】PMOD 接口 LCD 顯示屏調色板

【RA4E2開發板評測】PMOD 接口 LCD 顯示屏調色板

如何在智多晶FPGA上使用MIPI接口

火爆開發中 | 開源FPGA硬件板卡,硬件第一期發布

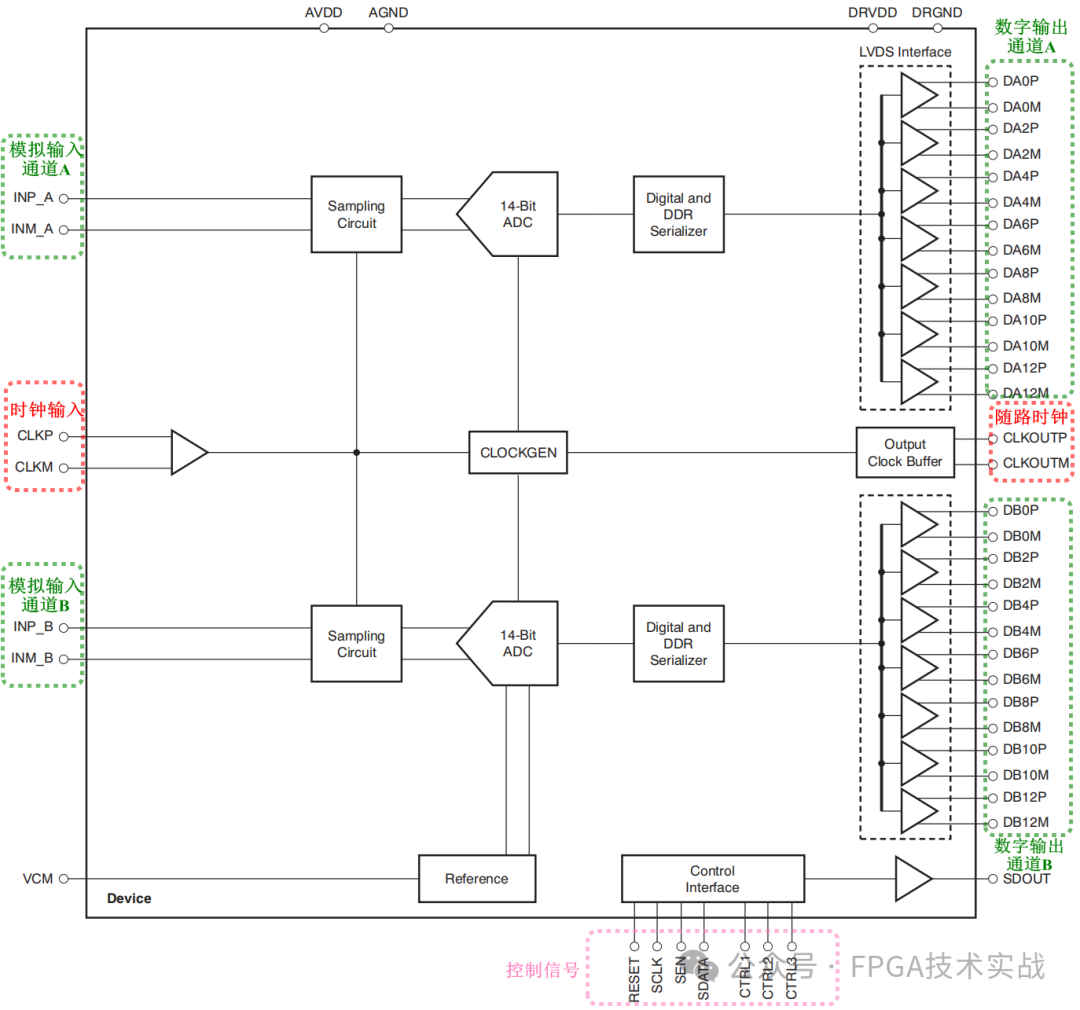

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設計

FPGA的Jtag接口燒了,怎么辦?

Profibus DP主站網關數據映射全解析!

基于Fpga的Pmod與Arduino接口映射

基于Fpga的Pmod與Arduino接口映射

評論