隨著超高清視頻與高幀率顯示需求的提升,大帶寬視頻接口被廣泛應用,其中HDMI是使用最廣泛的音視頻傳輸接口。AMDFPGA憑借其高性能的邏輯資源和穩定的高速串行接口,可以幫助用戶輕松實現HDMI2.1接口的產品部署。本文將以ZCU106開發板為基礎,介紹HDMI2.1的硬件和軟件實現,并針對常見調試問題給出解決思路。

HDMI2.1接口概述

High-Definition Multimedia Interface(HDMI)是一種傳輸音視頻數據的專用接口。目前最新的版本為HDMI 2.1,最大帶寬48Gbps,最大可支持8K30Hz RGB無壓縮的數據傳輸。

HDMI2.1在兼容HDMI2.0 TMDS傳輸模式的前提下,新增了FRL模式傳輸,并且可在TMDS和FRL模式之間任意切換,全方位兼容用戶使用需求。

AMD HDMI2.1 IP介紹

AMD HDMI2.1子系統支持最高12Gb/s@4lanes線速率并向下兼容HDMI2.0協議。子系統還支持可選的HDCP1.4和HDCP2.3加解密功能,并且已經通過CTS認證測試。

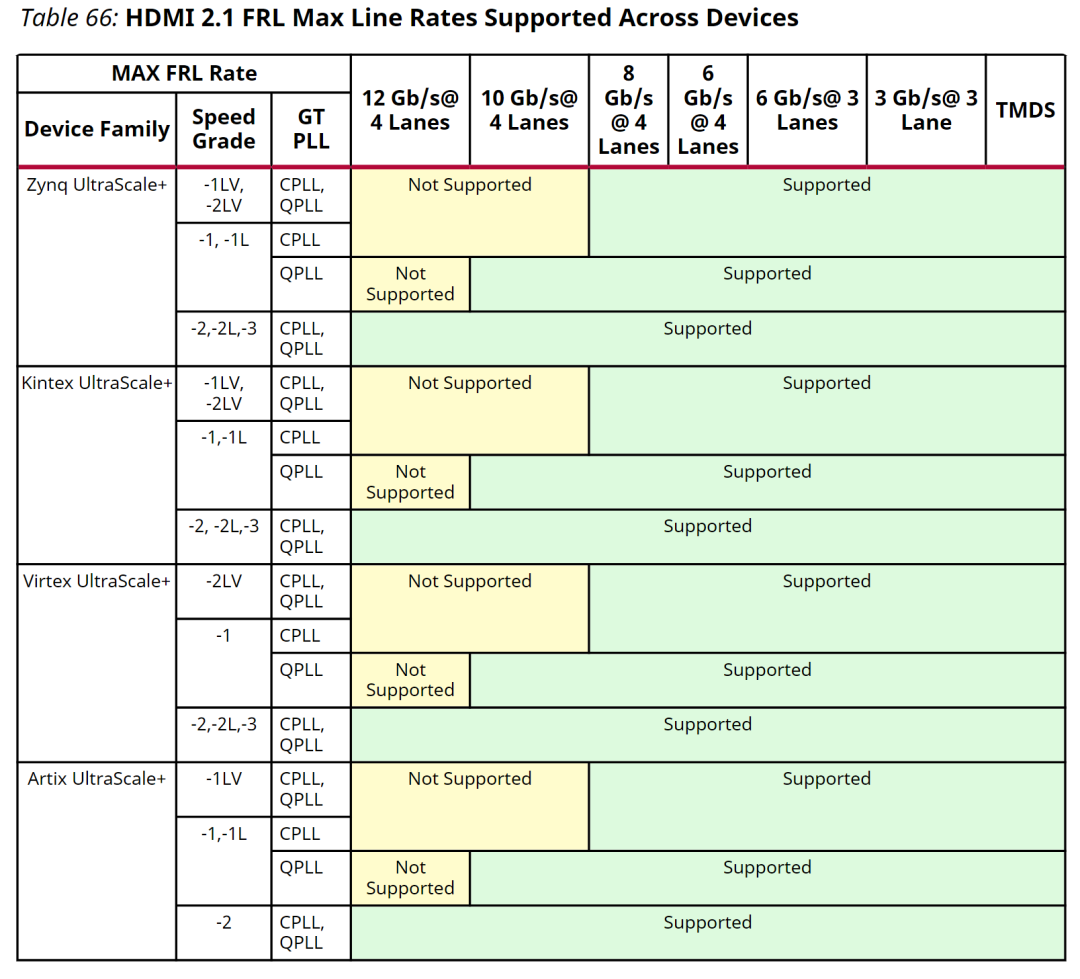

AMD HDMI2.1子系統支持16nm和7nm器件,最小器件為AU20P,并且在-1、-1LV、-2LV有速率限制,在選型時需要注意。

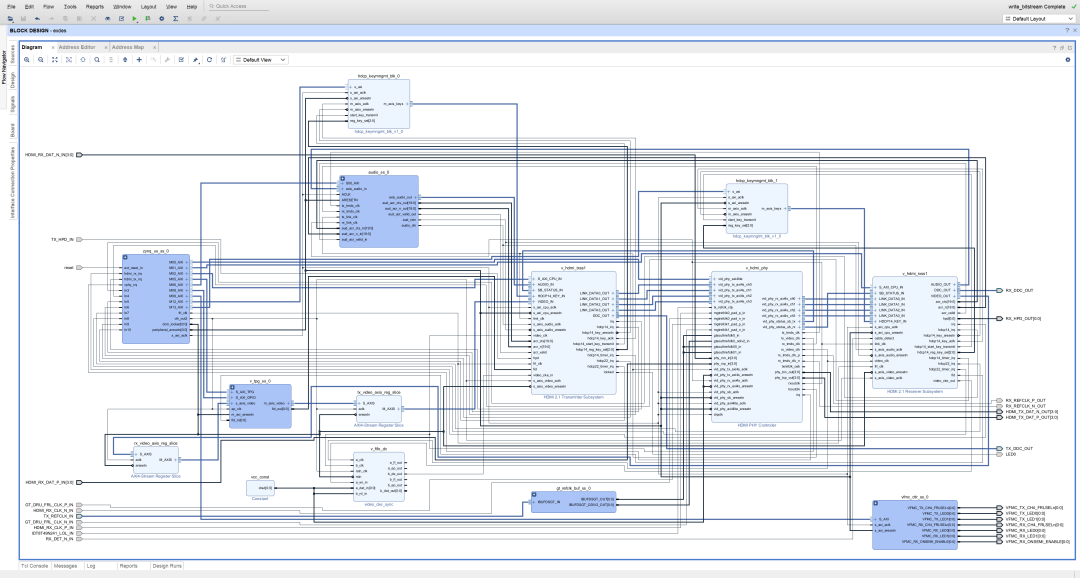

基于AMD FPGA實現的HDMI2.1方案需要兩個IP配合使用,分別是HDMI Phy Controller和HDMI2.1 subsystem。下面分別進行介紹。

HDMI Phy Controller:

HDMI Phy Controller主要負責高速串行數據的物理層收發,包括TMDS或FRL模式下的數據編解碼、時鐘恢復、電氣均衡等,簡化串行收發器的使用。

接口介紹:

HDMI PHY Controller由多個子模塊組成,如下圖所示。

PHY Control/Status Manager模塊實現軟核對IP的寄存器和中斷控制,所有模塊的狀態和控制信號均由該模塊通過axi-lite總線與CPU或軟核通信。

NI-DRU用于支持較低線速率的應用,如TMDS模式下的640x480@60Hz分辨率,線速率時鐘為25MHz,該時鐘通過GTREFCLK管腳接入QPLL或CPLL,但時鐘頻率小于QPLL(61.25MHz)和CPLL(50MHz)的最小工作頻率,此時通過NI-DRU功能仍然可以正常恢復出視頻數據。

User Clock Source模塊負責管理HDMI子系統的時鐘資源,例如HDMI2.1 RX子系統需要三個時鐘輸入到FPGA內部,分別是TMDS模式下的隨路時鐘、FRL模式下的參考時鐘以及NI-DRU時鐘。

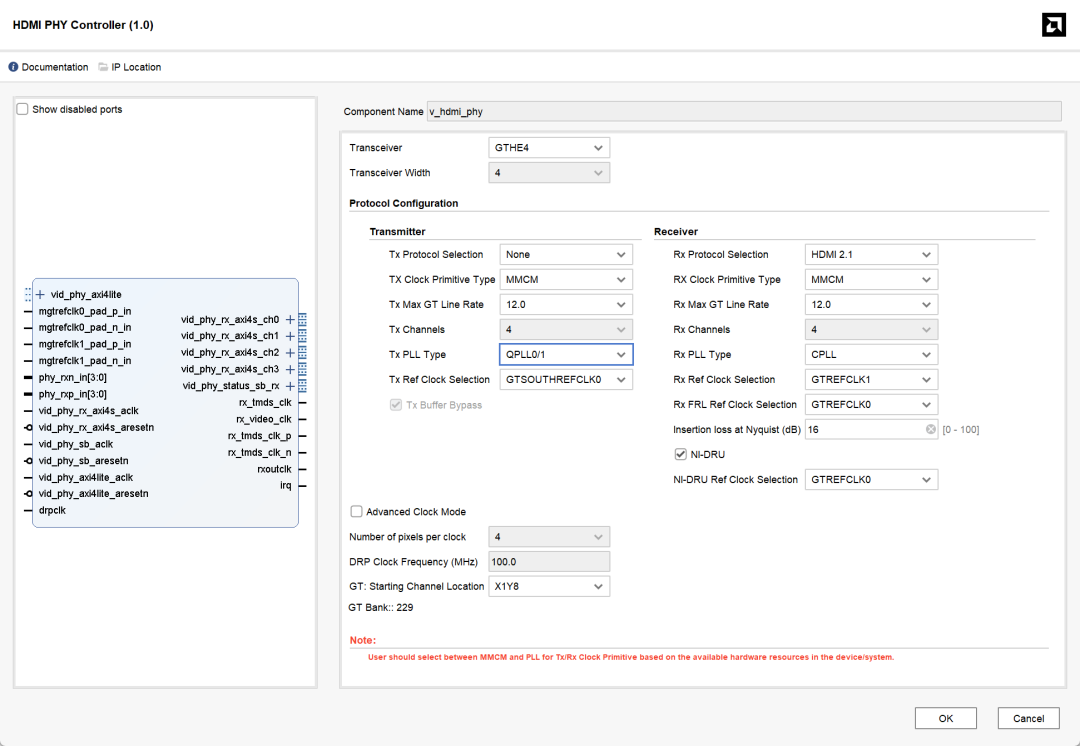

IP配置:

以HDMI2.1-RX為例,協議選擇HDMI2.1,最大線速率為12Gbps,時鐘模塊建議選擇MMCM,這樣可以很好的支持小數時鐘頻率。RX子系統需要三個外部輸入的時鐘:

Rx Ref clock selection:TMDS模式下的隨路時鐘,時鐘頻率跟隨分辨率變化;

FRL Ref clock selection:FRL模式下參考時鐘,-2器件頻率為400MHz,-1器件頻率為200MHz;

NI-DRU Ref clock Selection:提供給DRU模塊的時鐘,以恢復低線速率視頻數據,可以與FRL參考時鐘共用一個;

所有提供給GT的參考時鐘的抖動要求不超過±100PPM,ni-dru參考時鐘頻率誤差不能超過±10 kHz。

HDMI2.1 Subsystem

HDMI2.1 Subsystem主要負責從PHY層捕獲HDMI流,從HDMI流中解析數據并轉換為視頻和音頻流。

接口介紹:

HDMI子系統主要為三部分組成,如下圖所示。HDMI Receiver Core主要功能為負責HPD握手、解析音頻、視頻流和HDR數據,AXI-lite接口負責與軟核進行寄存器和中斷通信,HDCP為可選功能,實現HDCP1.4和HDCP2.3加解密功能。

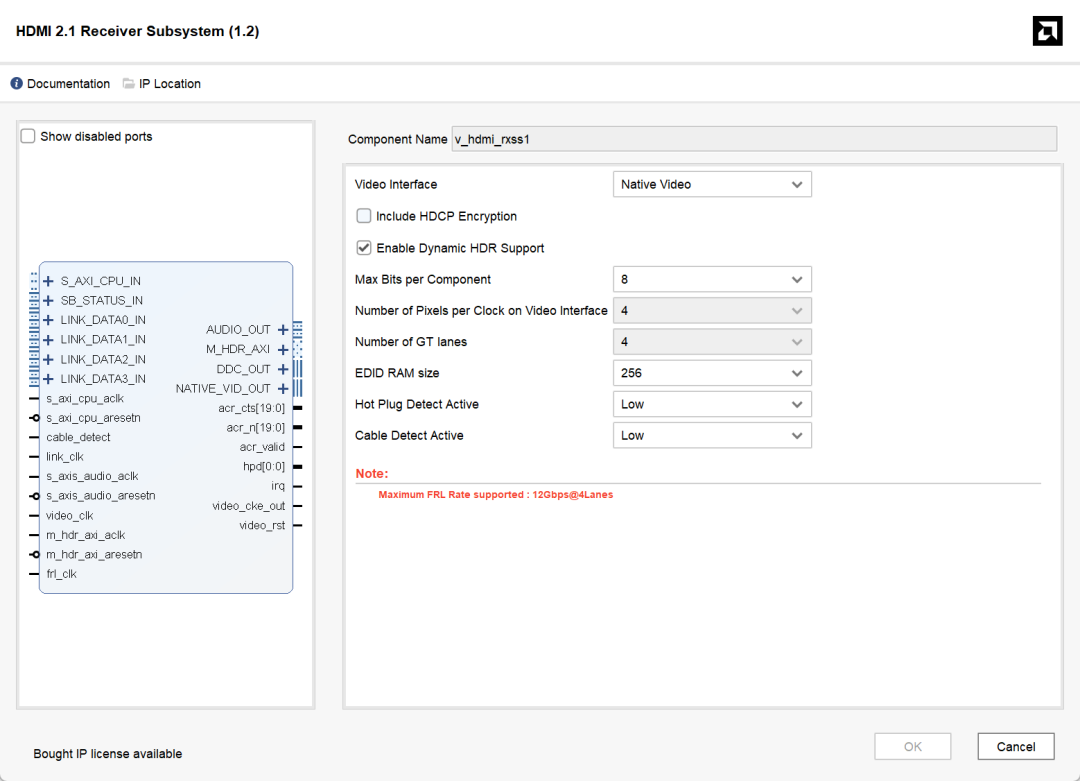

IP配置:

IP提供了axi-stream和native video接口供用戶內部邏輯使用。

當使用axis-stream接口時,用戶需要外部提供s_axis_video_clk,時鐘頻率要求s_axis_video_clk >= HActive*Vactive*Frame Rate/PPC。

當使用native video接口時,PPC固定為4,視頻數據時鐘域為video_clk,該時鐘來自hdmi phy controller。Tmds模式下,該時鐘為像素時鐘,頻率與分辨率成比例,如3840x2160@60Hz時,該時鐘為4400*2250*60/4=148.5MHz;在FRL模式下,該時鐘為固定的400MHz。

Frl_clk為固定的450MHz,可以使用內部mmcm或pll產生,供給IP使用。

參考設計

硬件設計:

實現HDMI2.1接口需要GT外部添加適當的EQ或retimer以滿足HDMI電氣特性。AMD官方推薦使用安森美NB7NQ621M或TI TMDS1204。

對于HDMI-RX接口,第四條lane在tmds模式下傳輸的是隨路時鐘,在frl模式下傳輸數據,因此需要將第四lane同時接入GT Refclk管腳和GT RX管腳。推薦器件:FUSB340TMX實現1分2功能。

軟件設計:

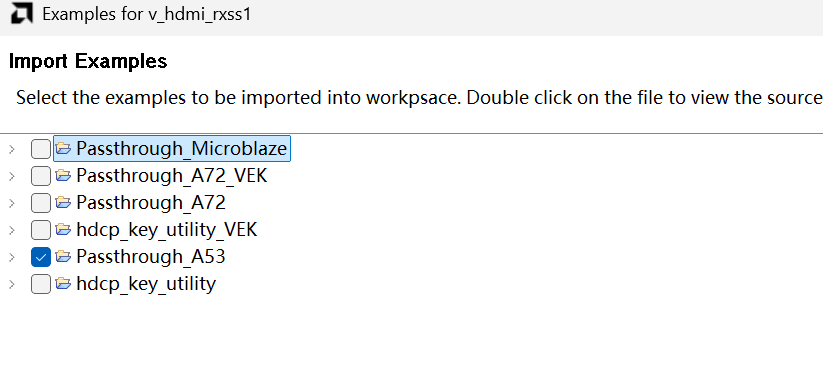

以ZCU106開發板為例,AMD提供了帶有HDCP功能的HDMI-RX和HDMI-TX passthrough例程:

Vivado工程:

Vitis工程:

常見問題及調試方法

1. 使能NI-DRU功能后,顯卡推小分辨率無法lock,dru時鐘顯示為1Hz:

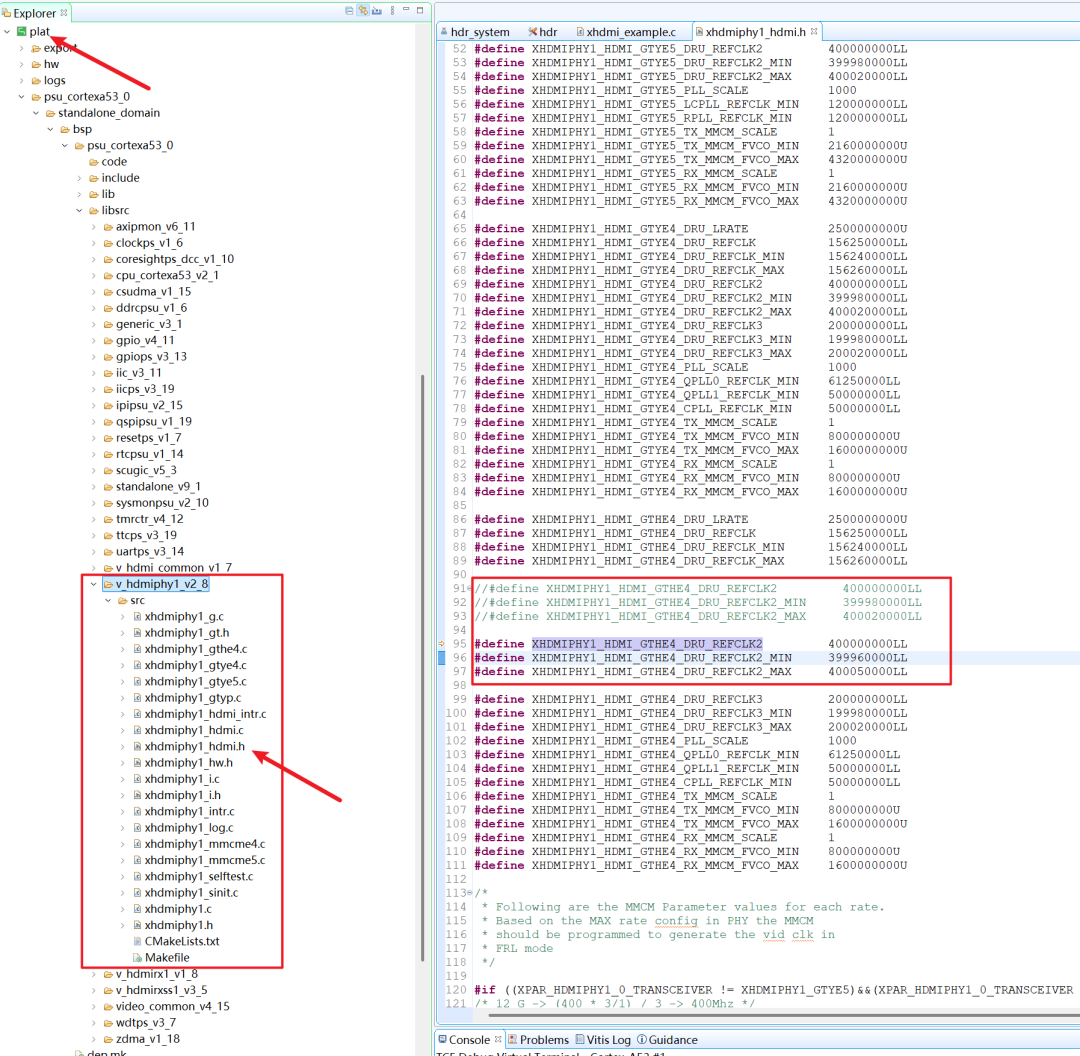

出現此問題是因為提供給dru模塊的參考時鐘誤差超過了±10kHz,可以考慮更換精度更高的晶振,也可以修改軟件中的時鐘檢測參數暫時解決,方法如下:

將原來的最大最小值范圍擴到可以覆蓋板上晶振的輸出頻率,此時dru模塊會恢復正常。

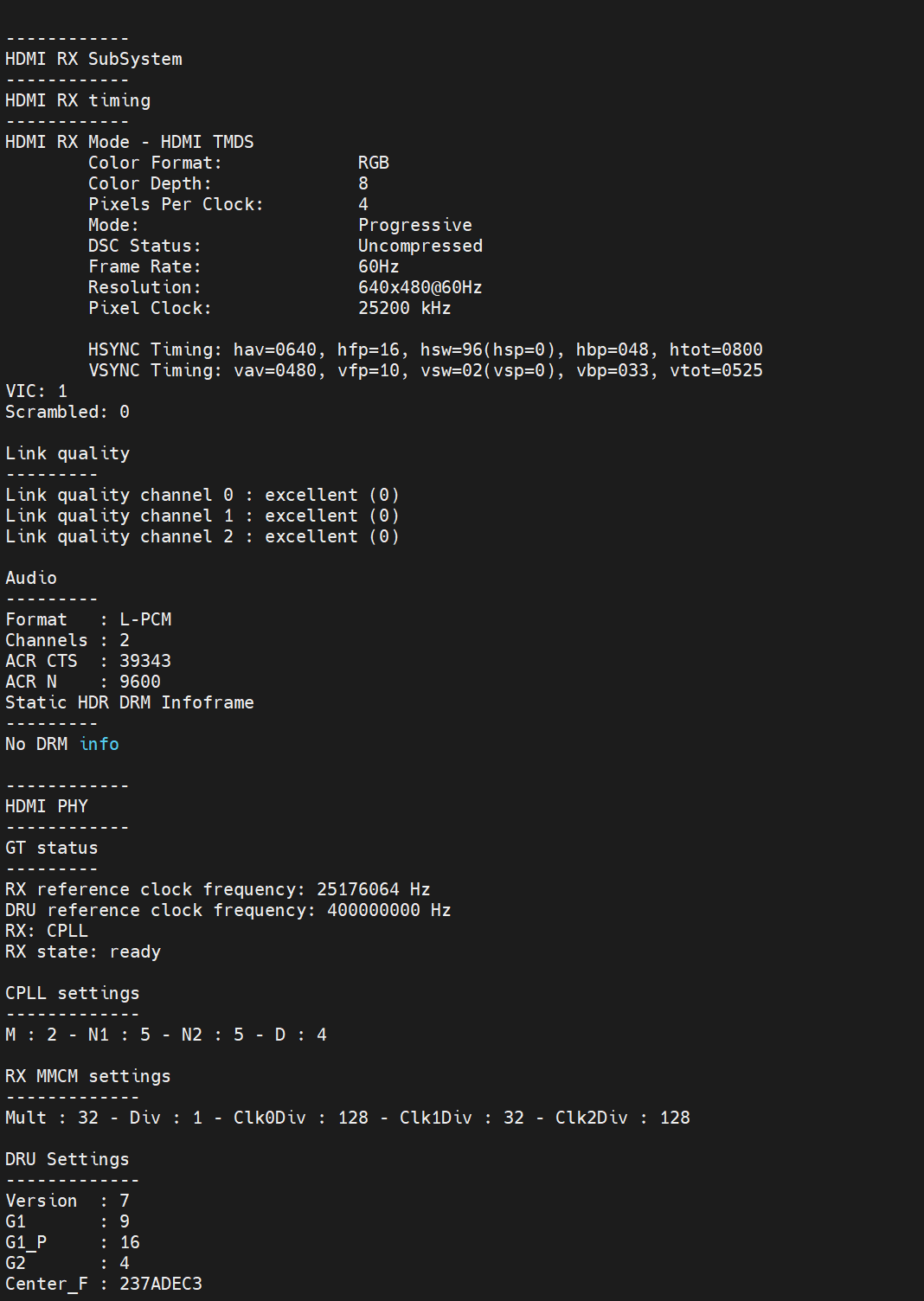

如下圖所示為NI-DRU功能正常運行時的打印信息:

當檢測到輸入當前分辨率隨路時鐘小于CPLL最低限制(50MHz)時,DRU功能自動使能,并開始計算CPLL、MMCM的分頻系數:

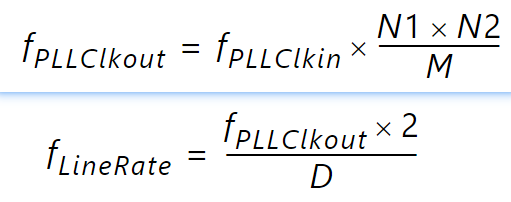

CPLL:

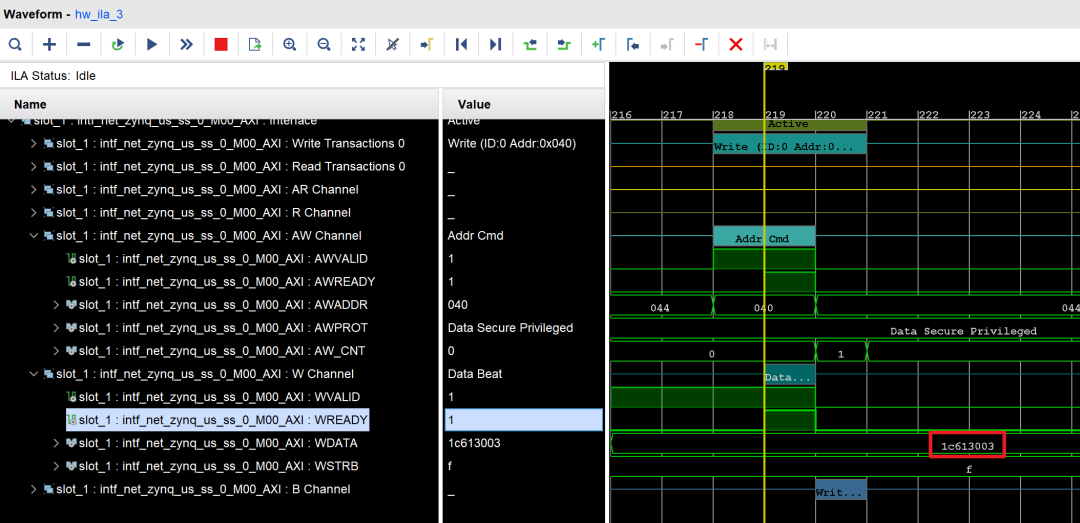

fPLLClkin=400MHz,此時計算出線速率時鐘為2500MHz,即在2.5Gbps的線速率下對低速數據進行過采樣。使用ila抓取GTH配置寄存器0x0003,配置數據為0x1C61,其中bit8-5為RX_DATA_WIDTH,這里對應值為3,即RX_DATA_WIDTH=20bit,此時rxoutclk=2500/20=125MHz。

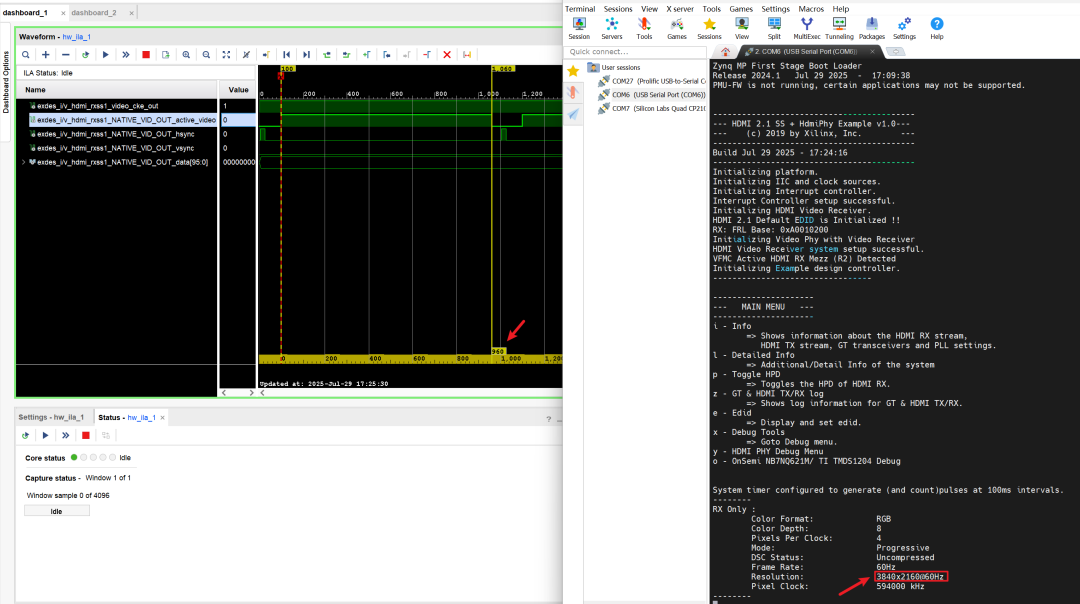

2. 選擇native video接口時,ppc固定為4,tmds模式下video_de的寬度為Hactive/4,如下圖:

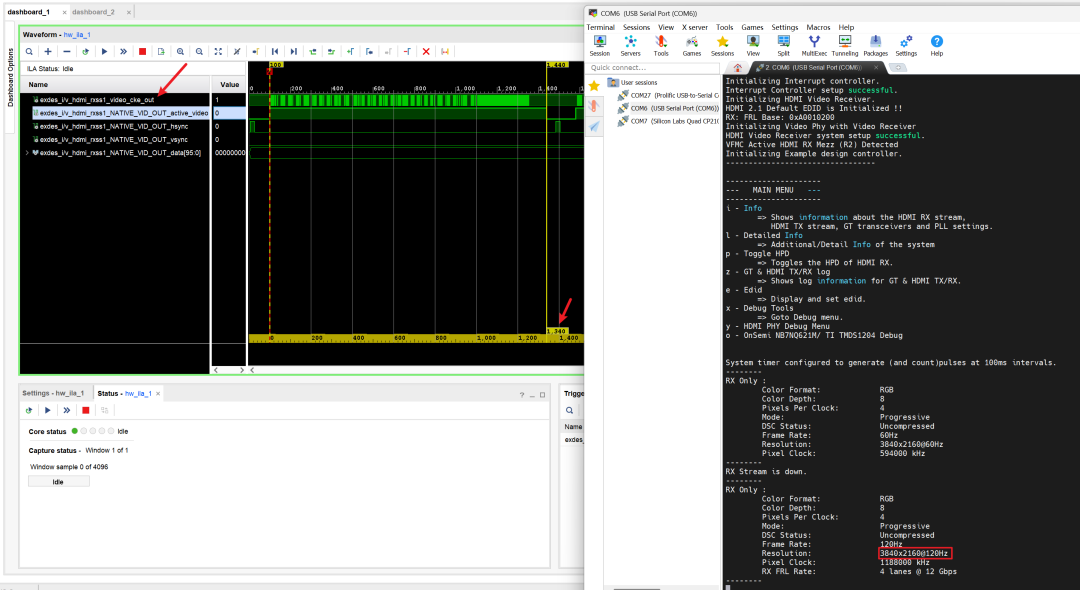

當分辨率為FRL速率時,video_de信號并不是Hactive/4,此時需要配合video_cke_out使用,當video_de和video_cke_out同時為高電平時,此時對應的video_data為有效像素點:

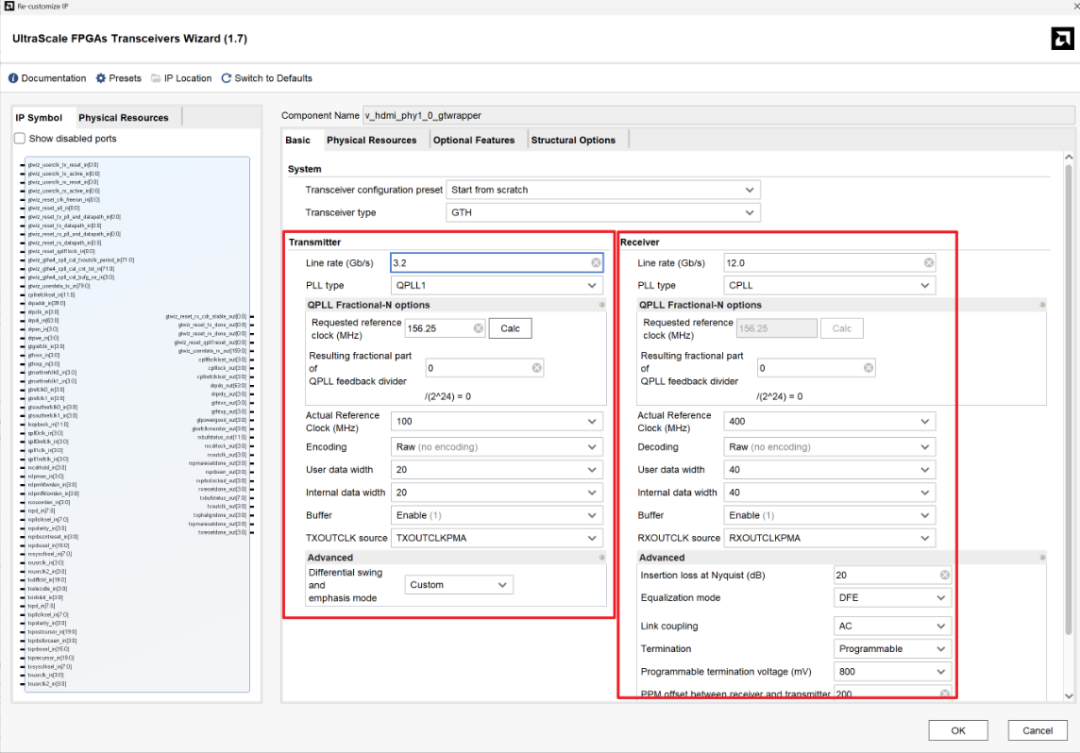

3. HDMI PHY Controller可以放在Block Design外面例化,此時可以通過修改GT_wizard以實現同一個GT Quad的RX運行HDMI2.1,TX實現其它協議的功能或TX運行HDMI2.1,RX運行其它協議:

參考資料

PG333 HDMI-PHY-Controller

PG351 HDMI2.1 Receiver Subsystem Product Guide

UG576 Ultrascale GTH Transceivers

-

FPGA

+關注

關注

1662文章

22450瀏覽量

637712 -

amd

+關注

關注

25文章

5694瀏覽量

140187 -

HDMI

+關注

關注

34文章

1909瀏覽量

161083

原文標題:AMD技術干貨|基于AMD FPGA的HDMI2.1接口實現

文章出處:【微信號:AvnetAsia,微信公眾號:安富利】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

三星HDMI2.1接口QLED電視,給你帶來視覺上的享受

8K接口HDMI2.1有什么作用到底需不需要HDMI 2.1

HDMI2.1新增了哪些不可忽視的重要功能

HDMI2.1標準的定義及其與HDMI2.0的區別

CS5298 Type-C轉HDMI 2.1轉換方案芯片,CS5298 DP1.4轉HDMI2.1轉換芯片

HDMI2.1進行了哪些改良

掌握連接線HDMI2.1和HDMI2.0的區別-科蘭

基于AMD FPGA的HDMI2.1接口實現

基于AMD FPGA的HDMI2.1接口實現

評論