當前,使用FPGA來進行數字邏輯課程實驗以及相關動手實踐、創新已經被越來越多的老師和學生所接受。學習數字邏輯基礎課的同時,掌握FPGA設計的基本流程和技巧也會對后續的學習以及工作有莫大的好處。

EGO1,這一最新的Xilinx口袋實驗平臺正是為此而生!各位對EGO1還不是很熟悉的小伙伴們,請點擊這里詳細閱讀EGO1口袋實驗平臺的詳細介紹。

EGO1配套教材-《基于Xilinx Vivado的數字邏輯實驗教程》

針對初學上手的小伙伴們,EGO1口袋實驗平臺推薦有多部參考教材。今天要介紹的就是一本來自于哈爾濱工業大學電工電子實驗教學中心電子學實驗室主任廉玉欣老師精心編寫的-《基于Xilinx Vivado的數字邏輯實驗教程》。

本書由依元素科技提供技術支持,以Xilinx公司最新的Vivado FPGA集成開發環境為基礎,將數字邏輯設計與硬件描述語言Verilog HDL相結合,循序漸進地介紹了基于Xilinx Vivado的數字邏輯實驗的基本過程和方法。書中包含了大量的設計實例,內容翔實、系統、全面。

目前該書已在各大平臺以及實體書店有售,使用EGO1學習數字邏輯以及FPGA設計的小伙伴們可不要錯過噢!

EGO1動手練習

今天我們EGO1動手練習部分要做的是一個計數器實驗。這個實驗在參考教材《基于Xilinx Vivado的數字邏輯實驗教程》的第5章第3節,是時序邏輯實驗部分的10K進制計數器實驗。

在Verilog中,實現一個任意位的計數器非常容易。一個計數器的行為就是在每個時鐘的上升沿使輸出加1。

我們通過編寫Verilog代碼來完成這個計數器邏輯電路。

其中,mod10kcnt_top.v為計數器實驗的頂層模塊。該模塊的作用是將各個模塊連接起來。

clkdiv.v為時鐘分頻模塊,將輸入為100MHz的時鐘分頻為190Hz和48Hz。

mod10kcnt.v為10K進制計數器模塊。該模塊的輸入時鐘為48Hz。

binbcd14.v為14位二進制轉BCD碼模塊,該模塊的作用是將10K進制計數器模塊的輸出轉換為BCD碼。

x7segbc.v為數碼管模塊。該模塊的輸入時鐘為190Hz,該模塊的作用是將轉換后的BCD碼通過數碼管顯示出來。

mod10kcnt_top_tb.v為Testbench文件,該文件的作用是給這個計數器邏輯電路施加測試激勵信號,并進行仿真。

mod10kcnt_top_top.xdc為管腳約束文件。

關于實驗原理部分的詳細講解,有興趣的小伙伴們可以查閱參考書的對應章節。

實驗源文件準備妥當之后,我們就可以開始動手實踐啦。

首先當然是打開Vivado工具咯,這里我們使用最新的2017版本的Vivado開發環境。什么?你還沒有安裝Vivado么?表擔心啦,我們提供有詳細的Vivado安裝流程。

Vivado開發環境成功打開后,它的主界面如下。

接下來就讓我們開始使用Vivado完成這個實驗吧。如果有對Vivado操作不熟悉的小伙伴們也不用擔心啦,我們提供有STEP-BY-STEP的指導噢。

首先,我們進行實驗仿真。下面是仿真的結果。

同時,我們可以在Vivado中查看我們RTL所對應的原理圖。

在完成Vivado FPGA綜合流程后,我們還可以看到這段電路綜合后的原理圖。

最后,我們完成設計的整體實現,可以看到這段電路在實際的FPGA芯片中的線路圖。

接下來,就可以在硬件平臺上下載驗證啦。當然,我們也有使用EGO1口袋實驗平臺來進行硬件下載的詳細步驟介紹喲。

硬件配置完成后,我們就可以在EGO1平臺上來驗證我們的設計啦,這個設計中我們將EGO1開發板的撥碼開關SW0作為clr的輸入,同時用數碼管顯示計數結果。將SW0拉高后,計數結果就直接顯示在數碼管上面了。好啦,各位小伙伴們大家看看我們的電路計算正確么?

FPGA我們是認真的!

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636281 -

FPGA設計

+關注

關注

9文章

431瀏覽量

28138 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131129 -

數碼管

+關注

關注

32文章

1894瀏覽量

94135 -

egO1開發板

+關注

關注

1文章

3瀏覽量

4915

原文標題:【玩轉EGO1系列教程九】:使用EGO1動手學習數字邏輯系列(4)

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

使用Xilinx 7系列FPGA的四位乘法器設計

Xilinx FPGA串行通信協議介紹

請問如何將蜂鳥E203移植到Xilinx NEXYS A7 FPGA 開發板上?

【VPX650 】青翼凌云科技基于 VPX 系統架構的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

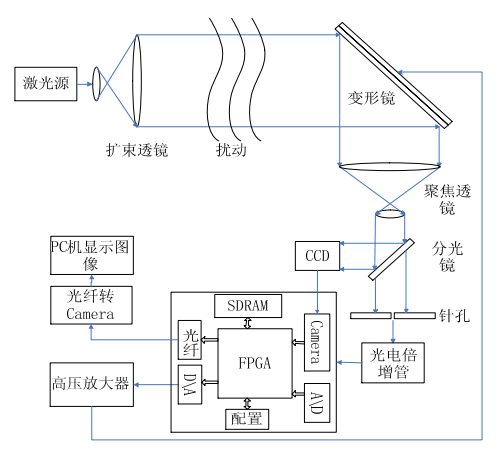

高壓放大器驅動:基于FPGA的SPGD自適應光學控制平臺的探索

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX雙FMC接口通用信號處理平臺

一文詳解xilinx 7系列FPGA配置技巧

【TES807】青翼凌云科技基于 XCKU115 FPGA 的雙 FMC 接口萬兆光纖傳輸信號處理平臺

使用Xilinx口袋實驗平臺,動手FPGA設計!

使用Xilinx口袋實驗平臺,動手FPGA設計!

評論