LPC175x作為NXP公司主推的cortex-M3內核芯片,廣泛應用于各工控、電子計量、報警系統等領域,無論何種應用,根據實際需求選擇合適的時鐘源并配置合理的系統時鐘頻率都是必不可少的。

以EasyARM-1754M3開發板為例,LPC1754芯片外部晶體振蕩器包含兩個,一個頻率為12MHz外部高速晶振和一個頻率為32.768KHz的外部低速晶振,兩個都可以使用軟件設置選用或不選用。此外LPC1754內部也包含三個獨立的振蕩器,他們分別是內部主振蕩器,內部RC振蕩器和內部RTC振蕩器。實際應用當中常用的振蕩器是外部高速晶體振蕩器,和外部低速晶體振蕩器。

LPC1754內部PLL0原理簡介

PLL0包含多個寄存器,其中PLL0時鐘源的選擇可在CLKSRCSEL寄存器中設置,PLL0將輸入時鐘進行倍頻,然后再分頻為CPU及芯片外設提供實時時鐘信號。PLL0可產生的時鐘頻率最高可達100MHz,是CPU所允許的最大值。

PLL0內部結構可表示為下圖,PLL0的輸出時鐘信號即為pllclk,后經過CPU時鐘分頻器的分頻,產生系統時鐘,系統時鐘再進入外設時鐘分頻器后輸出多路的外設時鐘。

應用舉例

EasyARM-1754M3開發板配套的所有例程使用統一的系統初始化函數SystemInit()將系統時鐘配置為96MHz,外設時鐘配置為默認值24MHz。用戶可在對此函數有一定理解的條件下,根據自身實際需求,對參數進行修改,可修改項一般包含時鐘源、倍頻系數、分配系數三個重要參數,系統初始化函數當中的PLL0配置部分如下程序清單所示:

#if (CLOCK_SETUP) /* Clock Setup */

LPC_SC->SCS = SCS_Val;

if (SCS_Val & (1 << 5)) {????????????????????????????? ?????/* If Main Oscillator is enabled? */

while ((LPC_SC->SCS & (1<<6)) == 0);???????????? ????????/* Wait for Oscillator to be ready*/

}LPC_SC->CCLKCFG = CCLKCFG_Val; /* 系統時鐘分頻值,CCLKCFG_Val值可改 */

LPC_SC->PCLKSEL0 = PCLKSEL0_Val; /* Peripheral Clock Selection */

LPC_SC->PCLKSEL1 = PCLKSEL1_Val;

LPC_SC->CLKSRCSEL = CLKSRCSEL_Val; /* 選取時鐘源,CLKSRCSEL_Val值可改 */

#if (PLL0_SETUP)

LPC_SC->PLL0CFG = PLL0CFG_Val; /*PLL0倍頻值,PLL0CFG_Val值可改 */LPC_SC->PLL0CON = 0x01; /* PLL0 Enable */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

while (!(LPC_SC->PLL0STAT & (1<<26)));????????????? ??????/* Wait for PLOCK0?????????????? */

LPC_SC->PLL0CON = 0x03; /* PLL0 Enable & Connect */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

#endifLPC_SC->PCONP = PCONP_Val; /* Power Control for Peripherals */

LPC_SC->CLKOUTCFG = CLKOUTCFG_Val; /* Clock Output Configuration */

#endif其中關鍵參數為PLL0倍頻系數PLL0CFG_Val、CPU時鐘分頻系數CCLKCFG_Val,由于寄存器值比實際值小1,因此它們實際值為16和4。另外每次想PLL0相關寄存器寫入新的數值時,需要向饋送寄存器當中寫入饋送系列以后才能生效,通常是將0xAA和0x55先后寫入PLLxFEED寄存器。

將相關參數準備好之后,就要根據參數配置,判斷選中的時鐘源,并通過計算得出最后的系統時鐘頻率。在選用外部12MHz時鐘源的條件下,程序會跳轉到CASE1的位置運行,并結合此前所給參數,計算出系統時鐘頻率CCLK=12M×2×16/1/4=96MHz。

case 1: /* Main oscillator => PLL0 */

SystemFrequency = (OSC_CLK *

((2 * ((LPC_SC->PLL0STAT & 0x7FFF) + 1))) / /*PLL0STAT的低15位是15,倍頻值*/

(((LPC_SC->PLL0STAT >> 16) & 0xFF) + 1) / /*PLL0STAT的16~23位是0,分頻值*/

((LPC_SC->CCLKCFG & 0xFF)+ 1)); /*CCLKCFG是系統分頻值,3 */

break;又例如使用32.768KHz的外低速晶振作為時鐘源,并同樣產生96MHz的系統時鐘,只需將CLKSRCSEL_Val、CCLKCFG_Val、PLL0CFG_Val分別改為0x02、0x02、0x1127(4391)即可,含義分別是選擇外部低速晶振,系統分頻為3(寄存器值比實際值小1),PLL0倍頻值為4392(而PLL0分頻值不設,默認為0),計算:32.768×2×4392÷3=95944.704KHz,

約為96MHz。

時鐘配置注意事項

在整個代碼編寫過程中要格外注意對饋送寄存器PLLxFEED的操作,要嚴格遵循0xAA和0x55先后寫入的順序。另外要確保執行寫入饋送序列時,不會出現任何一個中斷服務程序,即在執行PLL0饋送操作時,必須禁止中斷,如果寫入的值不正確、或者沒有滿足無中斷發生的條件,那么對PLL0CFG寄存器的更改都不會生效。

在根據自身需求配置所需系統時鐘頻率時,往往會使用仿真器的Debug功能,觀測相關參數,以驗證時鐘頻率配置的正確與否。但不能在執行PLL0饋送操作時,設置任何斷點,否側同樣無法使配置生效。

-

LPC

+關注

關注

8文章

137瀏覽量

79256 -

NXP

+關注

關注

61文章

1396瀏覽量

197645 -

寄存器

+關注

關注

31文章

5608瀏覽量

129996 -

lpc1754

+關注

關注

0文章

1瀏覽量

1897

原文標題:多種選擇—輕松配置LPC175x系統時鐘-ZLG技術研發中心

文章出處:【微信號:Zlgmcu7890,微信公眾號:周立功單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

探索LPC11E6x 32位ARM Cortex - M0+微控制器:特性、應用與設計要點

LTC1754-3.3/LTC1754-5:高效微功耗電荷泵DC/DC轉換器

LPC1110/11/12/13/14/15 32 位 ARM Cortex - M0 微控制器:設計與應用指南

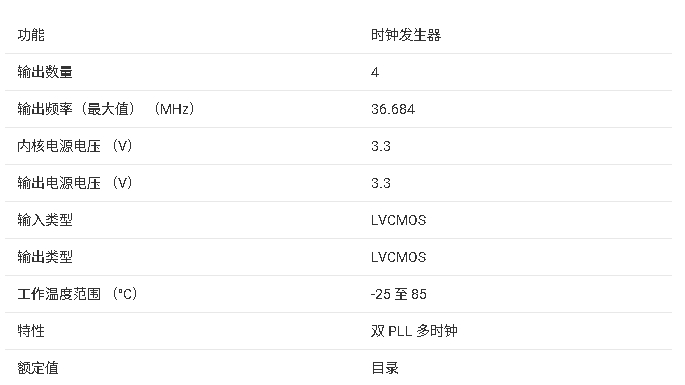

Texas Instruments PLL1705/PLL1706:3.3-V 雙 PLL 多時鐘發生器的卓越之選

Texas Instruments PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

探究PLL1705與PLL1706:3.3V雙PLL多時鐘發生器的卓越性能

德州儀器PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

LPC800系列MCU:低功耗與高性能的完美結合

修改 PLL 參數的流程

PLL1708雙PLL多時鐘發生器技術文檔總結

?PLL1707/PLL1708 雙PLL多時鐘發生器技術文檔總結

是否可以內部生成40MHz時鐘并將PLL時鐘設置為40MHz?

Analog Devices Inc. ADES1754 評估套件數據手冊

PLL用法

LPC1754內部PLL0原理及應用設計詳解

LPC1754內部PLL0原理及應用設計詳解

評論