SMT僅僅是用來提高NMOS 的速度,當工藝技術(shù)發(fā)展到45nm 以下時,半導體業(yè)界迫切需要另一種表面薄膜層應(yīng)力技術(shù)來提升PMOS 的速度。在SMT技術(shù)的基礎(chǔ)上開發(fā)出的接觸刻蝕阻擋層應(yīng)變技術(shù)(Contact Etch Stop Layer,CESL),它是利用Si3N4產(chǎn)生單軸張應(yīng)力來提升 NMOS 速度和單軸壓應(yīng)力來提升[110]晶向上PMOS速度的應(yīng)變技術(shù)。該應(yīng)變技術(shù)僅適用于45nm 及其以下工藝的短溝道器件,長溝道幾乎不會獲得好處。

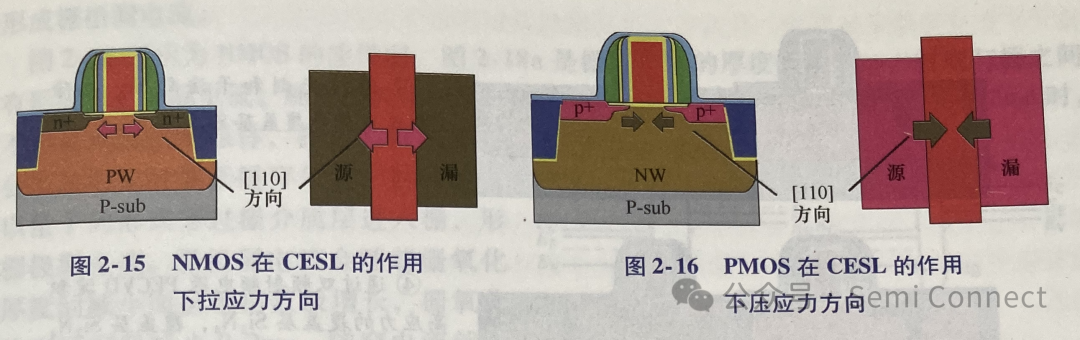

如圖2-15所示,與應(yīng)力記憶技術(shù)類似,接觸刻蝕阻擋層應(yīng)變技術(shù)也是利用覆蓋層 Si3N4會在溝道[110]方向產(chǎn)生單軸的張應(yīng)力,從而減小溝道方向的電子電導有效質(zhì)量和散射概率,提高 NMOS的速度。

如圖2-16所示,對于PMOS,接觸刻蝕阻擋層應(yīng)變技術(shù)是利用覆蓋層Si3N4在PMOS溝道[110]方向產(chǎn)生單軸的壓應(yīng)力,該方向上的壓應(yīng)力可以使價帶能帶發(fā)生分裂,重空穴帶離開價帶頂,輕空穴帶占據(jù)價帶頂,從而減小溝道方向的空穴的電導有效質(zhì)量,提高PMOS的速度。

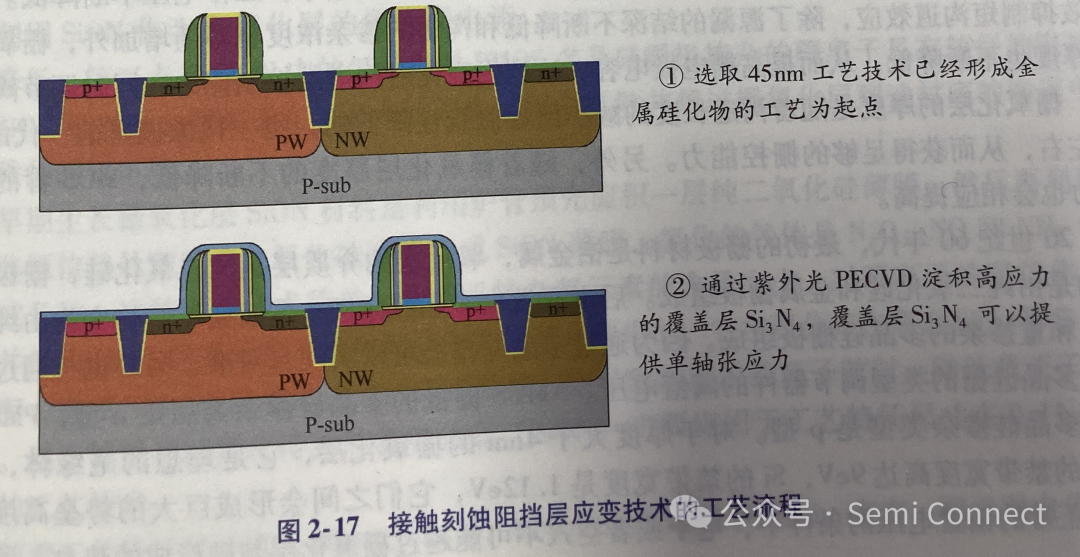

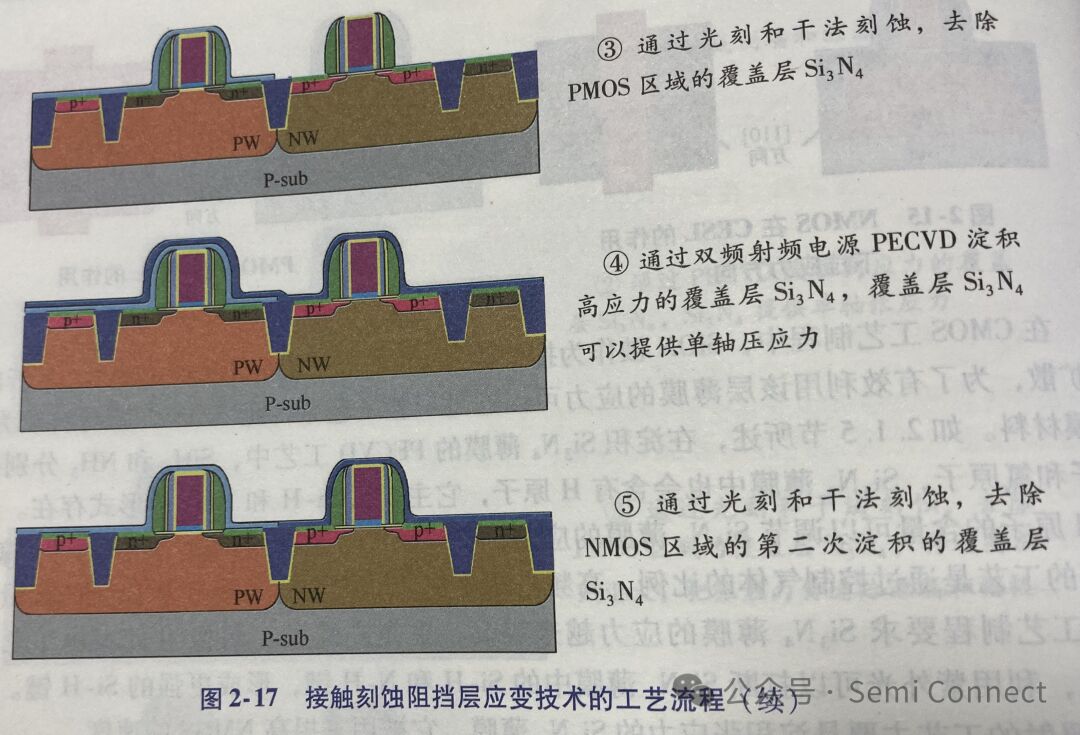

在CMOS 工藝制程中,SiON 被作為接觸孔刻蝕阻擋層和防止 BPSG中的B、P析出向襯底擴散,為了有效利用該層薄膜的應(yīng)力可以通過調(diào)整工藝條件把SiON 薄膜材料改為Si3N4薄膜材料。如2.1.5節(jié)所述,在淀積Si3N4薄膜的 PECVD工藝中,SiN4和NH3分別提供硅原子和氮原子,Si3N4薄膜中也會含有H 原子,它主要以Si-H和N-H的形式存在。通過改變H原子的含量可以調(diào)節(jié)Si3N4薄膜的應(yīng)力,H原子的含量越高Si3N4薄膜的應(yīng)力就越小,早期的工藝是通過控制氣體的比例、高頻電源功率和反應(yīng)溫度來調(diào)節(jié)H 原子的含量,但是隨著工藝制程要求Si3N4薄膜的應(yīng)力越來越高,更先進的工藝制程中引入紫外光照射條件,利用紫外光可以打斷Si3N4薄膜中的Si-H和N-H 鍵,形成更強的Si-H鍵。利用紫外光照射的工藝主要是淀積張應(yīng)力的Si3N4薄膜,它被用來提高 NMOS 的速度。

與淀積張應(yīng)力的Si3N4薄膜不同,可以利用雙頻射頻電源的PECVD淀積壓應(yīng)力的Si3N4薄膜,雙頻射頻電源是指它包含高頻射頻電源和低頻電源。淀積壓應(yīng)力的Si3N4薄膜的氣體源除了包含SiN4和NH3外,還包含H2和Ar(或者N2)。利用高頻射頻電源可以電解重原子氣體 Ar,形成Ar+等離子體(或者稱為 Plasma),再利用低頻電源加速 Ar+離子形成高能離子體,然后利用高能離子的體轟擊效應(yīng),使得Si3N4薄膜更為致密,形成壓應(yīng)力。

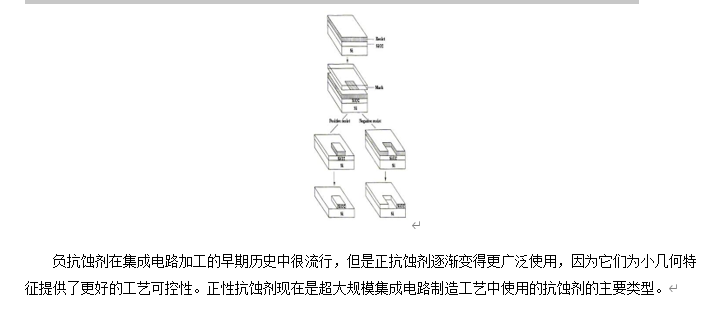

圖2-17所示為接觸刻蝕阻擋層應(yīng)變技術(shù)的工藝流程。

-

PMOS

+關(guān)注

關(guān)注

4文章

271瀏覽量

31609 -

工藝流程

+關(guān)注

關(guān)注

7文章

118瀏覽量

16856 -

刻蝕

+關(guān)注

關(guān)注

2文章

220瀏覽量

13777

原文標題:接觸刻蝕阻擋層應(yīng)變技術(shù)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

詳解原子層沉積薄膜制備技術(shù)

非接觸式應(yīng)變測量技巧

13um應(yīng)變補償多量子阱SLD臺面制作工藝的研究

選擇性發(fā)射極晶體硅太陽電池實現(xiàn)方法分析

【轉(zhuǎn)帖】干法刻蝕的優(yōu)點和過程

請教碳化硅刻蝕工藝

ITO玻璃技術(shù)之SiO2阻擋膜層規(guī)格

晶片清洗、阻擋層形成和光刻膠應(yīng)用

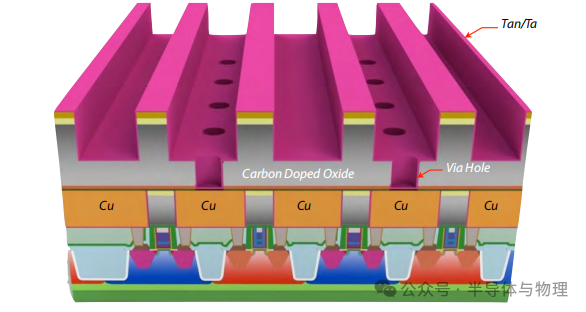

一文了解金屬互連中阻擋層

半導體boe刻蝕技術(shù)介紹

為什么LED芯片正電極要插入二氧化硅電流阻擋層,而負極沒有?

接觸刻蝕阻擋層應(yīng)變技術(shù)介紹

接觸刻蝕阻擋層應(yīng)變技術(shù)介紹

評論