隨著集成電路的快速發(fā)展及其應(yīng)用領(lǐng)域的不斷擴(kuò)大,通信業(yè)界對(duì)于大規(guī)模集成電路的小型化、高速、低電源電壓、低功耗和高性價(jià)比等方面的要求越來(lái)越高。雖然傳統(tǒng)的雙極型工藝集成電路具有高速度、強(qiáng)電流驅(qū)動(dòng)和高模擬精度等方面的優(yōu)點(diǎn),但雙極型工藝集成電路在功耗和集成度方面卻無(wú)法滿足 VLSI 系統(tǒng)集成多方面的發(fā)展需要,而CMOS 工藝集成電路在低功耗、高度集成和強(qiáng)抗干擾能力等方面有著雙極型工藝集成電路無(wú)法比擬的優(yōu)勢(shì),但是20 世紀(jì)70、80年代的CMOS 工藝集成電路速度低、驅(qū)動(dòng)能力差,它只能滿足低速的數(shù)字集成電路和小功率模擬集成電路的要求。由此可見,無(wú)論是單一早期落后的CMOS 工藝制程技術(shù),還是單一的雙極型工藝制程技術(shù)都無(wú)法滿足 VLSI 系統(tǒng)集成多方面性能的要求,因此只有融合CMOS 工藝制程技術(shù)和雙極型工藝制程技術(shù)這兩種工藝制程技術(shù)各自的優(yōu)點(diǎn),才能滿足早期 VLSI 系統(tǒng)集成多方面的要求,制造具有CMOS 工藝制程技術(shù)和雙極型工藝制程技術(shù)特點(diǎn)的BiCMOS工藝制程技術(shù)才是早期 VLSI發(fā)展的必然產(chǎn)物。BiCMOS 是雙極-互補(bǔ)金屬氧化物半導(dǎo)體,簡(jiǎn)單來(lái)說(shuō)BiCMOS 工藝制程技術(shù)是將雙極型器件和CMOS 器件同時(shí)制造在同一芯片上,發(fā)揮它們各自的優(yōu)勢(shì),克服各自的缺點(diǎn),綜合雙極型器件的高跨導(dǎo)、強(qiáng)驅(qū)動(dòng)能力和CMOS 器件的低功耗、高集成度的優(yōu)點(diǎn),使BiCMOS 工藝集成電路集高速度、高集成度和低功耗于一體,為高速、高集成度、高性能及強(qiáng)驅(qū)動(dòng)的集成電路發(fā)展開辟了一條新的道路。

按照基本工藝制程技術(shù)的類型,BiCMOS 工藝制程技術(shù)又可以分為以 CMOS 工藝制程技術(shù)為基礎(chǔ)的 BiCMOS 工藝制程技術(shù),或者以雙極型工藝制程技術(shù)為基礎(chǔ)的 BiCMOS 工藝制程技術(shù)。以CMOS 工藝制程技術(shù)為基礎(chǔ)的BiCMOS工藝制程技術(shù)對(duì)保證MOS 器件的性能比較有利,而以雙極型工藝制程技術(shù)為基礎(chǔ)的BiCMOS工藝制程技術(shù)對(duì)保證雙極型器件的性能比較有利。由于實(shí)際應(yīng)用中,影響 BiCMOS 器件性能的主要是雙極型晶體管部分,因此以雙極型工藝制程技術(shù)為基礎(chǔ)的 BiCMOS 工藝制程技術(shù)較為常用。

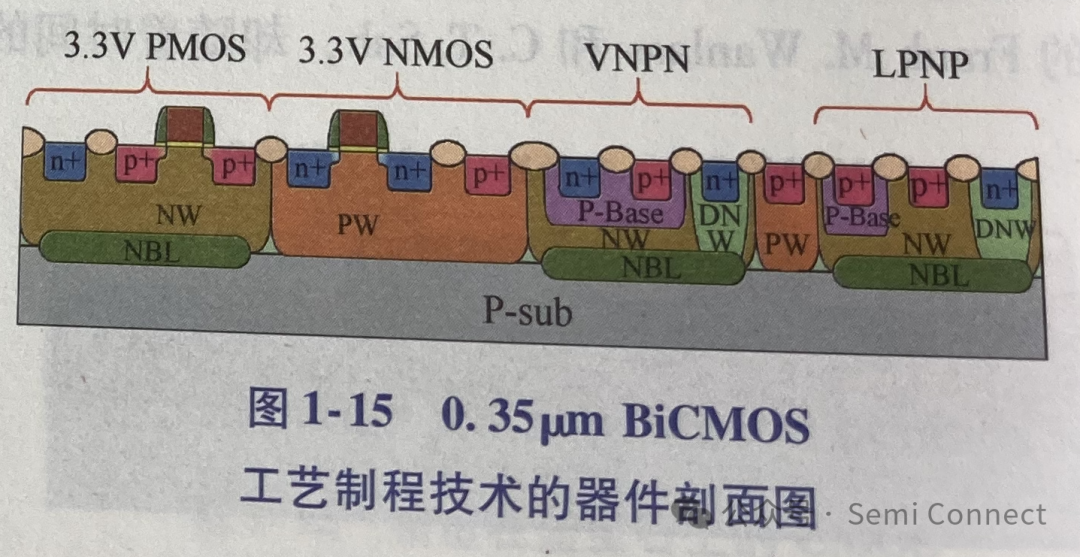

圖1-15所示為0.35μmBiCMOS 工藝制程技術(shù)的器件剖面圖。它是以傳統(tǒng)CMOS 工藝制程技術(shù)為基礎(chǔ),增加少量的工藝步驟而成。它包含 3.3V NMOS、3.3V PMOS、縱向 NPN結(jié)構(gòu)(VNPN)和橫向PNP結(jié)構(gòu) (LPNP)。

BiCMOS 工藝集成電路的基本設(shè)計(jì)思想是芯片內(nèi)部核心邏輯部分采用CMOS器件為主要單元門電路,而輸入輸出緩沖電路和驅(qū)動(dòng)電路要求驅(qū)動(dòng)大電容負(fù)載,所以輸入輸出緩沖電路和驅(qū)動(dòng)電路使用雙極型器件,這是最早的 BiCMOS 工藝集成電路的設(shè)計(jì)方案。因此BiCMOS 工藝集成電路既具有CMOS 工藝集成電路的高集成度和低功耗的優(yōu)點(diǎn),又獲得了雙極型工藝集成電路的高速和強(qiáng)電流驅(qū)動(dòng)能力的優(yōu)勢(shì)。

隨著 BiCMOS工藝制程技術(shù)的不斷進(jìn)步,在更先進(jìn)的 BiCMOS 工藝制程技術(shù)中,設(shè)計(jì)人員已經(jīng)可以將雙極型器件也集成到邏輯門中,因?yàn)檫@樣可以大幅提升邏輯門的速度,雖然加入雙極型器件的邏輯門會(huì)增加大概10%~20%的面積,但是考慮到其負(fù)載能力的增強(qiáng),與CMOS 邏輯門相比,在相同驅(qū)動(dòng)能力條件下,BiCMOS 邏輯門的實(shí)際集成度還是有很大的提升。另外與CMOS邏輯門類似,BiCMOS 邏輯門電路的輸出端兩管輪番導(dǎo)通,所以這種 BiCMOS 邏輯門的靜態(tài)功耗幾乎接近于零,而且在同樣的設(shè)計(jì)尺寸下,BiCMOS 邏輯門的速度會(huì)更加快。

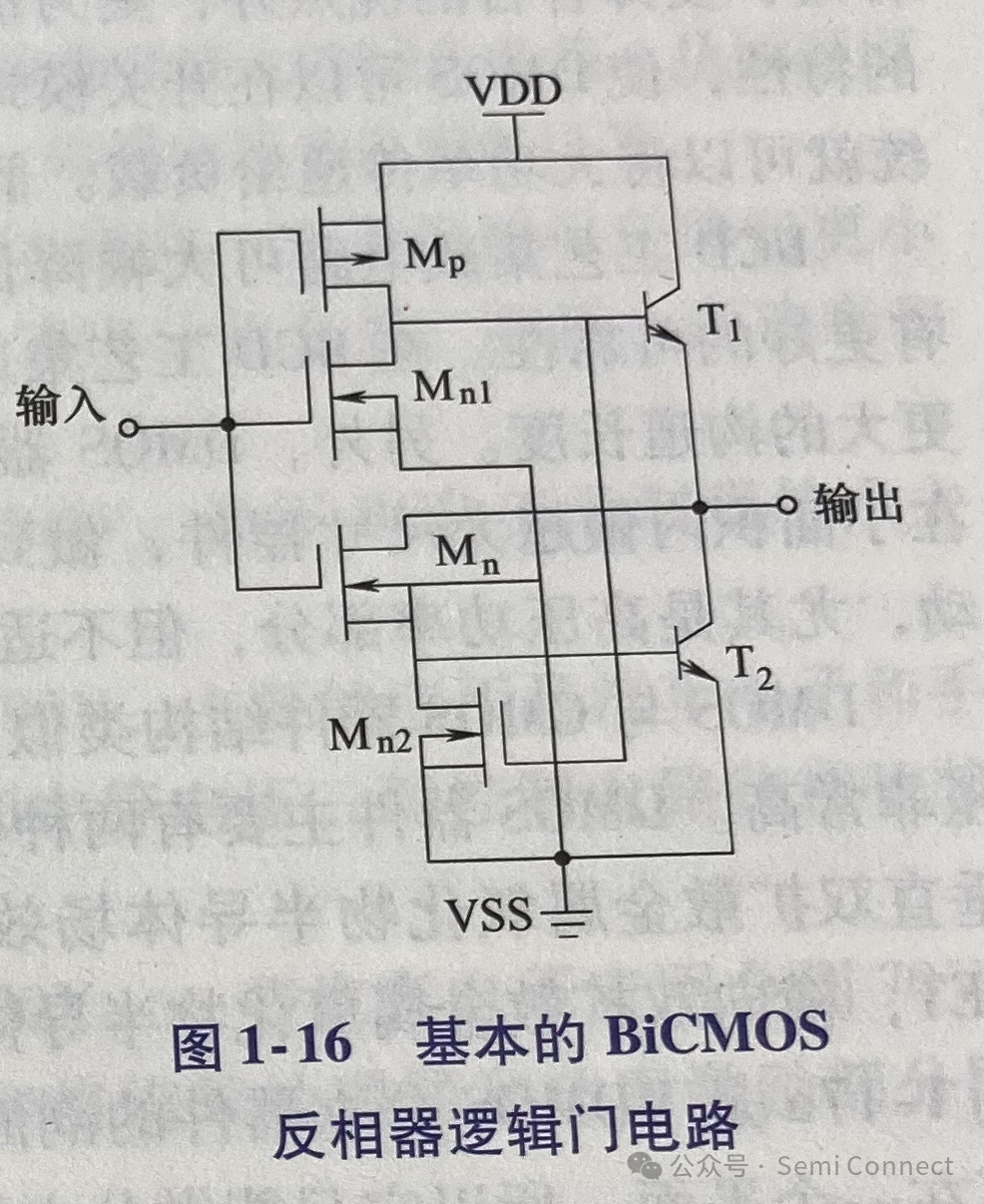

圖1-16所示為基本的BiCMOS 反相器邏輯門電路,為了使表達(dá)起來(lái)更清楚,MOS 器件用符號(hào)Mn和Mp表示,Mn表示 NMOS,Mp表示 PMOS,雙極型器件用T表示。T1和T2構(gòu)成推拉式輸出級(jí),而Mp、Mn、Mn1和Mn2所組成的輸入級(jí)與基本的CMOS 反相器邏輯門的輸入級(jí)很相似。輸入信號(hào)同時(shí)作用于 Mp和Mn的柵極。當(dāng)輸入信號(hào)為高電壓時(shí)Mn導(dǎo)通而Mp截止;而當(dāng)輸入信號(hào)為低電壓時(shí),情況則相反,Mp導(dǎo)通,Mn截止。當(dāng)輸出端有同類 BiCMOS 邏輯門電路時(shí),輸出級(jí)能提供足夠大的電流為電容性負(fù)載充電。同理,已充電的電容負(fù)載也能迅速地通過(guò)T2放電。

上述電路中T1和T2的基區(qū)存儲(chǔ)電荷亦可通過(guò)Mn1和Mn2釋放,以加快電路的開關(guān)速度。當(dāng)輸入信號(hào)為高電壓時(shí)Mn1導(dǎo)通,T1基區(qū)的存儲(chǔ)電荷迅速消散。這種作用與TTL門電路的輸入級(jí)中T1類似。同理,當(dāng)輸入信號(hào)為低電壓時(shí),電源電壓 VDD 通過(guò) Mp提供激勵(lì)使 Mn2導(dǎo)通,顯然T2基區(qū)的存儲(chǔ)電荷通過(guò) Mn2而釋放。所以門電路的開關(guān)速度可得到有效的改善。

在功耗方面,以32位的CPU采用CMOS 工藝制程技術(shù)為例,CPU芯片外主線要有較大的帶電容負(fù)載的能力。32位的CPU 包含有10個(gè)或者更多的接口器件,但同一時(shí)間內(nèi)只有一條主線是激活的,即每一條主線有90%的時(shí)間不工作。如果采用雙極工藝制程技術(shù)制作傳統(tǒng)的接口驅(qū)動(dòng)電路可以保證數(shù)據(jù)傳輸速度,但是功耗卻大了些。因?yàn)閱渭冸p極型接口驅(qū)動(dòng)電路,即使接口驅(qū)動(dòng)電路不被激活時(shí)它也在不停地消耗功率,所以整個(gè)CPU 的靜態(tài)功耗非常大。如果利用 BiCMOS 工藝制程技術(shù)制造接口驅(qū)動(dòng)電路,則不被激活的接口驅(qū)動(dòng)電路功耗非常小,在很多情況下,靜態(tài)功耗可以節(jié)省接近100%,而傳統(tǒng)主線接口驅(qū)動(dòng)電路的功耗約占整個(gè)系統(tǒng)功耗的30%,所以這種省電效果非常顯著,因而特別適用于手機(jī)、個(gè)人數(shù)字處理器和筆記本電腦等一類使用電池的通信、計(jì)算機(jī)和網(wǎng)絡(luò)設(shè)備中。更為有利的是,BiCMOS數(shù)字集成電路的速度與先進(jìn)的雙極型電路不相上下,這與高速數(shù)字通信系統(tǒng)的速度要求是相適應(yīng)的。

目前,BiCMOS 工藝制程技術(shù)主要用于 RF電路、LED 控制驅(qū)動(dòng)和 IGBT 控制驅(qū)動(dòng)等芯片設(shè)計(jì),對(duì)于高度集成的片上系統(tǒng)(SOC)芯片設(shè)計(jì),CMOS 工藝制程技術(shù)還是最理想的選擇。

-

集成電路

+關(guān)注

關(guān)注

5452文章

12572瀏覽量

374554 -

制程技術(shù)

+關(guān)注

關(guān)注

1文章

42瀏覽量

11417 -

BiCMOS

+關(guān)注

關(guān)注

0文章

124瀏覽量

20669 -

工藝制程

+關(guān)注

關(guān)注

0文章

59瀏覽量

13251

原文標(biāo)題:BiCMOS 工藝制程技術(shù)簡(jiǎn)介

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

哪位大俠有SiGe Bipolar或BiCMOS工藝的介紹

COMS工藝制程技術(shù)與集成電路設(shè)計(jì)指南

半導(dǎo)體工藝幾種工藝制程介紹

采用SiGe:C BiCMOS工藝技術(shù)的射頻/微波產(chǎn)品

制程工藝是什么?

CMOS工藝制程技術(shù)的詳細(xì)資料說(shuō)明

BiCMOS工藝流程介紹

雙極型工藝制程技術(shù)簡(jiǎn)介

PMOS工藝制程技術(shù)簡(jiǎn)介

HV-CMOS工藝制程技術(shù)簡(jiǎn)介

BiCMOS工藝制程技術(shù)簡(jiǎn)介

BiCMOS工藝制程技術(shù)簡(jiǎn)介

評(píng)論