中斷操作三個步驟:

1、中斷初始化

void intr_init(){//configure PLIC//cpu 0 accept all interrupts with priority above 0plic_set_threshold(BSP_PLIC, BSP_PLIC_CPU_0, 0);//enable SYSTEM_PLIC_USER_INTERRUPT_A_INTERRUPT rising edge interruptplic_set_enable(BSP_PLIC, BSP_PLIC_CPU_0, SYSTEM_PLIC_SYSTEM_AXI_A_INTERRUPT, 1);plic_set_priority(BSP_PLIC, SYSTEM_PLIC_SYSTEM_AXI_A_INTERRUPT, 1);//enable interrupts//Set the machine trap vector (../common/trap.S)csr_write(mtvec, trap_entry);//Enable external interruptscsr_set(mie, MIE_MEIE);csr_write(mstatus, MSTATUS_MPP | MSTATUS_MIE);}

其中包括設置中斷門限。相應中斷的使能,以及中斷的優先級,數字越大,優先級越高。然后還有中斷入中數據的保存。

2、trap處理

void trap(){int32_t mcause = csr_read(mcause);//Interrupt if true, exception if falseint32_t interrupt = mcause < 0;int32_t cause = mcause & 0xF;if(interrupt){switch(cause){case CAUSE_MACHINE_EXTERNAL: axiInterrupt(); break;default: crash(); break;}} else {crash();}}

3、用戶中斷處理

void axiInterrupt(){uint32_t claim;//While there is pending interruptswhile(claim = plic_claim(BSP_PLIC, BSP_PLIC_CPU_0)){switch(claim){case SYSTEM_PLIC_SYSTEM_AXI_A_INTERRUPT:bsp_print("Entered AXI Interrupt Routine, Passed!");break;default: crash(); break;}//unmask the claimed interruptplic_release(BSP_PLIC, BSP_PLIC_CPU_0, claim);}}

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

中斷處理

+關注

關注

0文章

96瀏覽量

11488 -

RISC-V

+關注

關注

49文章

2909瀏覽量

53208

發布評論請先 登錄

相關推薦

熱點推薦

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

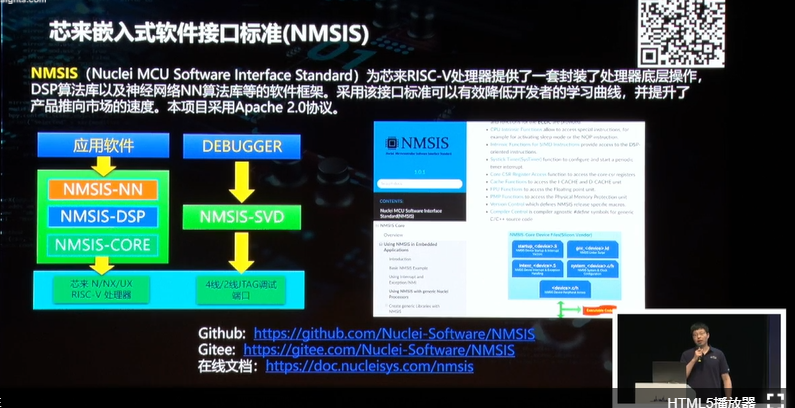

隨著 RISC -V處理器在 FPGA 領域的廣泛應用,易靈思 FPGA 的 Sapphire RISC-V 內核憑借軟硬核的靈活支持,為開發者提供多樣選擇。本文深入探討 Sapph

RISC-V架構及MRS開發環境回顧

—— CH32V103系列MCU。作為長久以來對RISC-V架構關注和研究的成果, RISC-V3A處理器,支持IMAC指令子集,內嵌了PFIC中斷

發表于 12-16 23:08

如何在RISC-V處理器上使用FreeRTOS?

FreeRTOS內核調用哪個外部中斷處理程序,設置外部中斷handler的名稱步驟如下:1 加載RISC-V芯片供應商提供的外部

發表于 11-29 15:54

學習RISC-V入門 基于RISC-V架構的開源處理器及SoC研究

RISC-V架構的開源處理器與SoC。1 RISC-V簡介1.1 RISC-V的基本設計RISC-V是一

發表于 07-27 18:09

FreeRTOS與RISC-V——適用于RISC-V的FreeRTOS概述

1.1簡介FreeRTOS中面向RISC-V的接口是易于拓展的,其提供了一系列基本的接口,用于操作適用于所有RISC-V實現中的通用寄存器,以及一系列的宏來處理特定的硬件實現中涉及到的

發表于 04-09 09:26

Sifive Learn Inventor基礎之GPIO 按鍵中斷 RISC-V

Sifive Learn Inventor 基礎之gpio 按鍵中斷Sifive Learn Inventor是Sifive的一款基于RISC-V內核的開發板,具體見官網的Hifive Rev b

發表于 12-20 19:06

?1次下載

RISC-V高性能計算需要要解決的三個問題

尤其是在 2022 年,RISC-V 的發展勢頭極為強勁,RISC-V 處理器核出貨量突破 100 億顆。

發表于 02-15 11:53

?1028次閱讀

MCU如何處理中斷?中斷處理過程包括哪些步驟?

當MCU接收到一個中斷信號時,它會暫停當前正在執行的任務,保存現場,然后跳轉到預設的中斷處理程序(Interrupt Service Routine, ISR)去處理這個

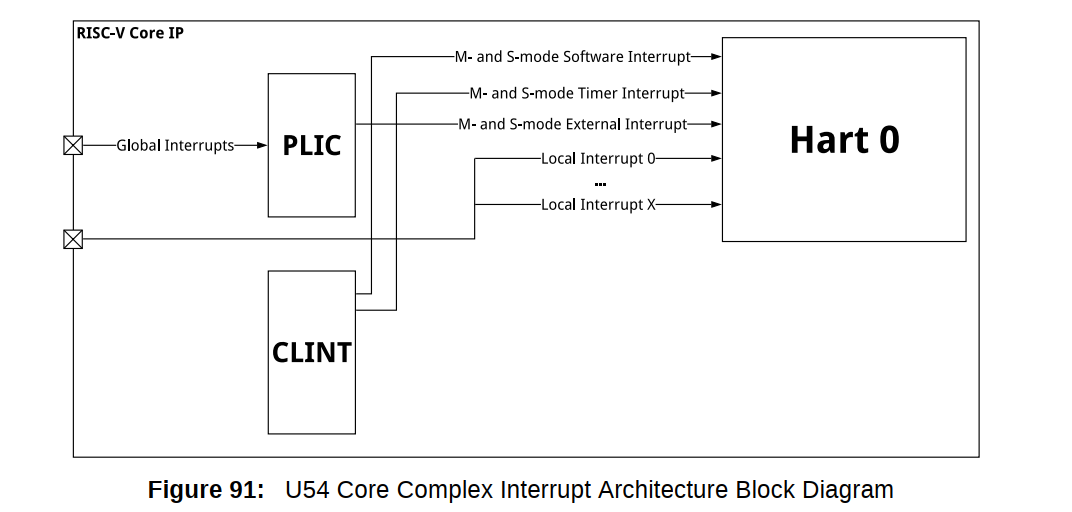

RISC-V怎么實現核間中斷?核心本地中斷控制器(CLINT)深度解析

全稱為Core Local Interruptor(核心本地中斷控制器),是 RISC-V 特權架構規范(Privileged Architecture Specification)中明確定義的內建

RISC-V的中斷處理 中斷操作三個步驟

RISC-V的中斷處理 中斷操作三個步驟

評論