易靈思RAM在使用時可以會遇到一些問題,這里把常用的問題總結下。

1、ram初始化文件路徑是工程路徑

在對ram進行初始化時需要指定文件路徑,這里要注意'/'的方向。

(1)如果文件放在工程目錄下,寫法如下:

.RAM_INIT_FILE("./ram_init_file.inithex" )

或者.RAM_INIT_FILE("ram_init_file.inithex" )

(2)如在工程目錄下新建一個src文件。寫法如下:

.RAM_INIT_FILE("./src/ram_int_file.mem")

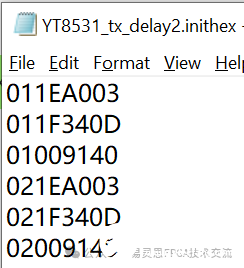

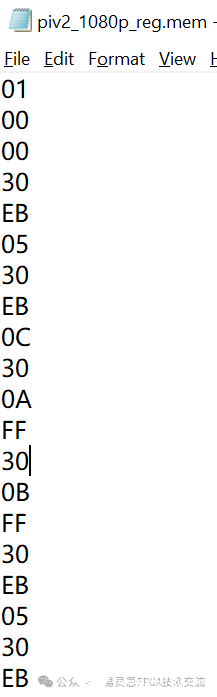

2.初始化文件格式

初始化文件支持.inithex和.mem.都是按順序以16進制輸入數據即可。

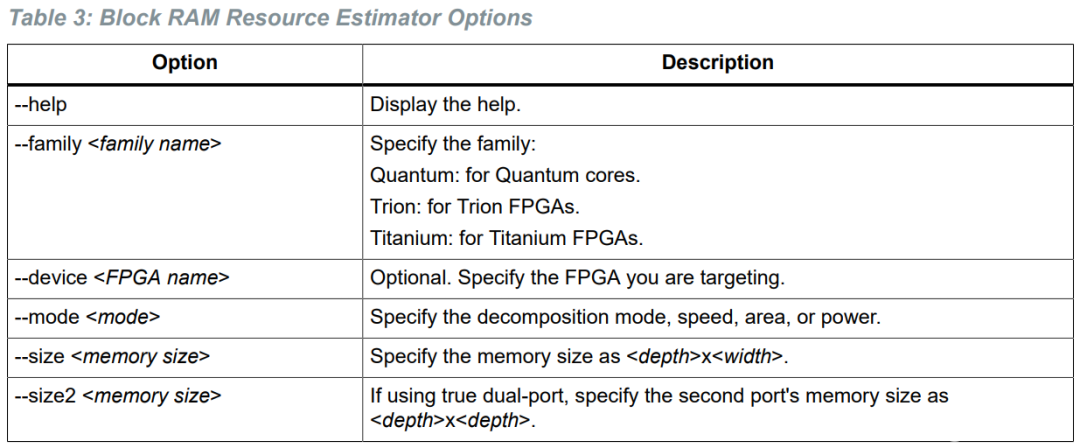

3、在RAM評估器中評估RAM資源

易靈思提供了RAM資源評估器,可以快速幫忙評估RAM資源的使用情況。以下為操作步驟:

(1)把路徑轉換Efinity路徑下的bin文件夾下。

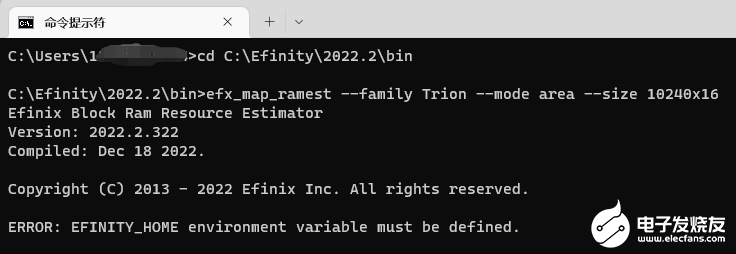

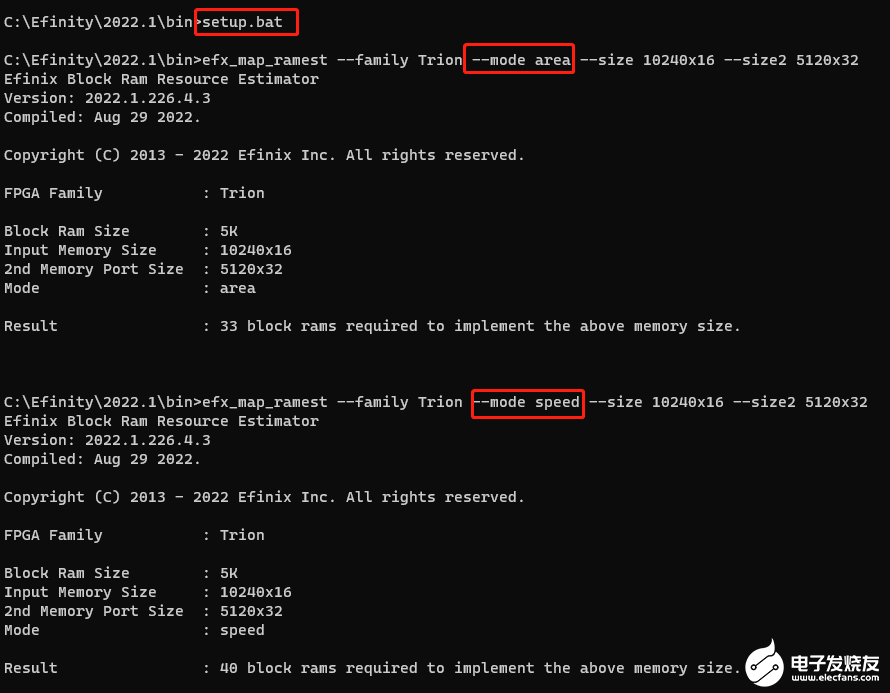

(2)通過以下命令評估

efx_map_ramest --family Trion --mode area --size 10240x16

但是如果直接運行該命令會提示錯誤。

因為efinity的路徑沒有寫入系統路徑,用windows 命令行的時候,需要先運行bin文件夾下的setup.bat來設置環境,然后運行命令,注意不同模式下資源使用量不同。

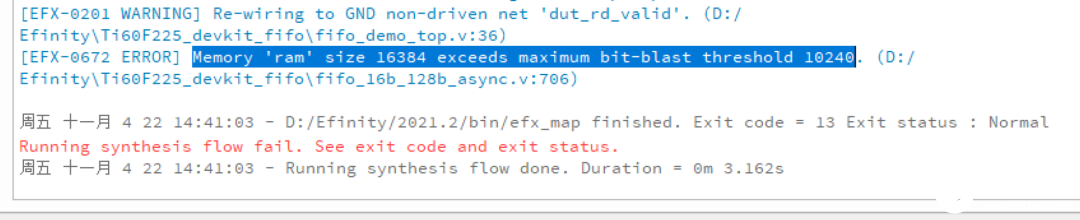

4、大塊ram的使用

如果RAM資源使用比較多時,可能會報出以下錯誤。

解決方案

在工程目錄下放置以下文件 文件名:efx_map_settings.ini

并在文件中輸入下面語句:max-bit-blast-mem-size = 524300

在2023.1及以后的版本已經不需要上面的ini文件解決方案。

4)RAM使用報錯

(1)ERROR: RCLK port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 is constant

ERROR: EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 WCLK port is disabled, but WCLKE is not

ERROR: EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 WCLK port is disabled, but WE is not

ERROR: WDATA[0] port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 is not disabled in a disabled mode

ERROR: RCLK port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$2 is constant

ERROR: EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$2 WCLK port is disabled, but WE is not

ERROR: WDATA[0] port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$2 is not disabled in a disabled mode

錯誤原因:FIFO時鐘給的是無效的。

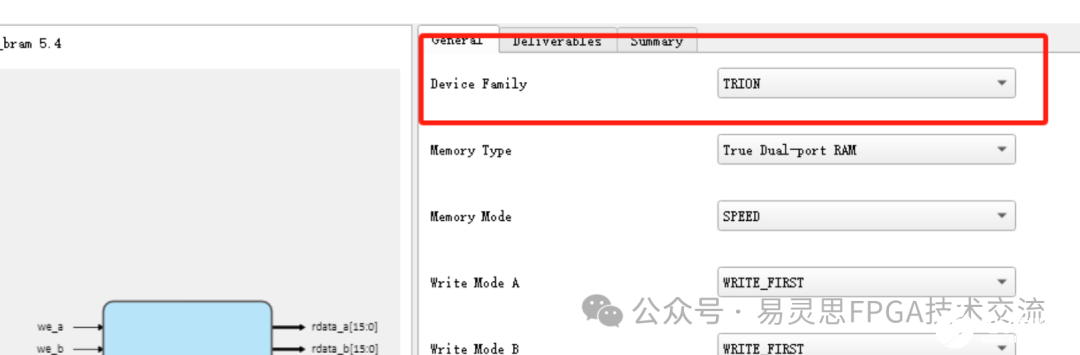

[EFX-0473 ERROR] EFX_DPRAM_5K 'genblkl.dpramsk' illegal instantiation for OPx device. (F:lcvzltestproiectMX efinity proilipltdp ram 16x1024 dlltdp ram 16x1024 d1.y'824)

錯誤原因:注意器件的family要對應下來。

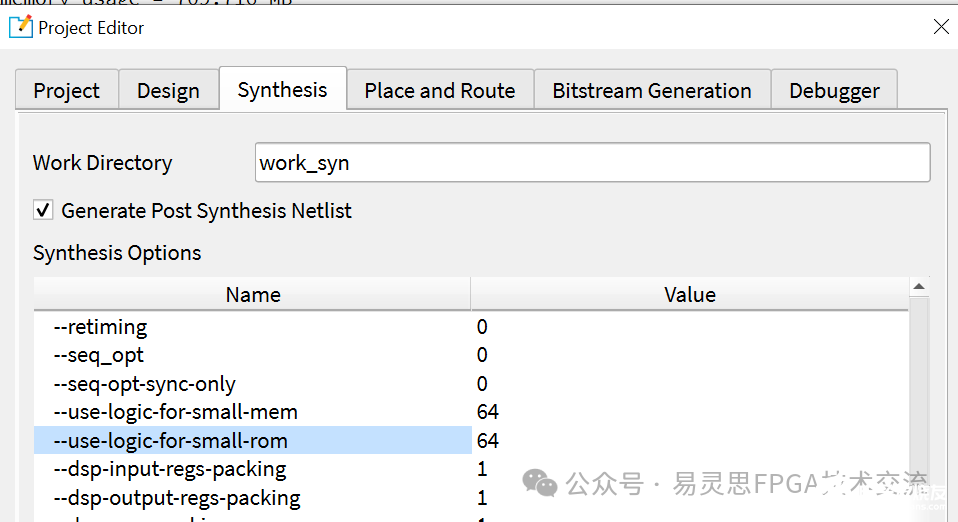

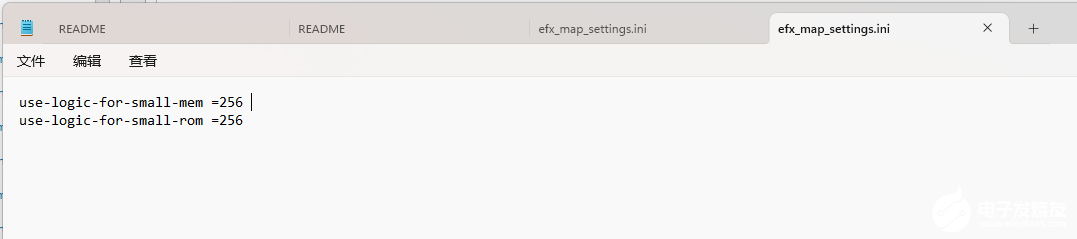

5、如果要把小于256bit的ram綜合成register,可以在工程目錄下新建一個efx_map_settings.ini文件。并在文件中輸入以下兩句:

use-logic-for-small-mem=256use-logic-for-small-rom=256

在2023.1及以后的軟件提供了相關的選項。

6、RAM綜合的其它操作請參考efinity-synthesis.pdf

這里包括對使能,復位等的寫法的注意事項。

審核編輯 黃宇

-

RAM

+關注

關注

8文章

1399瀏覽量

120544 -

易靈思

+關注

關注

6文章

64瀏覽量

5541

發布評論請先 登錄

探索MXD1210非易失性RAM控制器:特性、應用與設計要點

基于易靈思eMMC IP的Linux系統加載方案

易靈思助力2025年全國大學生嵌入式芯片與系統設計競賽圓滿落幕

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

易靈思助力上海集成電路緊缺人才培訓項目順利結課

易靈思2025 FPGA技術研討會成都站圓滿收官

易靈思與思特威第二屆機器視覺方案大會圓滿收官

睿思芯科靈羽處理器獲得國家級權威認可

易靈思與南京大學集成電路學院暑期課程圓滿結課

淺談wsl --update` 命令行選項無效的解決方案

易靈思邀您相約2025上海國際汽車工業展覽會

易靈思RAM使用--Update5

易靈思RAM使用--Update5

評論