AMD或向UCIe靠攏?

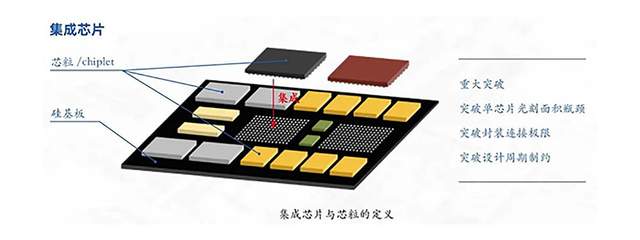

盡管AMD早在幾年前便率先探索Chiplet(小芯片)設計的可能性,其中包括自行開發(fā)的Infinity Fabric高速互聯(lián)技術(shù)。然而今時今日,他們正考慮采納共享于英特爾等十家頂級科技公司的通用Chiplet的高速互聯(lián)標準——UCIe。

眼下,眾多的EPYC、Ryzen以及Instinct MI300系列芯片均依賴自研的Infinity Fabric技術(shù)完成小芯片間的連接,不過這一技術(shù)仍未避免延遲及能量效率不足的缺陷。此外,由于這是AMD獨有的專利技術(shù),其他第三方無法獲準運用,因此在與其他廠商的小芯片互聯(lián)過程中勢必面臨兼容性挑戰(zhàn)。

對比之下,英特爾發(fā)起的通用Chiplet的高速互聯(lián)標準——UCIe,它致力于確立一套開源且易互操作的標準。通過先進封裝技術(shù),多個來自不同供應商的小芯片可聚集一處,并得以實現(xiàn)高效的互聯(lián)互通。

AMD闡釋,UCIe不僅可以充當小芯片生態(tài)系統(tǒng)和數(shù)據(jù)庫,同時也是第三方實施模塊化Chiplet設計的契機;用戶只須自產(chǎn)核心的小芯片,其余模塊則可選配采用UCIe標準化的外來產(chǎn)品,如此可以有無限可能的組合,從而加速產(chǎn)品上市速度。然而想要實現(xiàn)這一境界的關(guān)鍵在于必須有均勻的互連標準以及成熟的設計平臺支持。

盡管AMD積極參與UCIe標準聯(lián)盟的行動,并有高管表達出對采用UCIe標準構(gòu)建小芯片的興趣所在,但最終是否將推出相應產(chǎn)品尚需進一步觀望。

-

amd

+關(guān)注

關(guān)注

25文章

5689瀏覽量

140019 -

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13605 -

UCIe

+關(guān)注

關(guān)注

0文章

53瀏覽量

2019

發(fā)布評論請先 登錄

多Chiplet異構(gòu)集成的先進互連技術(shù)

Robotec.ai與AMD Silo AI的合作實踐

西門子EDA如何推動Chiplet技術(shù)商業(yè)化落地

得一微電子受邀出席第四屆HiPi Chiplet論壇

UCIe協(xié)議代際躍遷驅(qū)動開放芯粒生態(tài)構(gòu)建

解構(gòu)Chiplet,區(qū)分炒作與現(xiàn)實

新思科技UCIe IP解決方案實現(xiàn)片上網(wǎng)絡互連

線控轉(zhuǎn)向直流無刷電機的控制策略研究

技術(shù)資訊 I 完整的 UCIe 信號完整性分析流程和異構(gòu)集成合規(guī)性檢查

Chiplet與先進封裝設計中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進封裝

將SPSDK for FRDM-MCX-W71 SDK與VS一起安裝時出現(xiàn)hidapi構(gòu)建錯誤怎么解決?

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

Chiplet:芯片良率與可靠性的新保障!

AMD將轉(zhuǎn)向UCIe構(gòu)建Chiplet

AMD將轉(zhuǎn)向UCIe構(gòu)建Chiplet

評論