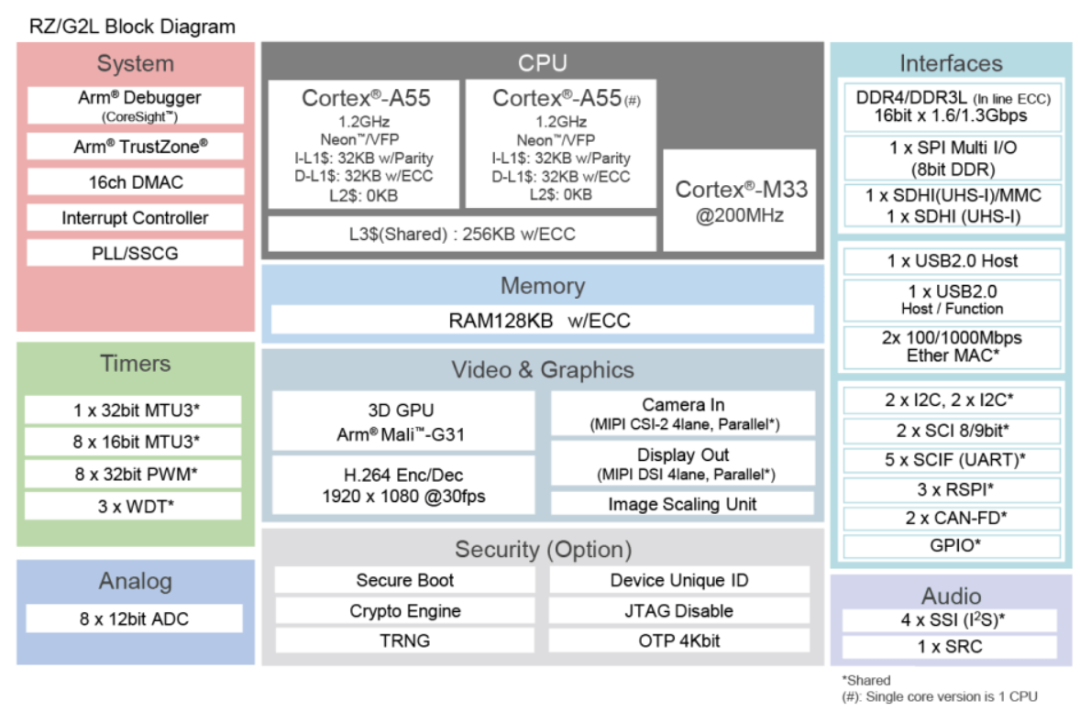

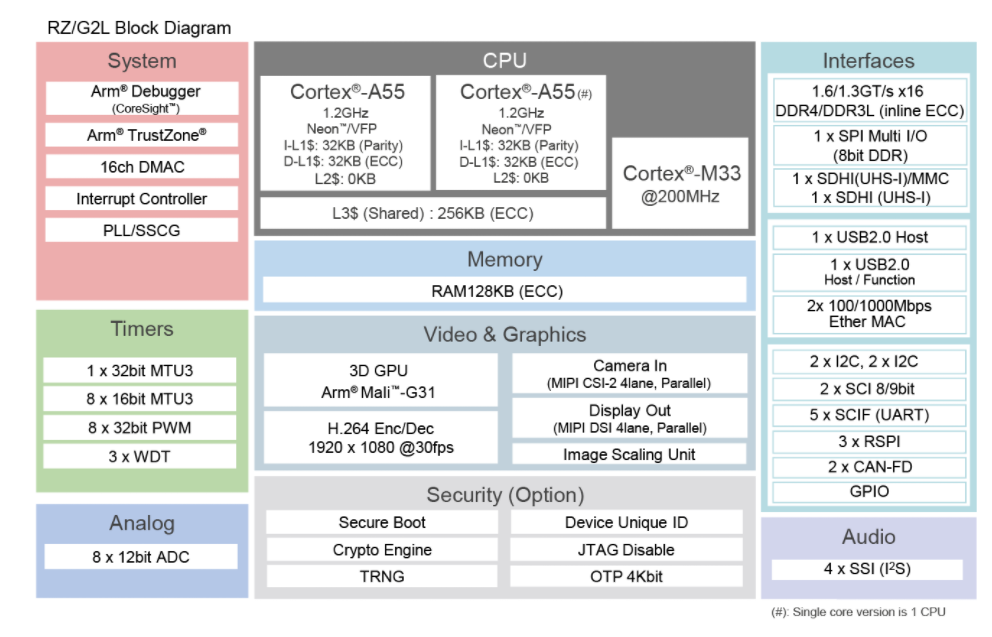

RZ/G2L微處理器配備Cortex-A55 (1.2 GHz) CPU、16位DDR3L/DDR4接口、帶Arm Mali-G31的3D圖形加速引擎以及視頻編解碼器(H.264)。此外,這款微處理器還配備有大量接口,如攝像頭輸入、顯示輸出、USB 2.0和千兆以太網,因此特別適用于入門級工業人機界面(HMI)和具有視頻功能的嵌入式設備等應用。

ECC是一種用于檢測和糾正內存數據中的錯誤的機制,用于高可靠性應用場景。

ECC有如下方案

邊帶ECC

內聯ECC

片上ECC

鏈接ECC

從G2L框圖可見,支持DDR in-line ECC功能。

RZ/G2L系列板上的內存控制器提供可選的ECC功能,可用于驗證內存中的數據并在發生內存錯誤時糾正它們。內存控制器將檢查所有讀取事務中的數據以及校驗錯誤。

ECC工作原理是創建獨特的“校驗碼”,這些校驗碼是對稱為“ECC數據字”的對齊數據段中的信息進行數學描述。

校驗碼始終與整個ECC數據字相關聯,并且可以在內存控制器內部用于所有內存讀取,以控制數據的準確性。“在線”ECC將這些校驗碼存儲在內存中,該內存對用戶不可見。

內存控制器將ECC錯誤定義為“可糾正的”或“不可糾正的”。可糾正的錯誤是校驗碼或數據中的一位錯誤。控制器使用綜合特征來確定哪個位出現錯誤并可以糾正錯誤。不可糾正的錯誤是校驗碼或數據中的雙位錯誤。在這種情況下,控制器可以識別校驗碼或數據中不正確的2位,但無法準確確定哪2位有錯誤,因此無法糾正錯誤。

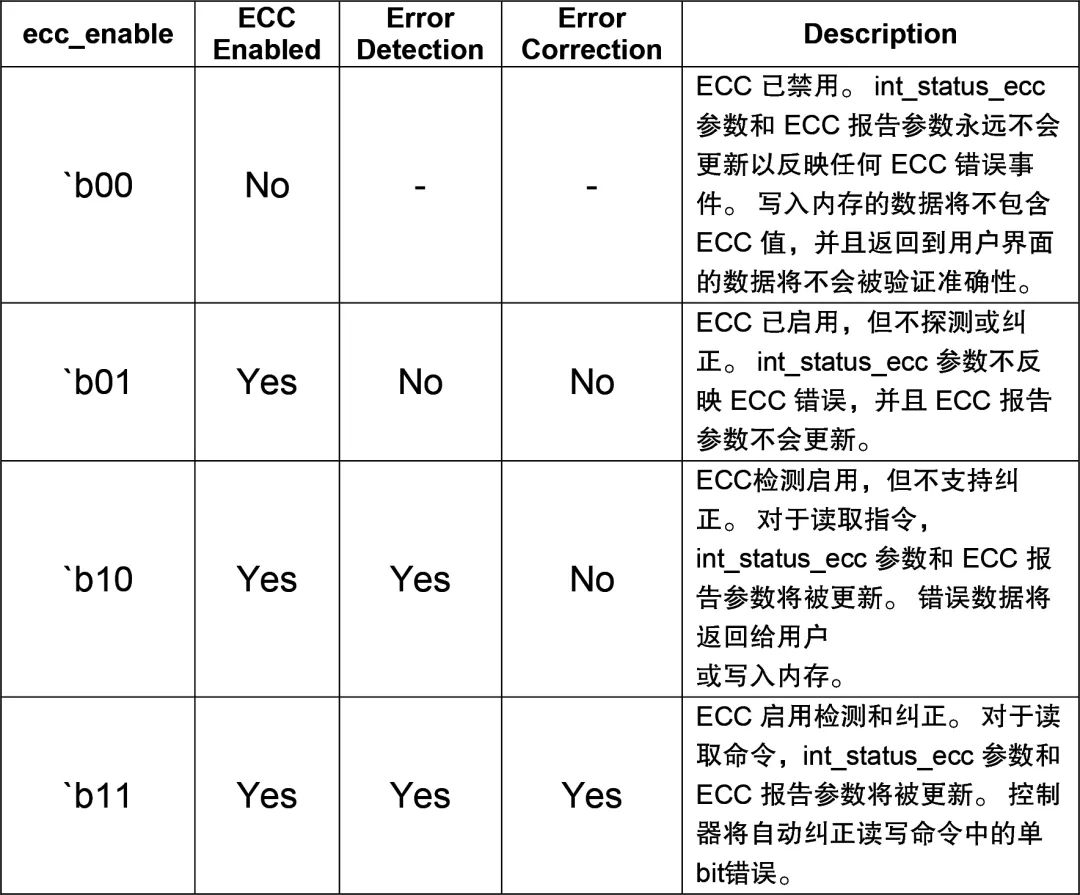

軟件通過將ecc_enable參數設置為非零值來啟用ECC。

控制器中的ECC功能由ecc_enable參數控制。該參數使能ECC,并設置上報和糾錯行為。

ecc_enable參數含義詳細說明:

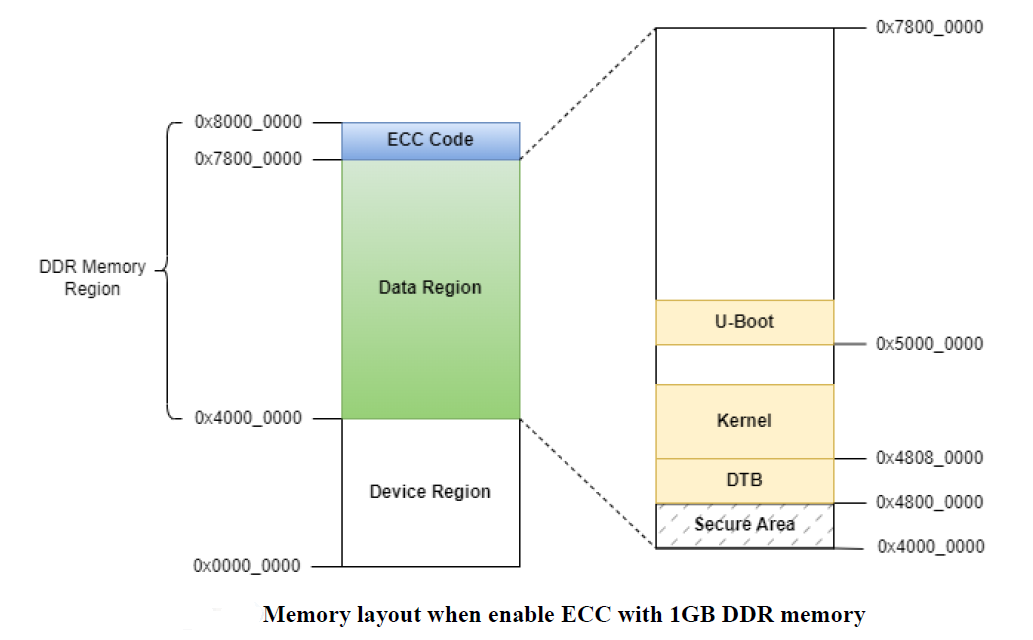

G2L內存控制器支持in-line ECC,其中內存區域的一部分(1/8)用于ECC存儲。當ECC功能啟用時,內存控制器將分配頂部1/8內存區域來存儲ECC校驗碼。并且不允許用戶訪問該區域。

例如,當DDR內存為1GB時,啟用ECC功能時內存布局如下圖所示。假設DDR內存映射到系統總線,并以地址0x4000_0000開始,以0x7FFF_FFFF結束。要使用的數據區域為0x4000_0000 – 0x77FF_FFFF。頂部1/8內存區域是0x7800_0000 – 0x7FFF_FFFF (128MB) 將用于保存ECC校驗碼。

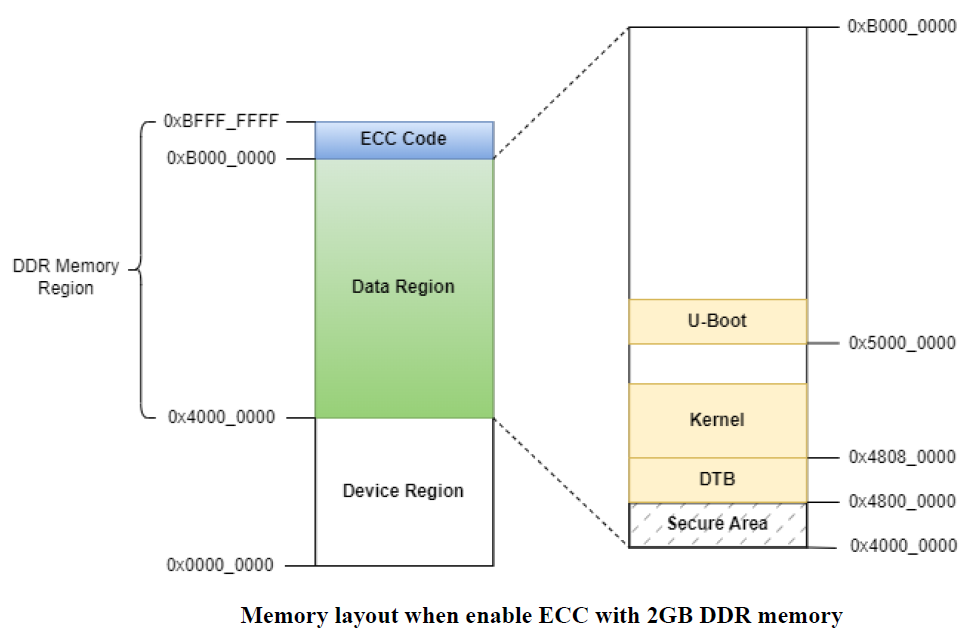

當DDR內存為2GB時,啟用ECC功能時內存布局如下圖。

假設DDR內存映射到系統總線,并以地址0x4000_0000開始,以0xBFFF_FFFF結束。

要使用的數據區域為0x4000_0000 – 0xAFFF_FFFF。頂部1/8內存區域是0xB000_0000 –

0xBFFF_FFFF(256MB) 將用于保存ECC校驗碼。

以上概要介紹ECC功能和機制,后續會介紹軟件使用配置。

審核編輯:劉清

-

DDR

+關注

關注

11文章

759瀏覽量

69381 -

人機界面

+關注

關注

5文章

565瀏覽量

45652 -

微處理器

+關注

關注

11文章

2434瀏覽量

86051 -

ECC

+關注

關注

0文章

104瀏覽量

21730 -

視頻編解碼器

+關注

關注

0文章

25瀏覽量

11930

發布評論請先 登錄

瑞薩MCU方案:瑞薩RZ/G2L Bootloader單獨編譯方法詳解

G2L系列 核心板 -RZ/G2L 處理器簡介|框架圖|功耗|原理圖及硬件設計指南

【米爾瑞薩RZ/G2L開發板-試用體驗】開箱

【米爾瑞薩RZ/G2L開發板-試用體驗】認識一下米爾瑞薩RZ/G2L開發板的核心板

瑞薩G2L系列核心板-RZ/G2L處理器簡介

具有3D圖形和視頻編解碼器的通用 MPU RZ/G2L 數據手冊

RZ/G2L微處理器DDR ECC功能和機制概要

RZ/G2L微處理器DDR ECC功能和機制概要

評論