封裝測試為半導體產業核心環節之一,指將經過測試的晶圓加工成獨立芯片的過 程,主要分為封裝與測試兩個環節。封裝是將半導體元件在基板上布局、固定及連接,并用絕緣介質封裝形成芯片的過程。封裝步驟有效保證芯片的散熱和電信 號傳輸性能;測試步驟對芯片的結構完整性及電氣功能進行確認。

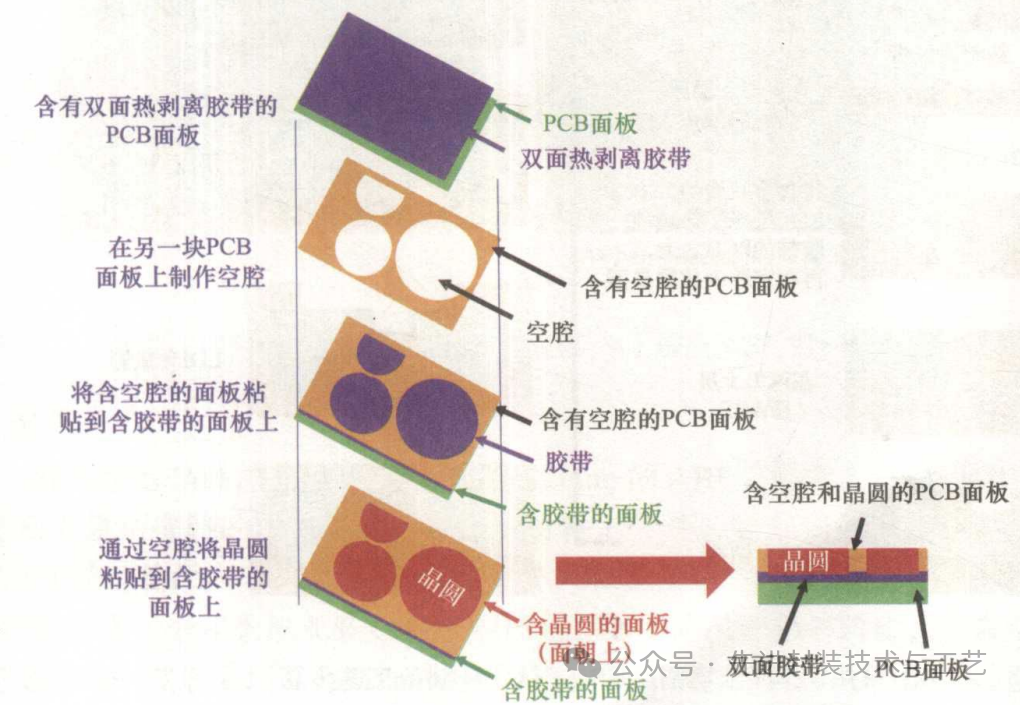

全球集成電路封裝技術共經歷了五個發展階段,不斷朝小型化、I/O 數量增加、集成化方向發展。早期三種傳統封裝方式包括通孔插轉型封裝(QFN、QFP)、表面貼裝型封裝(SOP、SOT)、現階段廣泛采用的芯片級封裝(CSP)和球柵陣列封裝 (BGA)。包括倒裝焊封裝 (Flip Chip)、三維立體封裝 (3D IC)、系統級封裝 (SiP) 在內的第四/五代封裝方式,被視為先進封裝。

封裝測試市場:與半導體產業共同發展壯大,先進封裝占比提升

作為從晶圓制造到成品芯片的關鍵環節,隨著全球半導體產業的發展,封裝測試的市場規模不斷擴大。據 Yole 統計和預估:2019 年全球封裝測試市場規模為 675 億美元,2022 年達到 815 億美元, 2026 年將上升至 961 億美元;中國大陸的封 裝測試市場由 2019 年的 2350 億元,上升至 2022 年的 2996 億元,在短暫調整之 后 2026 年有望達到3248億元的規模。

封裝測試產業鏈:與上下游密切配合

集成電路封裝測試行業整體位于半導體產業鏈的中下游,是銜接前道晶圓制造與成品芯片的關鍵環節。封裝測試的上游包括封裝測試設備,封裝材料,EDA 軟件,與晶圓生產等環節;下游客戶則主要為芯片設計企業。

前道制造晶圓廠很少直接參與傳統后道封裝環節;但是隨著先進封裝技術的不斷推廣,刻蝕、沉積、光刻、鍵合、清洗等工藝在先進封裝環節得到廣泛運用,逐漸形成了中道工藝。中道工藝的精度低于同期的前道晶圓制造工藝,但顯著高于傳統的后道封裝;由于中道制程工藝原理與前道制程工藝存在大量相通之處,臺積電、三星、海力士等晶圓制造企業開始與下游封測廠商密切合作,深度介入先進封裝流程。部分前道設備企業開始積極布局中道先進封裝設備。

封裝測試設備:存在較大國產替代空間

集成電路封裝測試流程主要使用測試設備與封裝設備。測試設備主要包括 ATE 測試機、探針臺、分選機等,負責對成品芯片的電性等指標進行檢查,并篩查出不合格的芯片。國內測試設備下游客戶主要包括封測企業,芯片IDM企業;2022年國內測試機市場規模為25.8億美元。在測試設備領域, 國內已經涌現出長川科技、華峰測控、武漢精鴻、精智達、聯動科技、廣立微等優秀企業,模擬測試機已實現較高的國產化率;但高端測試設備市場仍然主要被愛德萬、泰瑞達等美日企業掌控。

封裝設備負責從裸晶圓到成品芯片的生產過程。2022 年全球(傳統)封裝設備市場規模為 57.8 億美元,SEMI 預計 2023 年將回落至約 40 億美元,2025 年有望回 升至 59.5 億美元。相較于前道制造設備和測試設備,封裝設備品類繁多,國外出 口限制措施較少,國內重視程度較弱,國產化水平較低。2021/2022 年中國大陸封 裝用設備進口規模分別 216/153 億元,存在較大國產替代空間。傳統芯片封裝產線 中國大陸封裝設備進口金額(億元)

審核編輯:劉清

-

集成電路

+關注

關注

5452文章

12572瀏覽量

374554 -

半導體

+關注

關注

339文章

30737瀏覽量

264147 -

晶圓

+關注

關注

53文章

5410瀏覽量

132295 -

芯片設計

+關注

關注

15文章

1155瀏覽量

56679 -

QFN封裝

+關注

關注

0文章

193瀏覽量

17681

原文標題:集成電路封裝:由晶圓到成品芯片

文章出處:【微信號:DT-Semiconductor,微信公眾號:DT半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【海翔科技】玻璃晶圓 TTV 厚度對 3D 集成封裝可靠性的影響評估

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數據測量的設備

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

芯片制造的畫布:晶圓的奧秘與使命

從零到一:集成電路封裝測試實驗室建設的關鍵要素

集成電路封裝關鍵流程:由晶圓到成品芯片

集成電路封裝關鍵流程:由晶圓到成品芯片

評論