一、分頻

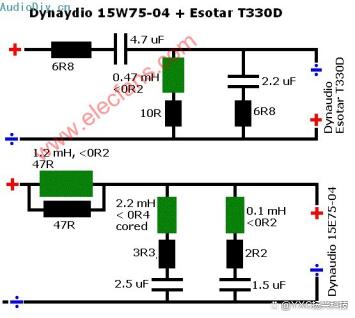

分頻的過程涉及到將一個高頻信號轉換成頻率更低的信號。例如,如果原始信號的頻率是F,經過2分頻后,新信號的頻率將是F/2。在這個過程中,原始信號每經過兩個周期,新信號才跳變一次,因此新信號的周期是原信號周期的兩倍。分頻常用于需要降低時鐘頻率的電路中,如在某些數字電路設計中生成不同頻率的時鐘信號。

在RC電路中,電阻和電容的值可以決定一個振蕩器的頻率。通過改變電阻或電容的值,可以將振蕩器的頻率分成不同的頻率。而在數字分頻器中,輸入信號被分成不同的頻率分量,然后通過數字邏輯電路進行分頻處理。

二、倍頻

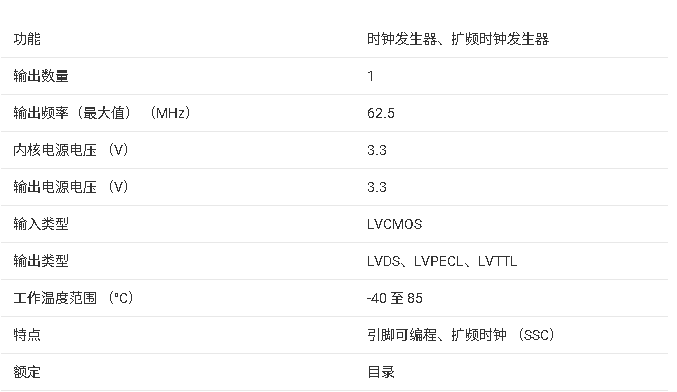

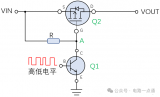

倍頻則是將信號的頻率增加至原來的N倍。這意味著,如果原始信號頻率為F,那么經過2倍頻后,新信號的頻率將是2F。在實際應用中,倍頻器可以用于無線通信系統,以產生更高頻率的信號進行傳輸。

在LC振蕩器中,電感和電容的值可以決定一個振蕩器的頻率。通過改變電感或電容的值,可以將振蕩器的頻率乘以不同的倍數。而在數字倍頻器中,輸入信號被分成不同的頻率分量,然后通過數字邏輯電路進行倍頻處理。

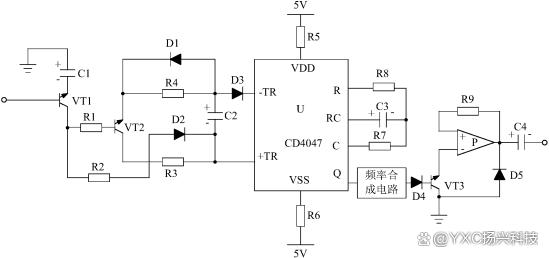

三、鎖相環PLL電路

鎖相環(PLL)電路是一種反饋控制系統,它利用外部輸入的參考信號來控制內部振蕩信號的頻率和相位。

鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。

鎖相環是一種反饋系統,其中電壓控制振蕩器和相位比較器相互連接,使得振蕩器頻率(相位)可以準確跟蹤施加的頻率或相位調制信號的頻率。鎖相環可用來從固定的低頻信號生成穩定的輸出頻率信號。

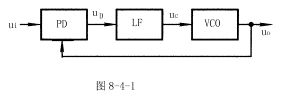

鎖相環通常由鑒相器(PD,Phase Detector)、環路濾波器(LF,Loop Filter)和壓控振蕩器(VCO,Voltage Controlled Oscillator)三部分組成,鎖相環組成的原理框圖如圖8-4-1所示。

-

鎖相環

+關注

關注

36文章

635瀏覽量

91194 -

鑒相器

+關注

關注

1文章

62瀏覽量

23887 -

環路濾波器

+關注

關注

3文章

38瀏覽量

13438 -

PLL電路

+關注

關注

0文章

94瀏覽量

7107 -

反饋控制系統

+關注

關注

0文章

12瀏覽量

2737

發布評論請先 登錄

CDC5801A:低抖動時鐘倍頻器與分頻器的卓越之選

?CDC5801A低抖動時鐘倍頻/分頻器技術文檔總結

IGBT驅動與保護電路設計及 應用電路實例

無線應用射頻微波電路設計

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

集成整數 N 分頻 PLL 和 VCO 的 350-5000 MHz 寬帶接收混頻器 skyworksinc

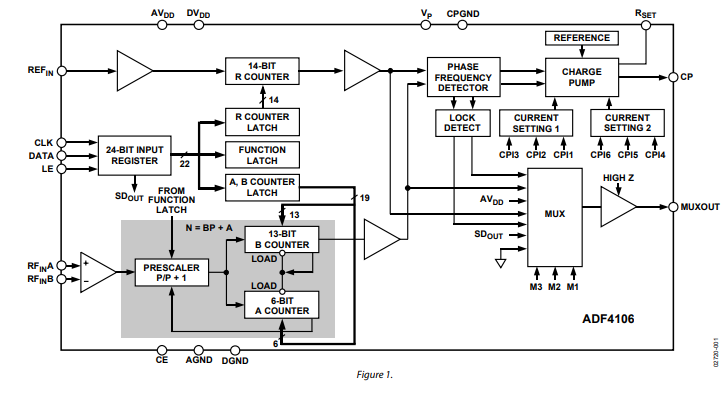

ADF4106 6GHz整數N分頻PLL技術手冊

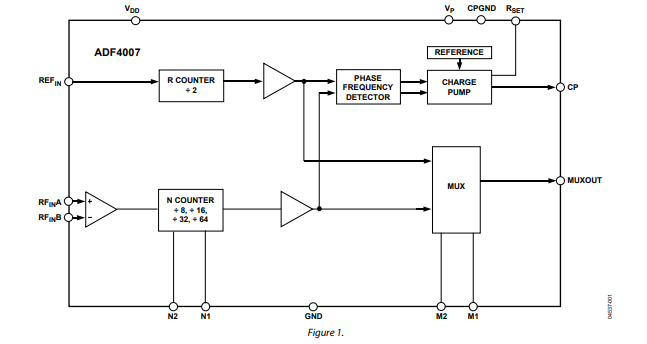

ADF4007高頻分頻器/PLL頻率合成器技術手冊

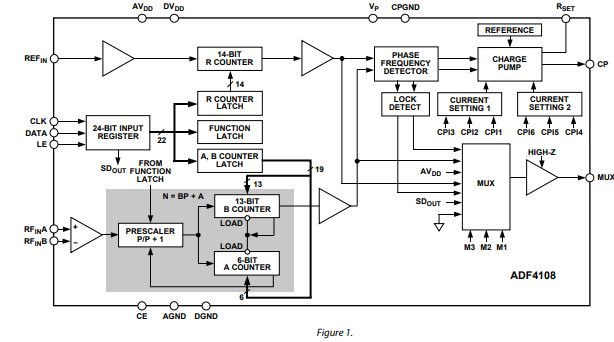

ADF4108 8GHz整數N分頻PLL技術手冊

分頻、倍頻與PLL電路在電路設計中的應用

分頻、倍頻與PLL電路在電路設計中的應用

評論