SOC芯片近幾年的發展勢頭迅猛,許多行業中俱可見其身影。SOC芯片并不是傳統意義上的芯片,它是一個由多種功能集成的一個芯片。SOC芯片自身在出廠時便帶有部分程序,是為了方便設計開發而針對某些行業設計的特定功能。如芯海的SOC芯片大多數則是基于測量精度領域而設計,它是一種集成ADC和MCU主控功能的芯片,具有高精度和穩定性的特點。測量精度SOC芯片通過集成高精度的傳感器和信號處理電路,能夠實現對各種參數的準確測量,如溫度、壓力、濕度等。它能夠提供穩定、可靠的測量結果,為工業控制系統提供準確的數據支持。

今天整理了一些關于芯海SOC芯片的操作流程和注意事項問題,希望對大家有幫助。

1、當晶片進入休眠模式時,應如何設置 I/O 狀態,使功耗最小?

答:I/O 口斷開上拉電阻,作為輸出,并輸出低電平。

2、沒有用到的 I/O 如何處理?

答:沒有用到的 I/O 口應設成輸入狀態,并啟用上拉電阻,避免因 I/O 浮接時造成芯片耗電。或將 I/O 口設置為輸出狀態。

3、產品開發過程中如何提高 EFT 特性?

答:

(1)電源輸入位置要做好濾波,通常采用大小電容組合,外部電源必須要經過電容再到達芯片電源端;

(2)采用 3V 電池作電源時, RST 復位端上拉一個 10KΩ的電阻到 VDD 端;采用 LDO 穩壓電源時, RST 復位端上拉一個 100KΩ的電阻到 VDD 端,并且需添加大小為 0.1uF的接地電容。

(3)設計外掛晶振電路時,應視晶振參數選擇合適的匹配電容和電阻,振蕩電路應盡可能靠近芯片引腳,并與地線和電源線保持足夠的距離,以避免電源高頻干擾。

(4)I/O 端具有高雜信號的負載最好以光藕等元件隔離或加吸干擾信號電路。如果是有危險的負載,應加有上拉或下拉電阻以防止芯片損壞時的誤動作。另外,某些特殊場合由于安全的需要,具有危險性的負載也可以利用軟體脈沖驅動的方式,透過電容耦合,以避免芯片復位或當機時的誤啟動造成的危險。

4、RC 振蕩頻率主要受哪些因素影響?

答:

(1)工作電壓;

(2)工作環境溫度;

(3)外部干擾源:不同的 RC 組合,會有不同的抗干擾性能。 PCB 布板也可以改善 RC 振蕩的穩定性。

5、獨立按鍵與 MCU 如何連接能有效避免 I/O 口損壞?

答:產品開發時,按鍵是很常見的功能,由于考慮到成本等因素,很多客戶都是將按鍵的兩端分別與 MCU 和 GND 相連,這種做法在大部分情況下是沒有問題的。但是,當工作環境比較差,比如: ESD、電源等干擾,此時若按鍵被按下就很可能會有瞬間大電源或高電壓甚至負壓灌入 I/O 口,造成 I/O 口損壞。 針對這種問題的防范措施是:可以將端口的上拉打開,并增加一個 0.1uF 的接地電容。

6、I/O 外接下拉電阻,沒有外接信號時芯片為何讀不到低電平?

答:如果客戶在程序中將 I/O 口的上拉電阻使能,同時又在該 I/O 口的周邊接有下拉電阻,在沒有信號輸入的情況下,相當于內置上拉電阻與外接下拉電阻串聯分壓,所以有可能會導致 I/O 口讀不到低電平。

7、切換 ADC 通道后,須丟棄多少筆 AD 數值才穩定?

答:切換 AD 通道后,須丟棄前三筆轉換的 AD 值,以確保轉換的數值正確性。

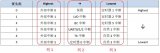

8、如何選擇 VS 輸出的電壓值?

答:芯片內部 VS 可選 2.2V、 2.5V、 2.8V、 3V 四種 LDO 電壓輸出。電壓越低,功耗也越低,電源電壓下降時影響越小,但傳感器輸出信號越小。為此在滿足信號量情況下, VS 選越低的電壓越好。

9、如何正確使用 Watchdog?

答:Watchdog 是防止外部不可控制事件(如電的干擾等)所造成的程序不正常動作或跳轉到未知的地址。使用者必須適當設計程序及運用 CLRWDT 指令使程序正常執行時, Watchdog不會溢出,并且當系統運行不正常時, Watchdog 可以溢出喚醒芯片。

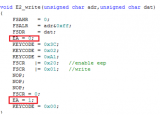

10、編寫程序時如何進行間接尋址?

答:FSR0/1 是存放間接尋址的地址, IND0/1 是存放間接尋址地址內的數據。 IRP0/1 是控制尋址的范圍,“ 0”為尋 00~FF 的內容;“ 1”為尋 100~17F 的內容。

11、調試開發板上的 AD 內碼達不到 Datasheet 上的有效位?

答:由于開發板有干擾,使仿真時內碼比實際芯片的內碼有效位低 1 位左右。

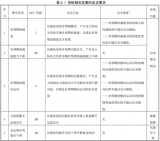

12、為何用舊電池標定省EEPROM產品時,用舊電池稱重準,換用新電池后重量不準?

答:OTP自燒錄時的VPP電壓是通過將電池電壓升壓1倍從VLCD引腳輸出到VPP。而OTP燒錄的VPP電壓要求6.25~6.75V,若采用舊電池來供電,則VPP電壓低于標準電壓,OTP燒錄的電荷就偏低,造成當電池電壓高時,會有誤讀OTP數據。

建議:

(1)采用OTP自燒錄省EEPROM時,用外部穩壓電源6.25~6.75V供給VPP或用外部穩壓電源3.3V供給DVDD和AVDD;

(2)采用3.2V~3.5V的電池供給DVDD和AVDD;

13、 LCD顯示過暗,筆畫不清晰?

答:

(1)將分壓電阻調小,調小電阻會帶來功耗的增加;

(2)將LCD的時鐘頻率以及LCD幀頻調整,一般說來幀頻越慢,顯示筆畫越清晰,但是幀頻過慢會導致LCD顯示閃爍的問題;

(3)將波形選為B波形;

14、間隙供電測量模式下,為什么每次讀回的AD值誤差大?

答:間隙供電時,關閉模擬部分只需清除NETF寄存即可,模擬部分其它寄存器不要每次上電都配置。

15、外部晶振不起振?

答:

(1)IO 設成模擬輸入;

(2)IO數字輸入輸出使能設置為數字輸入;

(3)關掉IO上拉電阻;

(4)設外部晶振是高速還是低速;

(5)開啟外部晶振,并延時20ms;

16、使用內部溫度傳感器時,如何保存能做到+/-1度誤差?

答:

(1)PGA = 1 取22位AD值;

(2)進行一點標定(用當前環境溫度進行標定);

計算公式: 當前溫度AD / (273.15 + 當前環境溫度) = 每度變化AD值

17、開發高精度帶背光的產品時,當背光關閉和點亮時,ADC的內碼會變化?

答:背光關閉和點亮時,ADC的內碼變化,需注意以下幾點:

(1)模擬部分的AVDD和AGND需在電源的輸入端才與DVDD和DGND相連;

(2)主程序中每個大循環的運行時間需一致,否則會引起內部電流波動,影響ADC;(建議:主程序中不要用Halt指令;)

18、UV擦除裸片(DIE),UV強度和時間多少?

答:UV強度需達到25mW/cm^2,光強時間為1小時。

注意:由于OTP是一次性燒寫memory,紫外擦除只是應急措施,并不能保證100%成功。

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54010瀏覽量

466003 -

soc

+關注

關注

40文章

4576瀏覽量

229135

發布評論請先 登錄

芯馳科技亮相BlackBerry QNX 2025中國年度開發者大會

芯海單片機 燒錄器提示“燒錄文件錯誤”怎么解決

芯片制造中的鍵合技術詳解

瑞芯微芯片:國產SoC的技術突破與應用前景

芯海科技CPW6430:全能型多快充協議Buck-Boost SoC

鼎盛合|芯海SOC芯片開發中的技術問題

鼎盛合|芯海SOC芯片開發中的技術問題

評論