雙路LVDS信號和單路的時鐘頻率有什么關系?是一個時鐘內傳輸兩個像素的數據嗎?

雙路LVDS信號是一種在高速數據傳輸上應用廣泛的接口,它利用微小的電壓擺動來傳輸數據。在雙路LVDS信號中,數據被分成兩個獨立的信號流傳輸。這兩個信號流被稱為“正”和“反”信號,每個信號流包含一個有效數據線和一個共享地線。雙路LVDS接口在圖形和視頻傳輸中得到廣泛應用,通常用于解決一些高速傳輸需要,比如在某些具有高像素密度的液晶顯示器(LCD)中。

雙路LVDS信號的時鐘頻率由兩個因素決定:像素時鐘頻率和像素位寬。像素時鐘頻率是指在數字信號處理系統中像素時序的頻率,通常以MHz為單位。而像素位寬則指每個像素的位數,例如24位像素包含RGB(紅色,綠色和藍色)信號,一個像素根據不同的分辨率要求可能需要不同的像素位寬。

為了保證數據的傳輸速率和準確性,雙路LVDS信號的時鐘頻率必須與像素時鐘頻率同步。在傳輸數據之前,像素時鐘通過相位鎖定環(PLL)被同步到小數位。同時,像素時鐘以雙倍節拍的頻率被輸入到LVDS接收器以產生正和反信號,這樣即可傳輸雙倍像素位寬的數據。

因此,雙路LVDS的時鐘頻率并不是一個時鐘內傳輸兩個像素數據,而是將兩個像素數據傳輸到雙倍頻率的LVDS信號中,從而通過同步的像素時鐘實現高速數據傳輸。這種方式可以提高傳輸速度和準確性,以適應高分辨率和高清晰度視頻傳輸的需求。

當然,對于傳輸性質要求不高的情況,也可以使用單路LVDS信號,這只需要一個信號流和單獨的時鐘信號就可以完成數據傳輸。但在需要高速傳輸和高性能的應用中,如現在的高端液晶顯示器、高分辨率攝像頭等設備,使用雙路LVDS可以實現更高的數據傳輸速率和數據準確性,因此成為了這些應用的主流接口。

-

RGB

+關注

關注

4文章

835瀏覽量

62191 -

LVDS信號

+關注

關注

0文章

19瀏覽量

8219 -

PLL電路

+關注

關注

0文章

94瀏覽量

7127

發布評論請先 登錄

深入解析CDCLVD2102:雙路1:2低附加抖動LVDS緩沖器

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析

CDCLVD2104:高性能雙路1:4低附加抖動LVDS緩沖器解析

LT1212:單電源雙路和四路精密運算放大器的卓越之選

雙路復用LVDS中繼器SN65LVDS22和SN65LVDM22:高速信號傳輸的理想選擇

深度剖析DS90LV027A:高性能LVDS雙路高速差分驅動器

深入解析 8P34S2106A:高性能雙路 1:6 LVDS 輸出扇出緩沖器

汽車類LVDS雙路差動線路接收器DS90LV028A-Q1的設計與應用

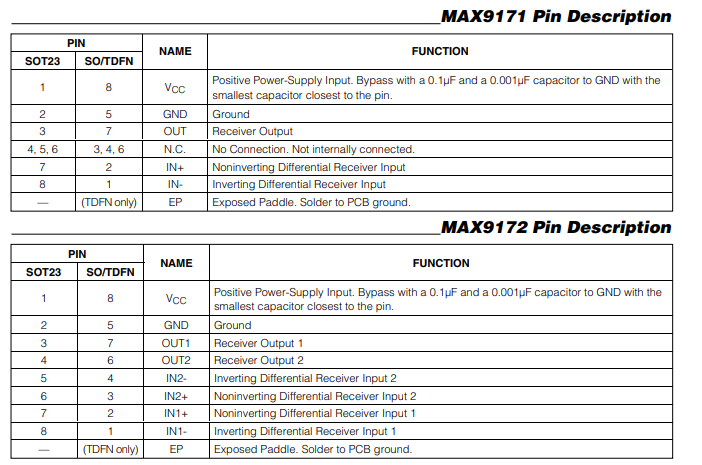

MAX9171/MAX9172單/雙路LVDS線接收器,帶有通道失效保護技術手冊

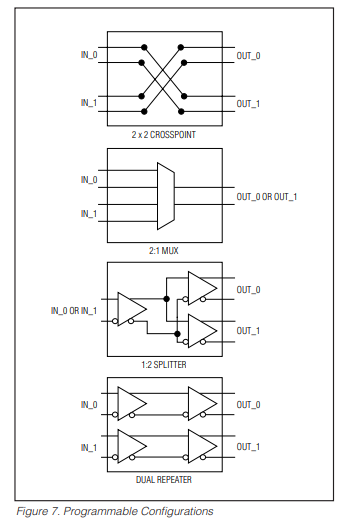

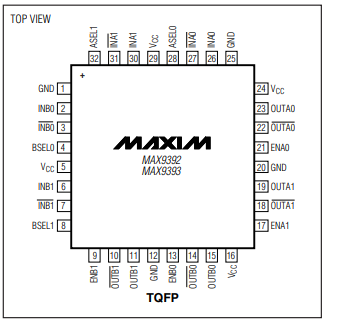

MAX9393任意邏輯至LVDS、雙路、2 x 2交叉點開關技術手冊

MAX9392任意邏輯至LVDS、雙路、2 x 2交叉點開關技術手冊

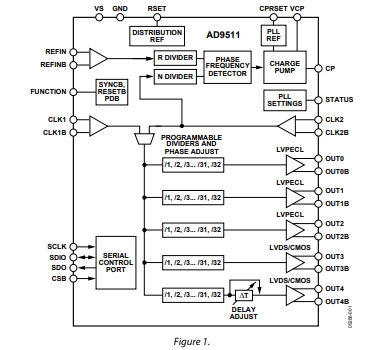

AD9511 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,5路輸出技術手冊

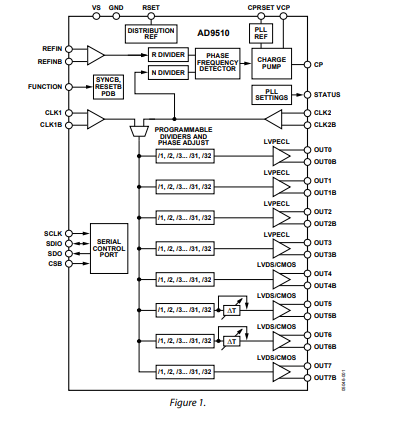

AD9510 1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出技術手冊

雙路LVDS信號和單路的時鐘頻率有什么關系?

雙路LVDS信號和單路的時鐘頻率有什么關系?

評論