pll倍頻最大倍數

PLL倍頻是一種常見的電路設計技術,通常用于將信號的頻率提高到需要的倍數。PLL倍頻的實現原理比較復雜,通常需要使用精密的電路元件、時鐘信號以及數字信號處理器。本文將詳細介紹PLL倍頻的實現方法、工作原理以及最大倍數的計算方法,幫助讀者更好地了解和應用PLL倍頻電路。

一、PLL倍頻的實現方法

PLL倍頻主要通過三個電路模塊來實現:相位比較器、鎖相環和除頻器。其中,相位比較器主要用于比較輸入信號和反饋信號的相位差,從而調整鎖相環的頻率;鎖相環則主要用于根據相位比較器的輸出信號來調整時鐘信號的頻率,保證輸入信號和輸出信號的同步;除頻器則用于將鎖相環輸出信號的頻率按照預定比例進行除頻,最終得到需要的輸出信號。

二、PLL倍頻的工作原理

PLL倍頻的工作原理基于鎖相環原理,具體步驟如下:

1.將所需倍頻的輸入信號和時鐘信號分別輸入給相位比較器和鎖相環;

2.相位比較器將輸入信號和時鐘信號進行相位比較,得出兩者之間的相位差;

3.鎖相環將相位比較器的輸出信號作為反饋信號輸入,與輸入信號合成新的時鐘信號;

4.除頻器將鎖相環的輸出信號按照預定比例進行除頻,得到需要的輸出信號。

在這個過程中,相位比較器、鎖相環和除頻器三者相互配合,保證了輸入信號到輸出信號的同步性和倍頻率的準確性。同時,在PLL倍頻中,除頻器的除數越大,輸出信號的頻率就越低,但是也會增加系統的時延。

三、PLL倍頻的最大倍數

PLL倍頻的最大倍數是指在給定的輸入信號頻率下,可以實現的輸出信號最高頻率。計算PLL倍頻的最大倍數需要考慮多方面的因素,包括鎖相環的帶寬、穩定性、噪聲等。

常用的計算公式如下:

最大倍頻率=N×Fclk/(2×M)

其中,N為除頻器的除數,M為鎖相環的倍頻器,Fclk為時鐘頻率。

從公式上可以看出,除頻器的除數N越大,最大倍頻率就越低,鎖相環的倍頻器M越大,最大倍頻率就越高。同時,時鐘頻率Fclk的大小也對最大倍頻率有一定的影響。

四、總結

PLL倍頻是一種重要的電路設計技術,其主要工作原理是通過相位比較器、鎖相環和除頻器這三部分電路模塊相互配合,實現輸入信號到輸出信號的同步和倍頻。在實際應用中,計算PLL倍頻的最大倍數需要考慮多種因素,包括帶寬、穩定性、噪聲等。希望本文可以為讀者提供一些關于PLL倍頻的基礎知識和理解,幫助讀者更好地應用該技術。

-

鎖相環

+關注

關注

36文章

635瀏覽量

91118 -

比較器

+關注

關注

14文章

1928瀏覽量

111918 -

pll

+關注

關注

6文章

982瀏覽量

138180 -

倍頻電路

+關注

關注

4文章

12瀏覽量

32936 -

除頻器

+關注

關注

0文章

2瀏覽量

5030

發布評論請先 登錄

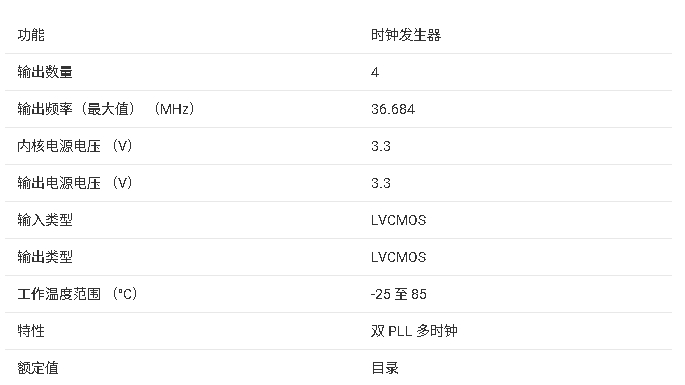

Texas Instruments PLL1705/PLL1706:3.3-V 雙 PLL 多時鐘發生器的卓越之選

Texas Instruments PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

探究PLL1705與PLL1706:3.3V雙PLL多時鐘發生器的卓越性能

德州儀器PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

德州儀器PLL1707和PLL1708:低抖動多時鐘發生器的卓越之選

倍頻系統中的晶振選擇建議

修改 PLL 參數的流程

PLL1708雙PLL多時鐘發生器技術文檔總結

?PLL1707/PLL1708 雙PLL多時鐘發生器技術文檔總結

易靈思 FPGA TJ375的PLL的動態配置

智多晶PLL使用注意事項

PLL用法

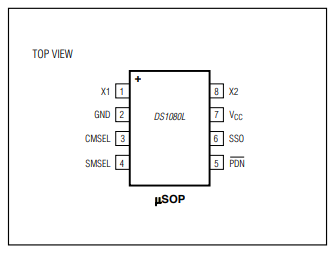

DS1080L擴頻晶振倍頻器技術手冊

pll倍頻最大倍數

pll倍頻最大倍數

評論