探索背面供電,解決芯片線路設計兩難

隨著半導體技術的飛速發展,先進制程的角逐已經圍繞著5nm以下的工藝展開。隨著制程節點由5nm向3nm、2nm發展和演進,芯片制造的難度逐步逼近摩爾定律的物理極限,從制程進步中獲得芯片性能提升的難度和成本越來越高。

在越來越小的晶體管中,堆棧層數越來越多,信號線和電源線在多層布線中混合在一起用于連接晶體管與金屬層。在越來越有限的芯片面積內,電源線進一步縮小會帶來IR Drop問題,晶體管得不到充足的電力供應。

但是如果選擇保證電源線厚度避免電壓降,又會占用更多片內信號線的布線空間。在以前的制程節點中,這一問題并沒有充分暴露出來,而線路層的信號線和電源線設計在3nm、2nm以及更小制程節點的演進下陷入兩難的境地。

傳統的供電線路是在正面進行布線,這種供電技術會影響到金屬層的資源的分配,在電路設計越來越復雜的情況下如何處理信號網絡跟供電網絡之間的資源排擠問題,是芯片進一步微縮的關鍵,也是芯片制造面臨的主要挑戰之一。

為了解決這一兩難的困境,業界不斷探索著新的芯片供電網絡方案。背面供電網絡BSPDN技術正是解決芯片線路設計兩難境地的革命性技術。

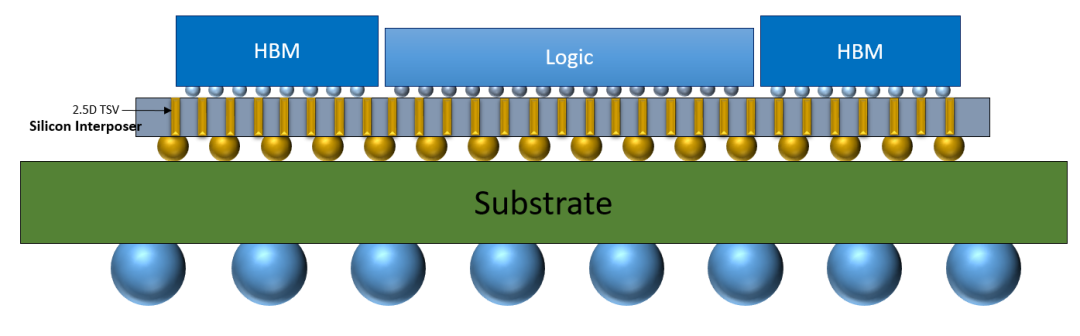

背面供電技術BSPDN該技術最早于2019年IMEC研討會上被提出,是在晶體管三維結構上進行創新,挖掘晶圓背面空間的潛力,將原先和晶體管一同排布的供電網絡直接轉移到晶體管的背面重新排布。

供電問題在晶圓背面解決,IR Drop效應明顯下降,芯片性能得以改善,芯片的正面只需要專注于信號互連。

背面供電技術能帶來的優勢遠遠不止解決供電問題IR Drop這么單一,物理設計上的改善,能夠大幅提高芯片利用率,減少時序擁堵等問題;背面供電同時縮減了金屬線長,這意味著時鐘功耗能夠降低、緩沖器數量減少和主動功耗降低。

綜合這些所有的優勢點,采用背面供電技術和采用傳統供電技術相比,芯片的性能、能效等系統級指標均能夠大幅提升,功耗、面積得以進一步降低。

巨頭競爭,搶攻背面供電技術高地

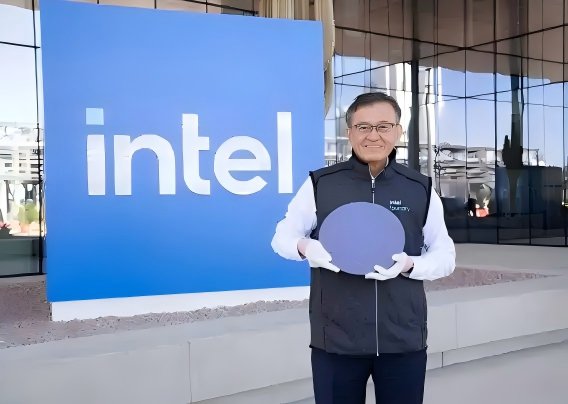

從目前布局開發背面供電技術幾家巨頭的進度來看,英特爾是在這條賽道上最激進也有望最先落地背面供電技術應用的一方。根據英特爾目前已經公布的信息,其獨家的背面供電技術PowerVia將用于18A、20A工藝節點,并且英特爾已經率先在產品級測試芯片上實現了背面供電。

英特爾官方宣布該技術將在2024年20A制程節點上正式落地應用,這比三星和臺積電暫定的背面供電技術推出時間都要早。

根據英特爾的測試,PowerVia將平臺電壓降低了30%,并帶來了6%的頻率增益。同時測試中芯片大部分區域的標準單元利用率都超過了90%,同時晶體管體積縮小,單元密度大幅增加。為此,英特爾還開發了新的散熱技術保證散熱。

當前背面供電技術還面臨著良率和可靠性等方面的挑戰,不過從英特爾目前已經公布的測試來看,PowerVia的良率和可靠性已經較為成熟。所以英特爾在明年正式使用PowerVia背面供電技術配合20A制程節點上線把握性還是很大的。

在先進制程的競爭中,三星同樣不甘示弱,其背面供電技術已經在緊鑼密鼓地開發中。根據相關消息,三星目前正在針對背面供電技術做市場需求調查,在確保需求充分后,背面供電技術可能會應用到計劃于2025年量產的2nm中以解決使用2nm工藝造成的布線擁塞問題,計劃于2027年量產的1.4nm工藝使用背面供電技術是可以確定的。

根據三星披露的其研發的背面供電技術測試數據,兩個基于ARM架構的處理器,采用背面供電技術后,相比采用傳統供電方式,芯片面積分別縮小了10.6%和19%。這意味著內部的集成度和性能都能有不小的提升。同時,背面技術的應用使布線長度減少了接近10%,這也能帶來額外的性能優勢。

作為另一家巨頭,臺積電也在背部供電上進行著布局,但在技術推進上稍顯保守。根據臺積電此前公布的規劃,臺積電會在2026年推出一個N2P制程節點,同時在這個工藝上,背面供電技術將被引入進來。

根據臺積電透露的相關技術數據,N2P制程技術將通過背后供電技術能夠有效減少IR Drop和改善信號,芯片性能提高了10%—12%,并將邏輯面積減少10%—15%。雖然推出時間有些落后,但在背面供電技術的前期準備上,臺積電已經做了不少相關的技術儲備。

三家巨頭中目前在背面供電技術最領先的無疑是英特爾,不論是從披露的相關技術進度、成熟度,還是從量產落地時間來看,英特爾目前都還是很有優勢的,相比其他廠商有著兩年左右的領先。尤其是在良率和可靠性上,英特爾目前是最具把握性的。

先進制程的角逐,將在2025年之后,各家2nm以及更先進節點芯片量產后進入白熱化。而背面供電技術的成熟度無疑會影響各個巨頭在先進制程角逐中的話語權。

小結

雖然它的實現涉及調試、散熱等諸多難度很高的挑戰,但背面供電技術能夠帶來的優勢同樣非常明顯,使用背面供電技術的芯片在性能和能效上獲得極大的提升,繼續逼近著摩爾定律的極限。

用更少的能量實現多的擴展性能,該技術成熟后能給半導體工藝帶來的改變,或許不止這些現在已經被發掘出來的優勢。背面供電技術也被視為繼續開發更精細工藝節點技術的基本技術,成為現在芯片晶圓廠正在全力競爭又一個技術高地。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

英特爾

+關注

關注

61文章

10301瀏覽量

180471 -

臺積電

+關注

關注

44文章

5803瀏覽量

176347

發布評論請先 登錄

相關推薦

熱點推薦

被指存散熱硬傷,英特爾代工iPhone芯片幾無可能?

的低端M系列芯片、2028年推出的iPhone標準版芯片,有望率先采用英特爾18A-P先進工藝。 ? 然而,這一看似“臺積

0.2nm工藝節點的背后需要“背面供電”支撐

實現0.2nm工藝節點。 ? 而隨著芯片工藝節點的推進,芯片供電面臨越來越多問題,所以近年英特爾、臺積電、

臺積電Q3凈利潤4523億元新臺幣 英偉達或取代蘋果成臺積電最大客戶

39.1%,凈利潤創下紀錄新高,臺積電在上年同期凈利潤為3252.58億新臺幣。 每股盈余為新臺幣17.44元,同比增加39.0%。 目前臺積電

今日看點丨英特爾 Panther Lake 高規格型號被曝 TDP 45W;消息稱追覓汽車 7 項專利“全球首創性存疑”

三星2nm晶圓代工 降價 以競爭臺積電 近日,三星電子宣布將其2nm(SF2)

發表于 09-28 10:59

?1662次閱讀

今日看點丨三星美國廠2nm產線運作;《人工智能生成合成內容標識辦法》正式生效

(2330)長期規劃美國新廠后續將導入2nm與更先進制程,三星加入戰局加上英特爾獲得奧援,2nm以下制程競爭在美國更加白熱化。 ? 韓國媒體

發表于 09-02 11:26

?1759次閱讀

英特爾連通愛爾蘭Fab34與Fab10晶圓廠,加速先進制程芯片生產進程

在全球半導體產業競爭日益白熱化的當下,芯片制造巨頭英特爾的一舉一動都備受行業內外關注。近期,英特爾一項關于其愛爾蘭晶圓廠的布局調整計劃,正悄

力旺NeoFuse于臺積電N3P制程完成可靠度驗證

力旺電子宣布,其一次性可編程內存(One-Time Programmable, OTP)NeoFuse已于臺積電N3P制程完成可靠度驗證。N

臺積電先進制程漲價,最高或達30%!

%,最高可能提高30%。 ? 今年1月初臺積電也傳出過漲價消息,將針對3nm、5nm等先進制程技術進行價格調整,漲幅預計在3%到8%之間,特

發表于 05-22 01:09

?1258次閱讀

詳細解讀三星的先進封裝技術

集成電路產業通常被分為芯片設計、芯片制造、封裝測試三大領域。其中,芯片制造是集成電路產業門檻最高的行業,目前在高端芯片的制造上也只剩下臺積電(TSMC)、三星(SAMSUNG)和

英特爾持續推進核心制程和先進封裝技術創新,分享最新進展

,英特爾代工已取得重要里程碑。例如,Intel 18A制程節點已進入風險試產階段,并計劃于今年內實現正式量產。這一節點采用了PowerVia背面供電

背面供電成先進制程競爭又一技術高地,英特爾先發制人,臺積電、三星加碼跟進

背面供電成先進制程競爭又一技術高地,英特爾先發制人,臺積電、三星加碼跟進

評論