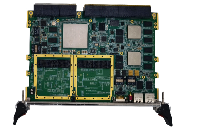

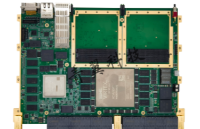

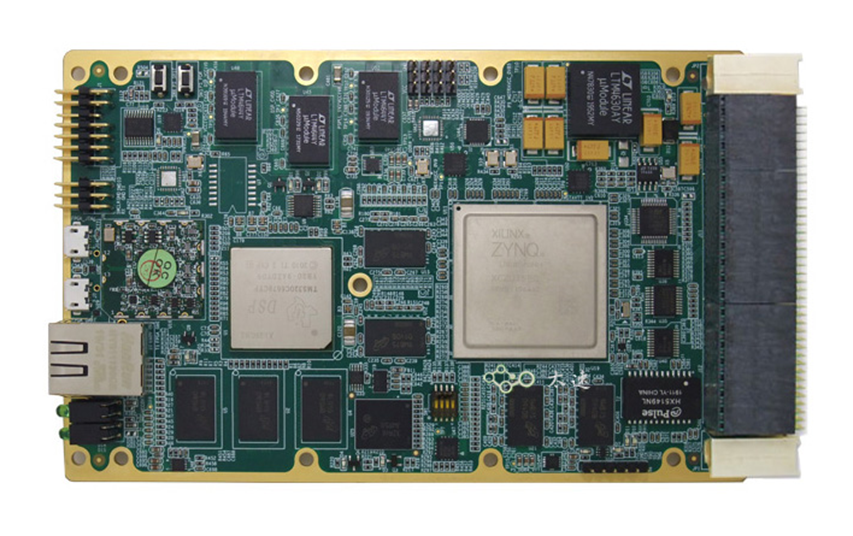

基于6UVPX C6678+XCVU9P的信號處理板卡

一、板卡概述

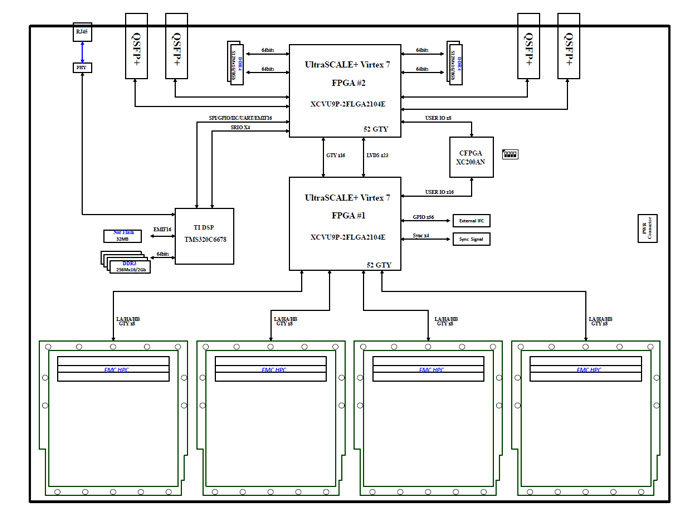

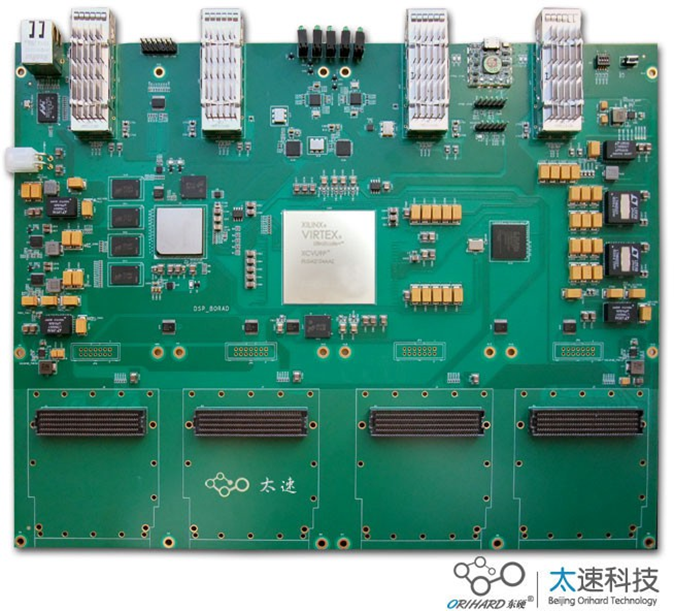

板卡基于6U VPX標準結構,北京太速科技,包含一個C6678 DSP芯片,一個XCVU9P 高性能FPGA,雙路HPC FMC。

二、處理板技術指標

? DSP處理器采用TI 8核處理器TMS320C6678;

? DSP 外掛一組64bit DDR3顆粒,總容量2GB,數據速率 1333Mb/s;

? DSP 采用EMIF16 NorFlash加載模式,NorFlash容量 32MB;

? DSP 外掛一路千兆以太網1000BASE-T;

? FPGA處理器采用Xilinx VirtexUltralSCALE+ 系列芯片 XCVU9P;

? FPGA外掛2組DDR4 ,每組2GB,64bit 容量

? FPGA 外掛2組FMC HPC 連接器;

? FPGA 引出1路QSPF+,每路數據速率40Gb/s;

? FPGA與DSP之間通過RapidIO互聯 。

? VPX 連接器上外接FPGA的24個GTY,LVDS信號,DSP的 1路以太網

三、軟件系統

? 提供FPGA的接口測試程序,包括 DDR4、光纖、RapidIO、FMC等接口

? 提供DSP接口測試程序,包括DDR3、Flash、RapidIO、網絡、uart接口。

四、物理特性:

? 尺寸:6U CPCI板卡,大小為160X233.35mm。

? 工作溫度:0℃~ +55℃ ,支持工業級 -40℃~ +85℃

? 工作濕度:10%~80%

五、供電要求:

? 雙直流電源供電。整板功耗 50W。

? 電壓:+12V 10A。

? 紋波:≤10%

六、應用領域

軟件無線電系統,基帶信號處理,無線仿真平臺,高速圖像采集、處理等。

審核編輯:湯梓紅

-

dsp

+關注

關注

561文章

8247瀏覽量

366750 -

FPGA

+關注

關注

1660文章

22415瀏覽量

636514 -

原理圖

+關注

關注

1353文章

6427瀏覽量

246339

發布評論請先 登錄

6UCPCI板卡設計方案:8-基于雙TMS320C6678 + XC7K420T的6U CPCI Express高速數據處理平臺

【VPX610】基于6U VPX總線架構的高性能實時信號處理平臺

3U VPX板卡設計原理圖:821-基于RFSOC的8路5G ADC和8路9G的DAC 3U VPX卡

【PCIE725G】青翼凌云科技基于 PCIe x16 總線架構的 JFM9VU9P FPGA 高性能數據預處理平臺(100%國產化)

【VPX650 】青翼凌云科技基于 VPX 系統架構的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

國產化板卡設計原理圖:2274-基于FMC接口的JFM7VX690T36的3U VPX信號處理板

VPX處理板設計原理圖:9-基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡 C6678板卡, XC7VX690T板卡, VPX處理板

中科億海微SoM模組——基于EQ6HL9S的單軸光纖陀螺板卡

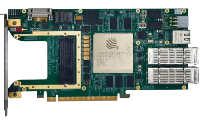

設計原理圖:U200E 基于VU9P的4路QSFP28光纖PCIeX16收發卡

527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

XCVU9P板卡設計原理圖:613-基于6UVPX C6678+XCVU9P的信號處理板卡

XCVU9P板卡設計原理圖:613-基于6UVPX C6678+XCVU9P的信號處理板卡

評論