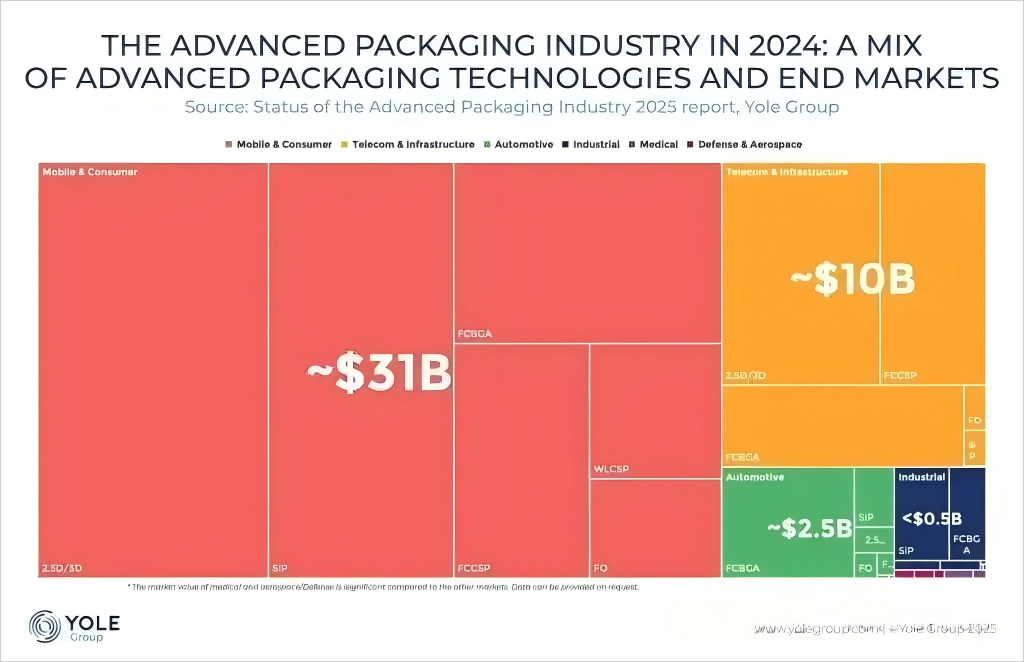

在算力撬動一切的今天,先進(jìn)封裝與Chiplet設(shè)計(jì)幾乎已成為高性能芯片的必然選擇。在先進(jìn)封裝技術(shù)與Chiplet架構(gòu)的雙力作用下,芯片這艘一度受困于摩爾定律的巨輪再次向前航行,先進(jìn)封裝功勛卓著。

2023年5月11日,第95屆CEIA中國電子智能制造高峰論壇在蘇州成功舉辦。國內(nèi)外知名品牌,業(yè)內(nèi)500余位知名專家、學(xué)者齊聚一堂,共同探討高可靠性測試技術(shù)方案,共商未來發(fā)展機(jī)遇。奇異摩爾先進(jìn)封裝專家,徐健先生受邀發(fā)表《算力時(shí)代的先進(jìn)封裝技術(shù)》的主題演講,探討大算力時(shí)代,先進(jìn)封裝與Chiplet技術(shù)的發(fā)展與應(yīng)用。

封裝:從幕后英雄,到前臺主角

“封裝是半導(dǎo)體制造的重要環(huán)節(jié),起到保護(hù)、支撐、散熱,以及連接外部電路的作用……”。封裝的這一定義,在今天看來,已不足以概括先進(jìn)封裝的價(jià)值。??????

隨著先進(jìn)制程帶來的成本優(yōu)勢和先發(fā)優(yōu)勢減弱,異質(zhì)異構(gòu)集成已成為行業(yè)公認(rèn)提升系統(tǒng)性能、降低成本的關(guān)鍵技術(shù)之一,其實(shí)現(xiàn)極大地依賴于先進(jìn)封裝技術(shù)。

在異質(zhì)異構(gòu)的世界里,chiplet是“生產(chǎn)關(guān)系”,是決定如何拆分及組合芯粒的方式與規(guī)則;先進(jìn)封裝技術(shù)是“生產(chǎn)力”,通過堆疊、拼接等方法實(shí)現(xiàn)不同芯粒的互連。先進(jìn)封裝技術(shù)已成為實(shí)現(xiàn)異質(zhì)異構(gòu)的重要前提。

隨著Fab廠商紛紛試水封裝賽道,通過Fab工藝加持封裝,先進(jìn)封裝工藝的革新也層出不窮。從傳統(tǒng)2D封裝發(fā)展至2.xD、2.5D和3D封裝,先進(jìn)封裝技術(shù)維度的革新,為芯片的集成提供了全新的可能性。

與傳統(tǒng)封裝相比,先進(jìn)封裝能夠?qū)崿F(xiàn)更小的線寬、線距,從而提供更好的電氣性能和速度;通過更好的互連設(shè)計(jì)和更高的集成度,減少PCB與芯片之間的巨大代差的影響,并承載更多的IO以而實(shí)現(xiàn)單位空間內(nèi)更高密度的系統(tǒng)集成,從而滿足產(chǎn)品在大算力和小型化方面的需求。

徐健先生表示,先進(jìn)封裝與當(dāng)下火遍全球的Chiplet概念密不可分。Chiplet設(shè)計(jì)基于先進(jìn)封裝技術(shù),涵蓋了從2.xD、2.5D到3D封裝的多種范疇。Chiplet將不同的芯粒模塊化,再通過先進(jìn)封裝技術(shù),進(jìn)行芯粒之間的互連,從而實(shí)現(xiàn)更高規(guī)模的集成。

其中,2.5D封裝通過無源Silicon Interposer、TSV通孔進(jìn)行進(jìn)行同層線路、不同芯片間的互連,可以有效實(shí)現(xiàn)芯片性能的提升。

3D封裝形式被認(rèn)為是Chiplet設(shè)計(jì)與先進(jìn)封裝的下一階段,其與2.xD和2.5D的顯著不同在于中介層的性質(zhì)。從封裝層面來說,Base die較2.5D的無源中介層更進(jìn)一步,升級為一顆獨(dú)立可用的完整芯片,從而讓芯片的集成度得到了更大程度的提高。

Base die中往往會集成cache、電源管理器等輔助功能模塊,通過上下層芯片的die2die進(jìn)行芯片間的立體通信。目前,全球各大頭部企業(yè)都在布局這一賽道。在可預(yù)見的時(shí)間里,2.5D-3D封裝與Chiplet的組合,將成為大算力芯片提升性能、降低成本最有效方式。這一趨勢也引發(fā)了先進(jìn)封裝結(jié)構(gòu)中新型互聯(lián)單元:Base die的需求。

Basedie作為3D Chiplet的必備模塊,已成為AMD和Intel為首的頭部大廠的重要研發(fā)課題之一。國內(nèi)這一領(lǐng)域尚在起步階段,也有少量具有前瞻視角的企業(yè)提前布局這一賽道。其中,奇異摩爾作為國內(nèi)首批專注于2.5D和3D Chiplet研發(fā)的公司,基于Chiplet架構(gòu),為客戶提供核心通用互聯(lián)芯粒及系統(tǒng)級解決方案,旗下產(chǎn)品線分為兩大部分,其一是2.5D、3D芯粒系列,其二是Die-to-Die IP系列。奇異摩爾基于UCIe標(biāo)準(zhǔn),提供覆蓋各種不同類型、綜合能力強(qiáng)、具高帶寬、低延時(shí)、低功耗的Die2Die IP,支持2.x/2.5/3D 等多種封裝形態(tài)。

奇異摩爾為客戶提供基于IO Die和Base Die的完整解決方案,基于核心互聯(lián)芯粒,客戶只需設(shè)計(jì)少量功能單元,即可搭建產(chǎn)品系列平臺,能極大地降低研發(fā)及量產(chǎn)的成本。奇異摩爾的解決方案覆蓋數(shù)據(jù)中心、自動駕駛、邊緣AI、5G、6G移動通信等需要大算力芯片的領(lǐng)域。客戶可以最高提升芯片的系統(tǒng)性能至1.5倍,并實(shí)現(xiàn)研發(fā)成本(80%)和量產(chǎn)時(shí)間(60%)的下降。

如何進(jìn)行Chiplet封裝設(shè)計(jì)

徐建表示,從封裝設(shè)計(jì)方式上來講,Chiplet與傳統(tǒng)封裝有所不同。由于Chiplet封裝中涉及多個(gè)芯粒的集成,不同芯粒可能具有不同的熱、電、結(jié)構(gòu)特性。在封裝設(shè)計(jì)過程中需要更加細(xì)致地考慮熱管理、流體流動、電性能和結(jié)構(gòu)布局等因素,以確保整體系統(tǒng)的穩(wěn)定性和可靠性。

此外,Chiplet封裝需要在芯片后端增加一些額外的流程,如PV(Physical Verification,物理驗(yàn)證)、時(shí)序分析、電性能和熱力分析等。這些流程確保了芯片封裝的可行性和可靠性,并幫助優(yōu)化設(shè)計(jì)和解決潛在的問題。這些差異也增加了chiplet封裝設(shè)計(jì)的復(fù)雜性。

Chiplet封裝設(shè)計(jì)需要考慮各個(gè)芯粒的協(xié)同工作,并進(jìn)行系統(tǒng)級優(yōu)化,以實(shí)現(xiàn)整體系統(tǒng)的性能和功耗平衡。這涉及到芯片之間的通信帶寬、延遲、功耗消耗等方面的綜合考慮,以滿足應(yīng)用需求并提供最佳的性能。

奇異摩爾在Chiplet生產(chǎn)和測試方面有著豐富的實(shí)踐經(jīng)驗(yàn),同時(shí)擁有多樣化的產(chǎn)業(yè)資源,可提供世界領(lǐng)先水平的先進(jìn)封裝設(shè)計(jì)、小規(guī)模打樣測試和其他服務(wù),以盡可能低的成本助力客戶解決Chiplet領(lǐng)域中最棘手的挑戰(zhàn)。

同時(shí),奇異摩爾也與主流FAB及OSAT通力協(xié)作,提供Chiplet量產(chǎn)管理服務(wù);客戶只需自研核心芯片,無需管理其他芯粒及復(fù)雜封測流程,即可輕松實(shí)現(xiàn)Chiplet量產(chǎn),并可以通過共享奇異摩爾平臺供應(yīng)鏈體系,有效降低量產(chǎn)成本。

-

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

599瀏覽量

69302 -

智能制造

+關(guān)注

關(guān)注

48文章

6235瀏覽量

79918 -

算力

+關(guān)注

關(guān)注

2文章

1528瀏覽量

16740 -

奇異摩爾

+關(guān)注

關(guān)注

0文章

79瀏覽量

4037 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

533瀏覽量

1026 -

芯粒

+關(guān)注

關(guān)注

1文章

85瀏覽量

424

原文標(biāo)題:算力時(shí)代,進(jìn)擊的先進(jìn)封裝

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

AI時(shí)代算力瓶頸如何破?先進(jìn)封裝成半導(dǎo)體行業(yè)競爭新高地

“四算合一”算力平臺,芯片國產(chǎn)化率超九成,兼容8種國產(chǎn)AI芯片

2025年曙光存儲以先進(jìn)存力構(gòu)建開放的算力底座并加速AI進(jìn)化

從云端集中到邊緣分布:邊緣智算如何重塑算力網(wǎng)絡(luò)布局

智能算力為何必須先進(jìn)存力

安世事件警示錄:當(dāng)先進(jìn)封裝設(shè)備成為AI算力新戰(zhàn)場

算力板卡:驅(qū)動智能時(shí)代的核心引擎

一文看懂AI算力集群

揭秘瑞芯微算力協(xié)處理器,RK3576/RK3588強(qiáng)大算力搭檔

算力即國力,比克電池如何為AI時(shí)代“蓄能

大算力芯片的生態(tài)突圍與算力革命

算力領(lǐng)域常用名詞解釋

算力時(shí)代,進(jìn)擊的先進(jìn)封裝

算力時(shí)代,進(jìn)擊的先進(jìn)封裝

評論