多核的微控制器(MCU)向來是設計上的一大挑戰,尤其是多核異構的設計。而MCU雙核作為其中的精簡版本,憑借其超強的處理性能和便捷開發的特性,很快受到業界的好評。先楫半導體先后推出了幾款高性能MCU雙核產品,集成 2 個 RISC-V 處理器,其中HPM6700系列兩個核的最高主頻都可以達到816MHz。本文通過對先楫HPM6000系列雙核的使用方法、工程編譯與調試、雙核通信方式和資源分配等內容的介紹,全方位給大家介紹雙核的使用和操作,讓大家輕松玩轉雙核,完成更多的片上系統功能開發。

接下來,讓我們看一看HPM6000系列雙核MCU是如何玩轉起來的吧~

雙核簡介

Introduction

HPM6000系列的雙核配置,均集成 2 個 RISC-V 處理器,雙核采用主從結構。CPU0 和 CPU1 采用相同配置,如下:

● 支持相同指令集

● 相同容量的 L1 指令和數據緩存

– 32KB L1 I-Cache,4-way,128x 64B cache line per way

– 32KB L1 D-cache,4-way,128x 64B cache line per way

● 相同容量的指令和數據本地存儲器:256 KB ILM 和 256 KB DLM

CPU0 和 CPU1 采用相同的存儲器映射,以下為例外:

● CPU 自身的指令/數據本地存儲器 ILM / DLM 為私有;

● FGPIO 為私有

● 平臺中斷控制器 PLIC 為私有

● 軟件中斷控制器 PLICSW 為私有

● 機器定時器 MCHTMR 為私有

雙核的三種使用方法推薦

Recommendation

不論是在RAM中運行,還是片上Flash運行,雙核固件均是存儲在Flash上。客戶根據應用場景,選擇在上電后將雙核各自的鏡像從Flash中裝載到RAM中執行或者基于Flash片上執行。

根據應用場景,選擇合適的運行方式,推薦以下幾種:

方案一:Core0 加載到RAM運行,Core1加載到RAM運行

RAM區域可以是各自的ILM,也可以片上的SRAM,或者是SDRAM。當然,裝載CODE的RAM區域各自都是獨立的。此方案應用與雙核固件均占用小,可完全裝載到RAM中運行。

固件存儲位置:Core0和Core1的固件均存放在Flash指定區域(Flash分區規劃)。上電后,BootRom 從指定Flash區域裝載Core0鏡像到指定RAM運行(type:debug/release),Core0運行后從指定Flash 區域裝載Core1鏡像到指定RAM,然后運行Core1。

方案二:Core0基于flash xip(flash片上執行)運行,Core1加載到RAM運行

此方案應用與Core0核固件占用大, Core1核固件占用小。通常將Core0用來做應用復雜交互,Core1用來做高實時性,高性能的觸發邏輯。

固件存儲位置:

1). Core0和Core1的固件各自存放在Flash的指定區域(Flash分區規劃)。

優點:Core0和Core1可單獨OTA。

缺點:需要維護兩個固件BIN文件,并存放到各自的區域中。

2). Core1的固件以數組(只讀區)鏡像的方式存儲在Core0的固件中,Core0固件存放在Flash指定區域;官方例程中使用此方案。

優點: 只維護一個固件。

缺點:Core0和Core1不可單獨OTA。

方案三:Core0基于flash xip0(flash片上執行)運行,Core1基于flash xip1(flash 片上執行)運行

此方案應用與Core0核和Core1核固件均很大,雙核均無法滿足放到RAM中運行。

注意:由于雙核均基于flash片上執行,如果使用同一個flash XPI,會出現并發訪問Flash的情況導致未知異常發生;如果強制順序訪問,訪問效率極低,嚴重拖垮CPU運行速率;故不建議兩個核使用同一個flash XPI片上執行。建議使用XPI0和XPI1各自外掛一個FLASH,分別用于Core0 Flash xip0和Core1 Flash xip1。

固件存儲位置:Core0和Core1的固件存儲在各自外掛的Flash的指定區域中。

雙核工程編譯與調試

Compilation and Debugging

HPM雙核是集成了兩個RISC-V 處理器,是兩個完全獨立的CPU,故HPM雙核工程是Core0工程和Core1工程兩個獨立的工程。因此HPM雙核工程編譯,其實是兩個獨立的單核工程的編譯。用戶只需要建立core0和core1的各自工程編譯調試即可。

由于HPM-SDK例程中使用的是方案二,且Core1的固件以數組(只讀區)鏡像的方式存儲在Core0的固件中,導致Core1工程為Core0工程的關聯工程。因此在構建工程時,必須先構建生成Core0工程,作為關聯工程Core1工程會自動生成。由于Core1的固件是Core0工程中的只讀數組,故必須先編譯Core1工程生成只讀數組鏡像后,再編譯Core0工程。

如下構建編譯調試雙核hello world工程:

A. 構建工程

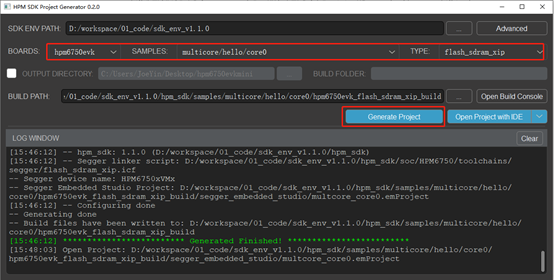

先構建生成Core0工程:

由于Core0是flash片上執行,故type選擇:flash_sdram_xip或flash_xip

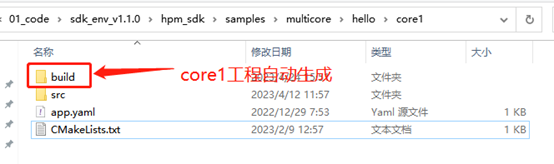

作為關聯工程Core1工程會自動生成:

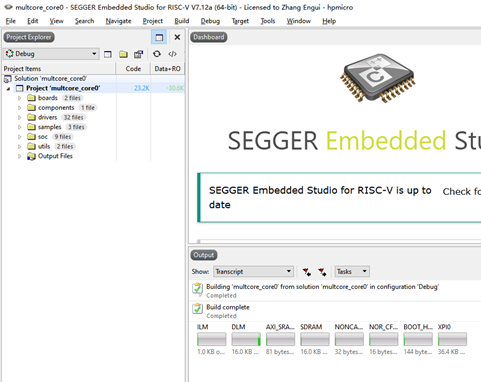

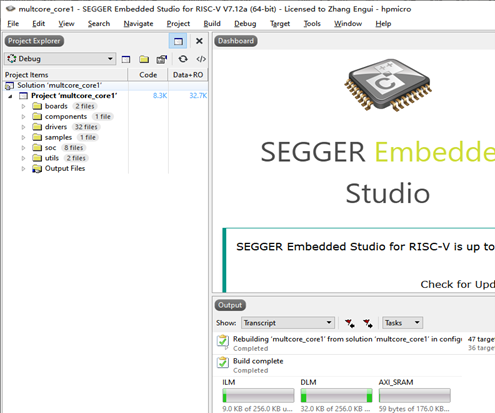

B. 編譯工程

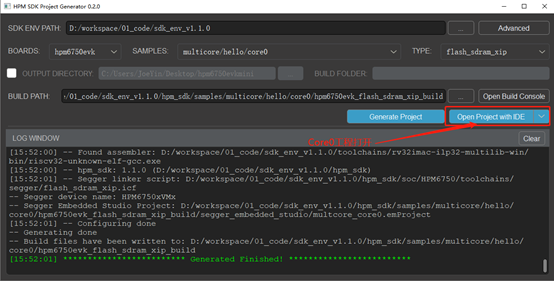

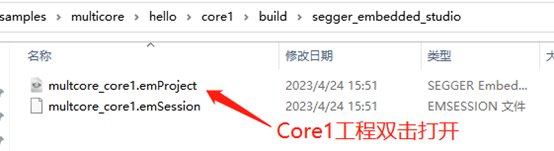

打開各自的工程(Core0通過GUI工具直接點擊Open Project with IDE, Core1對應目錄下雙擊打開工程)。

用SES編譯各自的工程即可。

C. 工程調試

一、雙核同時調試

基于OpenOCD調試(FT2232/DAP-LINK等)。

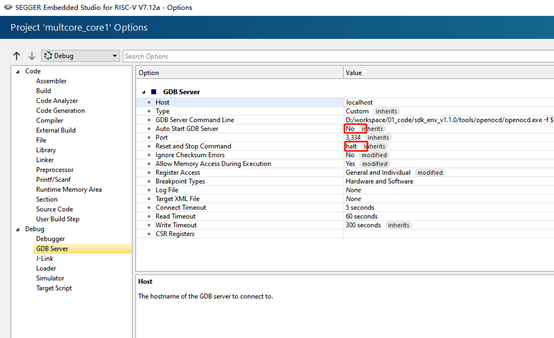

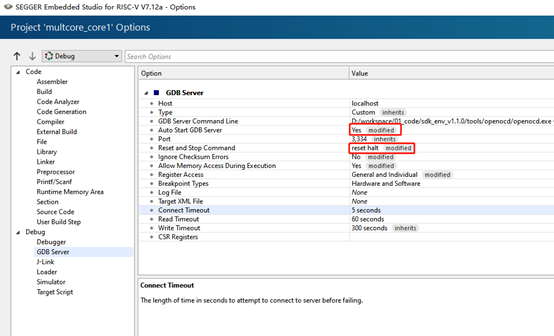

為了達到Core0和Core1同時調試,基于OpenOCD調試在HPM-SDK例程中,對Core1的Debug做了如下限制:

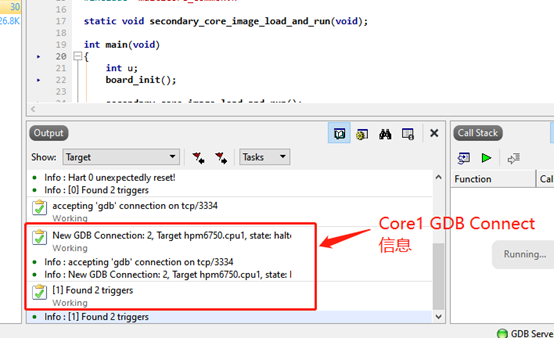

1)Core1不啟動GDB Server,連接Core0啟動的GDB Server。當然使用不同的port來區分是Core0(Port:3333)還是Core1(Port:3334)。

2)Reset 和 Stop時,直接hart停止運行。

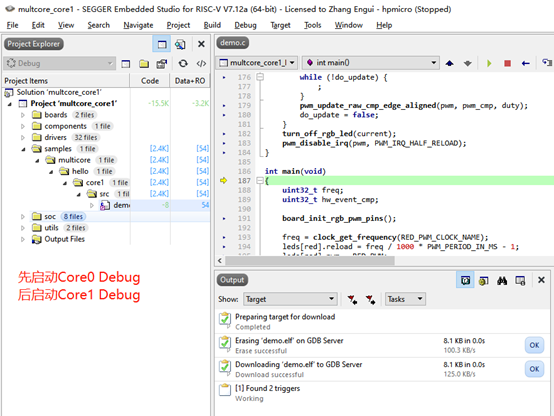

如下圖:

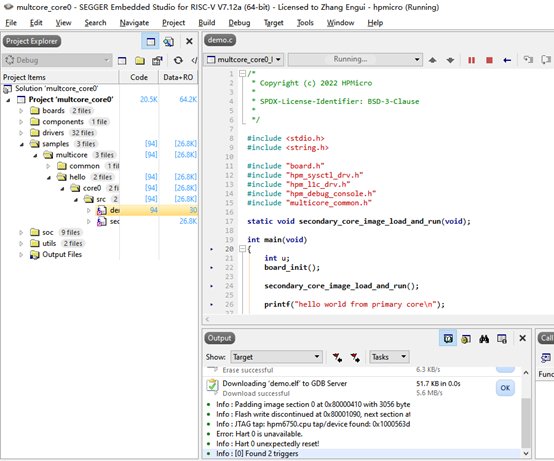

因此,調試HPM-SDK雙核例程,步驟如下:

步驟1:Core0的工程調試,和正常的單核調試相同,正常SES啟動debug即可。

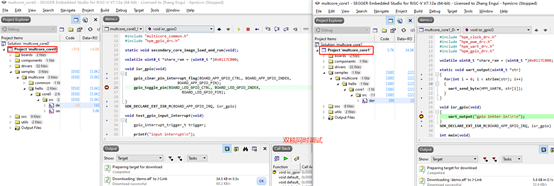

步驟2:Core1的工程調試,由于上述限制(為了雙核同時調試),必須先將Core0的工程Debug運行,然后在啟動Core1的Debug仿真。

可在Core0 SES終端看到Core1 GDB connect信息:

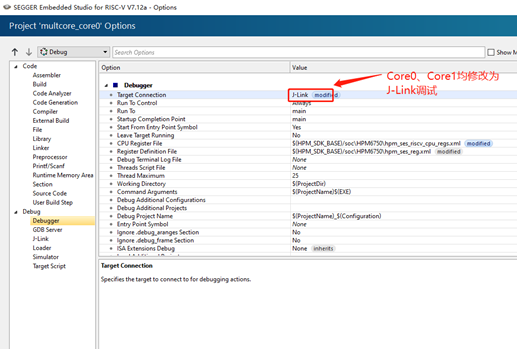

基于Jlink 調試

基于Jlink調試,對Core0和Core1的Debug做如下修改:

1. Core0 修改Debug連接target為:J-Link

2. Core1修改Debug連接target為:J-Link

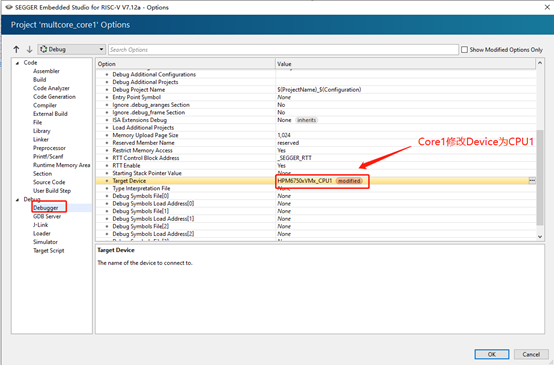

3. Core1修改Debug Device為:HPM6750xVMx_CPU1

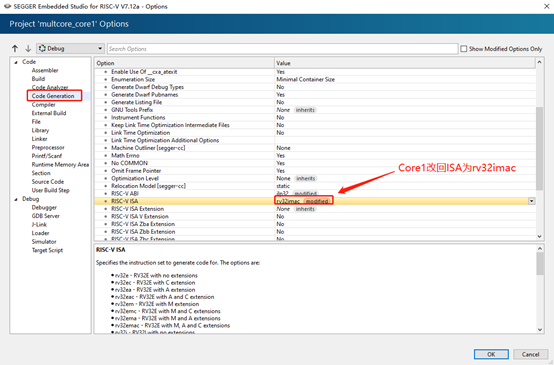

4. 由于SES修改Device為CPU1(上一步驟修改),聯動修改ISA為:rv32i,導致編譯等異常。故在Code Generation下改回ISA為:rv32imac。

5. 通常初始化時鐘等外設在Core0中完成,故為了雙核能同時調試,需先運行Core0 Debug至完成時鐘等外設初始化后,方可Core1 Debug運行。

二、雙核單獨調試

基于 OpenOCD 調試

如果只用來單獨調試Core1(Core0的單獨調試不做任何修改即可),可修改Core1的Debug配置,如下:

Auto Start GDB Server: Yes

Reset and Stop Command: reset halt

修改后, 可直接啟動Core1 Debug運行。

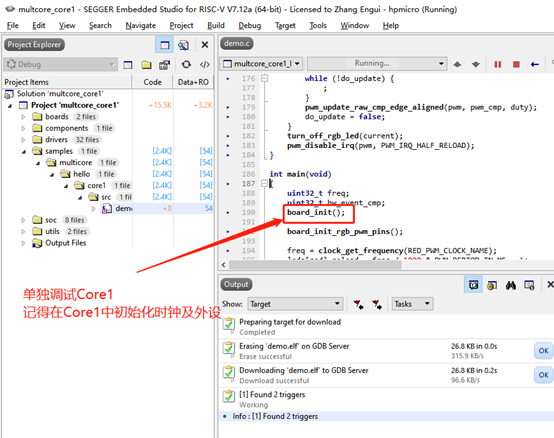

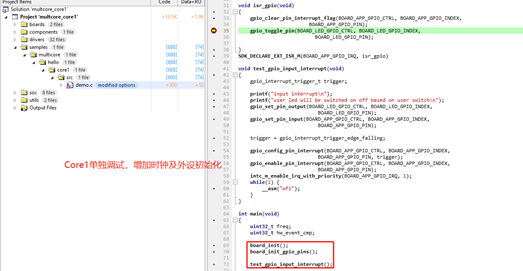

注意:由于CPU0,CPU1主從架構,通常外設等時鐘初始化會在Core0中完成。如果是單獨調試Core1,為了確保程序能正常運行,需在Core1工程中初始化時鐘等外設。如下:

基于 Jlink 調試

單獨調試Core1 (Core0的單獨調試不做任何修改即可),JLink修改同雙核JLink修改一致(可參考上方介紹的內容)。

同樣為了確保Core1能正常運行,需在Core1工程中初始化時鐘等外設。

下一篇,我們將會給各位小伙伴們介紹雙核的通信方式、資源分配和雙核應用eRPC架構,敬請期待。

-

mcu

+關注

關注

147文章

19036瀏覽量

401411 -

先楫半導體

+關注

關注

12文章

286瀏覽量

3361

發布評論請先 登錄

銳能微RISC-V雙核MCU芯片在智能電表中的應用

如何在rt-thread studio上開發STM32H747這類雙核的單片機?

單核CPU網關和雙核CPU網關有什么區別

Analog Devices Inc. ADSP-SC592 SHARC+?雙核DSP數據手冊

先楫半導體HPM6E8Y:先楫實時控制芯片驅動的機器人關節“芯”時代

【強勢上新】HPM5E00:EtherCAT運動控制MCU,先楫半導體再拓工業總線產品新版圖

【強勢上新】HPM5E00:EtherCAT運動控制MCU,先楫半導體再拓工業總線產品新版圖

雙核智控,破界芯生|國內首款Arm? Cortex?M7+M4雙核異構MCU發布

玩轉MCU雙核(上) 先楫HPM6000系列雙核怎么玩?答案超乎你想象!

玩轉MCU雙核(上) 先楫HPM6000系列雙核怎么玩?答案超乎你想象!

評論