High-speed serial interface

JESD204

接

口

JESD204標準專用于通過串行接口傳輸轉換器樣本。2006年,JESD204標準支持單通道上的多個數據轉換器。以下修訂版本:A、B、C相繼增加了支持多通道、確定性延遲、錯誤檢測和糾正等功能,并不斷提高通道速率。JESD204的應用十分廣泛,包括電信(無線、波束賦形、5G),航空航天(衛星通信、成像)和其他使用告訴ADC或DAC的行業。

1

JESD204的發展歷史

2006年,轉換器分辨率和速度的提高推動了對用于處理轉換器數據的高效串行接口的需求。JESD204A增加了對多通道和鏈路的使用以實現通道/器件同步。JESD204B允許單獨的時鐘驅動系統設備并引入確定性延遲。在8b10b編碼下,建議的最大速度增加到12.5Gbps。JESD204C將通道速率提高到32Gbps,并改為使用CRC和FEC的64b66b編碼。新的JESD204D目前正在開發中,該版本將使用帶有RS-FEC的PAM 4將通道速率提高到116G。

2

轉換器面向數據的框架

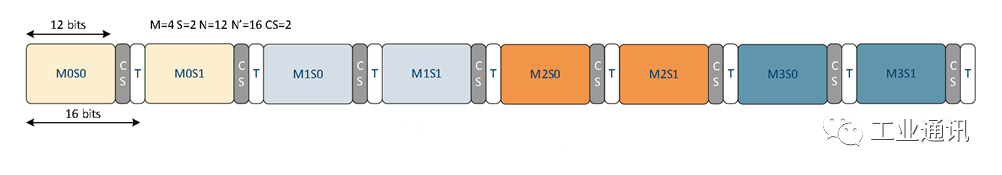

01 JESD輸入參數數據

?M - 每個鏈接的轉換器

? S - 每個轉換器的樣本

? N - 每個樣本的位數(分辨率)

? CS - 每個樣本的控制位

? N' - 樣本容器 N' >= N+CS

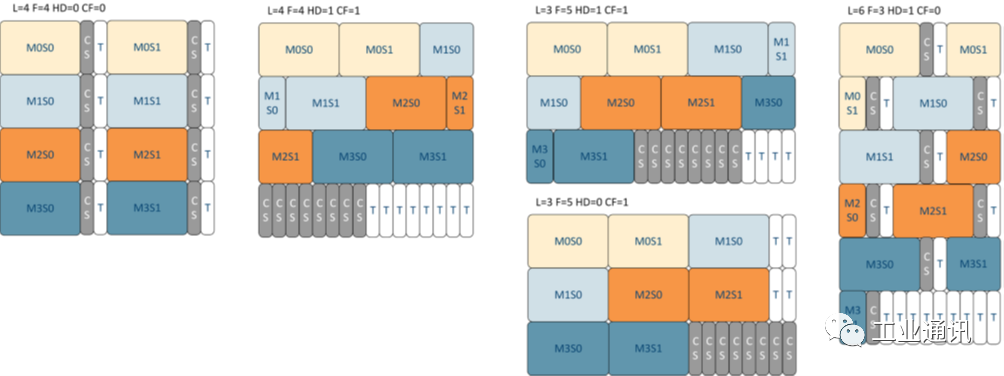

02 JESD成幀參數

? L - 每個鏈路的通道

? F - 每通道幀中的8位字節

? K - MultiFrame (204B) 中的幀

? E - 擴展多塊中的多塊 (204C)

? HD - 高密度(允許樣品拆分)

? CF - 控制幀(幀末尾的 CS)

轉換器樣本連續組合成一個幀,然后跨通道拆分

3

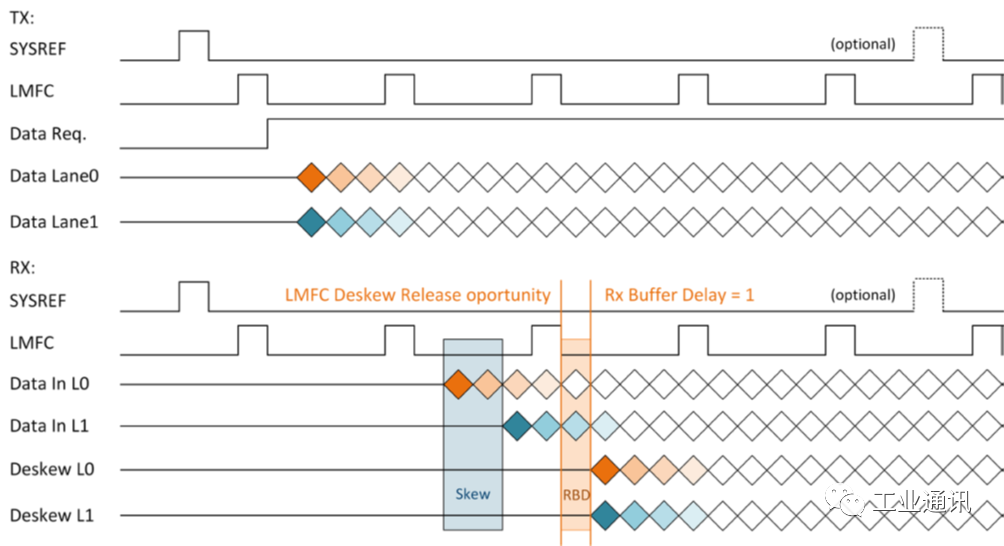

確定性延遲

JESD204B中引入的確定性延遲允許系統在整個復位、上電周期以及重新初始化事件中保持恒定的系統延遲。在大多數情況下,這是通過提供一個系統參考信號 (SYSREF) 來實現的,該信號在發送器和接收器之間建立一個公共時序參考,并允許系統補償任何延遲可變性或不確定性。

4

主要陷阱和隱患

圍繞JESD204標準進行系統設計的主要陷阱和隱患將涉及子類1中的系統時鐘,其中確定性延遲是通過使用SYSREF實現的,SYSREF的生成和在不同系統條件下的利用也很關鍵。選擇正確的幀格式和SYSREF類型來匹配系統時鐘的穩定性和鏈路延遲十分具有挑戰性。

規范對處理CRC和FEC的比特順序并不總是很清楚,技術圖紙與真值表不匹配,這種差異會導致不同的實現方式,造成不兼容問題。虹科合作伙伴Comcores已經采取了措施來防止這些陷阱和隱患,如位的交換。如果需要這方面的技術支持,歡迎聯系虹科技術工程師。

為什么選擇

虹科JESD204 IP?

/ Comcores

虹科Comcores JESD204 IP已在所有主要代工廠和低至5nm的工藝中進行了多次流片。此外,該JESD IP已通過與所有主要數據轉換器和SerDes/PHY的互操作性測試,從而實現了高度兼容的設計。

-

轉換器

+關注

關注

27文章

9418瀏覽量

156364 -

模擬

+關注

關注

7文章

1447瀏覽量

85387

發布評論請先 登錄

高速數據傳輸新利器:TSER9615串行器解析

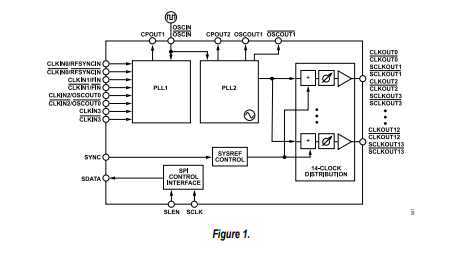

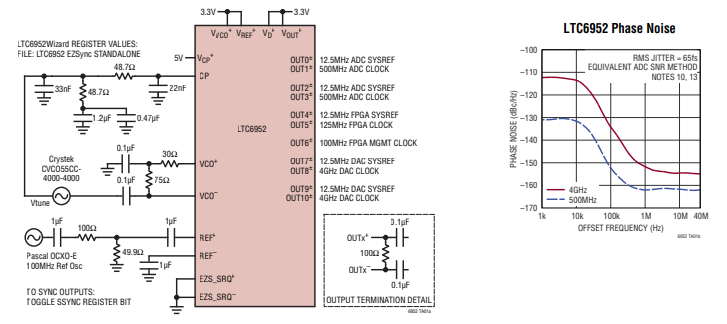

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

JEDSD204B標準verilog實現-協議演進

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

虹科干貨 | 使用JESD204串行接口高速橋接模擬和數字世界

虹科干貨 | 使用JESD204串行接口高速橋接模擬和數字世界

評論