寄生電容的定義

寄生電容影響電路機理

消除寄生電容的方法

當你想到寄生蟲時,你可能會想到生物學上的定義——一種生活在宿主身上或在宿主體內的有機體,從宿主身上吸取食物。從這個意義上說,寄生蟲可能是巨大的麻煩或導致嚴重的健康問題。

當然,作為一個PCB設計人員,您可能知道另一種寄生蟲—寄生電容。雖然您不必擔心電路中的生物寄生,但了解如何消除寄生電容可以幫助提高PCB設計中的信號完整性和性能。

什么是寄生電容?

寄生電容是一種現象,即電路中的元件在物理上不是電容時表現得像電容。如果回顧一下電容的基礎知識,就更容易理解寄生電容的概念。 電容器由被絕緣材料隔開的兩個導電元件組成。當兩個導體都受到差電位的驅動時,電荷就在它們之間積累起來。積聚的電荷用電容表示,公式為C = q/V。 物理電容器是根據上述原理構造的,目的是有意地在電路中儲存電荷。然而,電容也可能存在于電路的元件之間,只要元件之間的距離符合形成電荷的要求。 電路中形成的非預期電容稱為寄生電容。寄生電容可以在兩個導體、襯墊、導體和相鄰地平面之間,或任何兩個滿足電荷積聚標準的元素之間產生。當電路的各部分相互接近且電壓水平不同時,寄生電容的可能性最大。

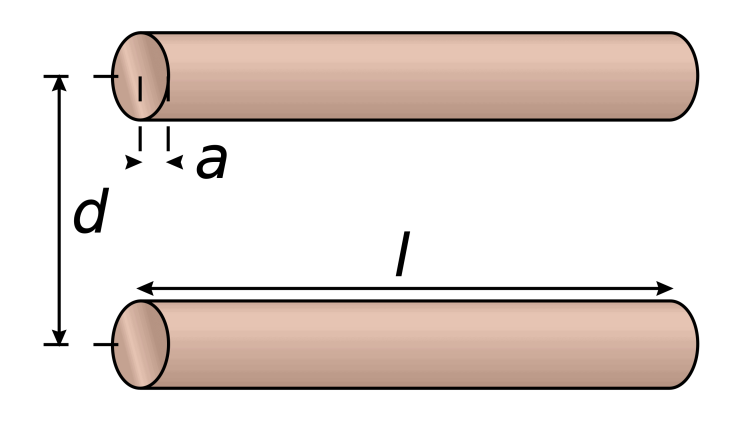

導體間寄生電容是面積與距離的關系

上圖顯示了電路中兩個導體之間的電容是如何產生的。當導體被置于不同的電位水平時,所積聚的電荷由下式決定: C= (?×a) /d,其中?為導體之間絕緣體的介電常數。

寄生電容影響電路的機理?

在高頻時,寄生電容會導致短路。

寄生電容很可能存在于電路中,對于低頻設計,它不太可能造成重大的問題。然而,寄生電容在高速設計中可能就必須被重視。 隨著頻率的增加,電容的行為發生變化,最后,可能會形成一個短路的行為。當高速信號通過一個元件時,寄生電容也會產生同樣的效果。 在放大器設計中,在輸入和輸出之間形成的寄生電容可能導致不必要的反饋。通常的開路電路在高頻工作時變得導電,并在放大器電路中引起不必要的振蕩或寄生振蕩。 寄生電容對于兩個相鄰的導體來說是很麻煩的。當其中一個導體攜帶高頻信號時,它會給另一個導體帶來串擾。寄生電容越大,EMI噪聲越大。 寄生電容不僅會產生干擾,還會影響信號本身的完整性。例如,寄生電容可以建立在導體和地平面之間。在高頻時,兩個元件都趨向于短路,并將改變導體上的信號。

消除寄生電容的方法?

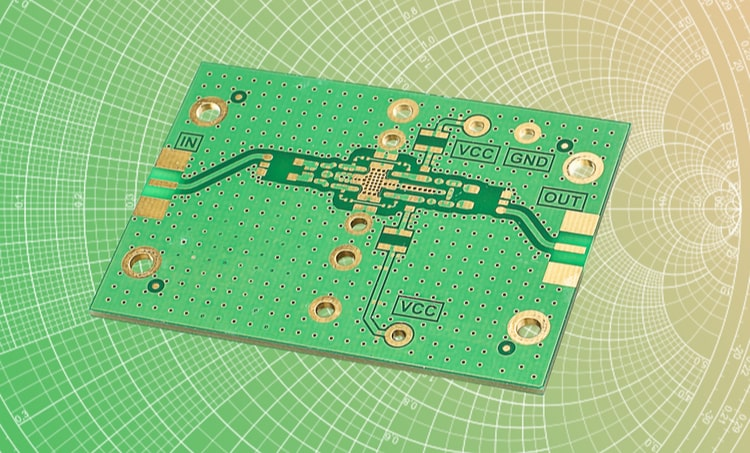

去除內地層,有助于降低寄生電容

考慮到在許多PCB設計中電路密度持續增加,消除寄生電容是不可能的。但是,您可以通過應用這些策略來減少它的影響。

01

增加導體之間的間隙

如果可能的話,在設計中使得布線之間保持盡量寬的間隙。這是因為,電容與導體之間的距離成反比。較寬的間隙將降低寄生電容和交叉耦合等影響。

02

適當的使用地平面

建議使用內層接地面,以減少雜散電感、EMI和散熱,但請記住,它也可能增加寄生電容。在用地平面覆蓋整個內層之前,需要考慮一下利弊。

03

減少過孔

在構建緊湊的PCB時,過孔是有用的,但過孔過多會引入顯著的寄生電容。少用過孔,并盡量避免任何高速線上打過孔。

Cadence提供全套的PCB設計工具,仿真工具以確保PCB設計一次成功。

此外,我公司戰略合作伙伴北京迪浩永輝技術有限公司推出了CMS Schematic Audit-原理圖設計規則、規范性自動化分析軟件;CMS DesignPlus-PCB以及芯片封裝設計以及工藝規則自動化分析軟件完全集成Cadence工具集,在設計軟件中實現In-Design分析,軟件具有高度可擴展性,使得用戶結合自身產品形成特有的規則知識庫可隨時加入軟件中,以促進設計效率的提高。

-

電容

+關注

關注

100文章

6484瀏覽量

159322

發布評論請先 登錄

TH2839阻抗分析儀在LED驅動集成電路寄生參數測試分析中的應用

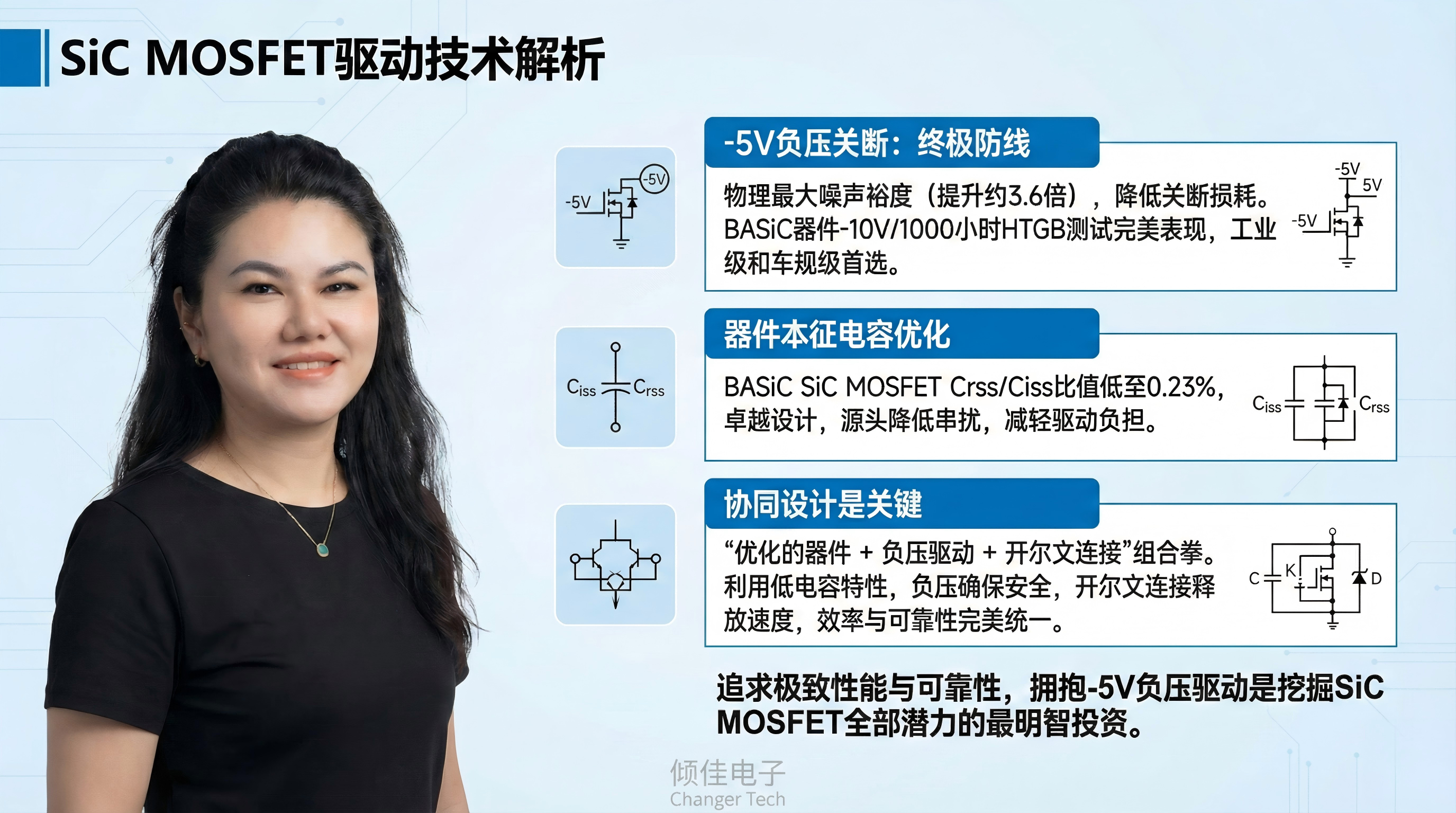

碳化硅MOSFET串擾抑制策略深度解析:負壓關斷與寄生電容分壓的根本性優勢

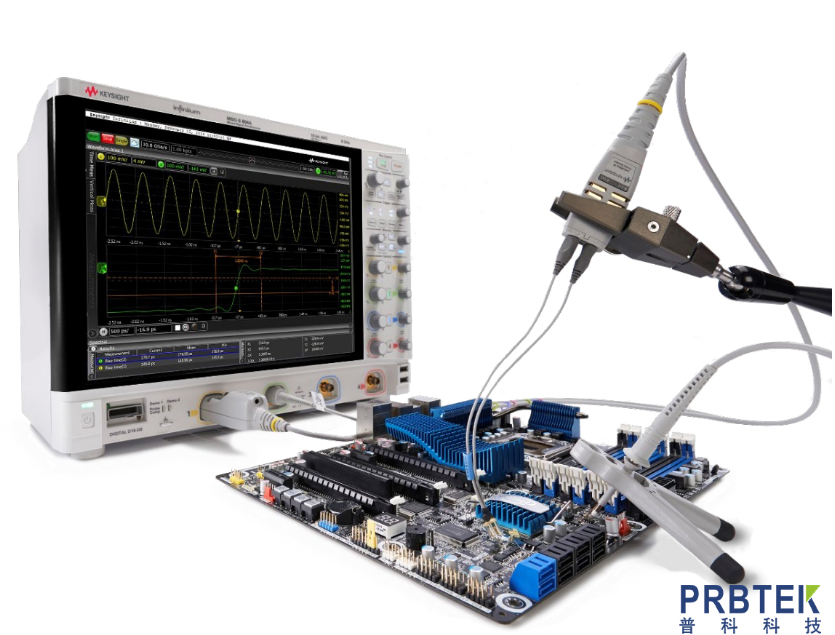

高速示波器時延校準實操:單邊單信號法從準備到驗證的全步驟指南

電源功率器件篇:線路寄生電感對開關器件的影響

示波器無源探頭補償調試全指南

逆變器寄生電容對永磁同步電機無傳感器控制的影響

【干貨分享】電源功率器件篇:變壓器寄生電容對高壓充電機輸出功率影響

LCR測試儀中LP(Parallel)與LS(Series)模式的區別

技術資訊 | 在高速設計中如何消除寄生電容?

技術資訊 | 在高速設計中如何消除寄生電容?

評論