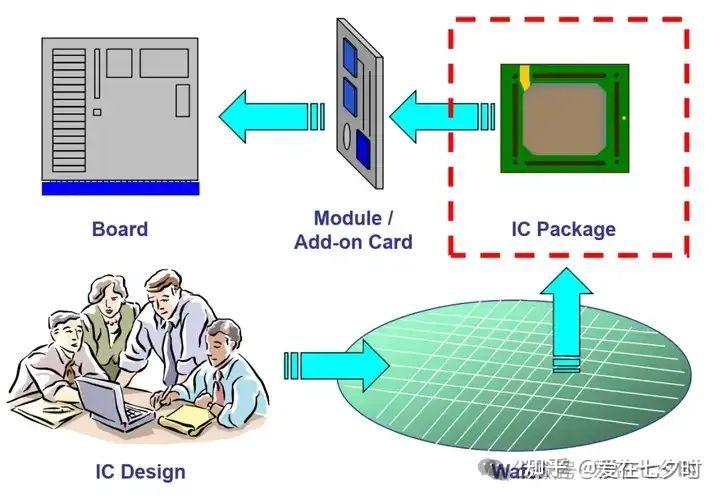

半導(dǎo)體芯片的封裝與測(cè)試是整個(gè)芯片生產(chǎn)過程中非常重要的環(huán)節(jié),它涉及到多種工藝流程。

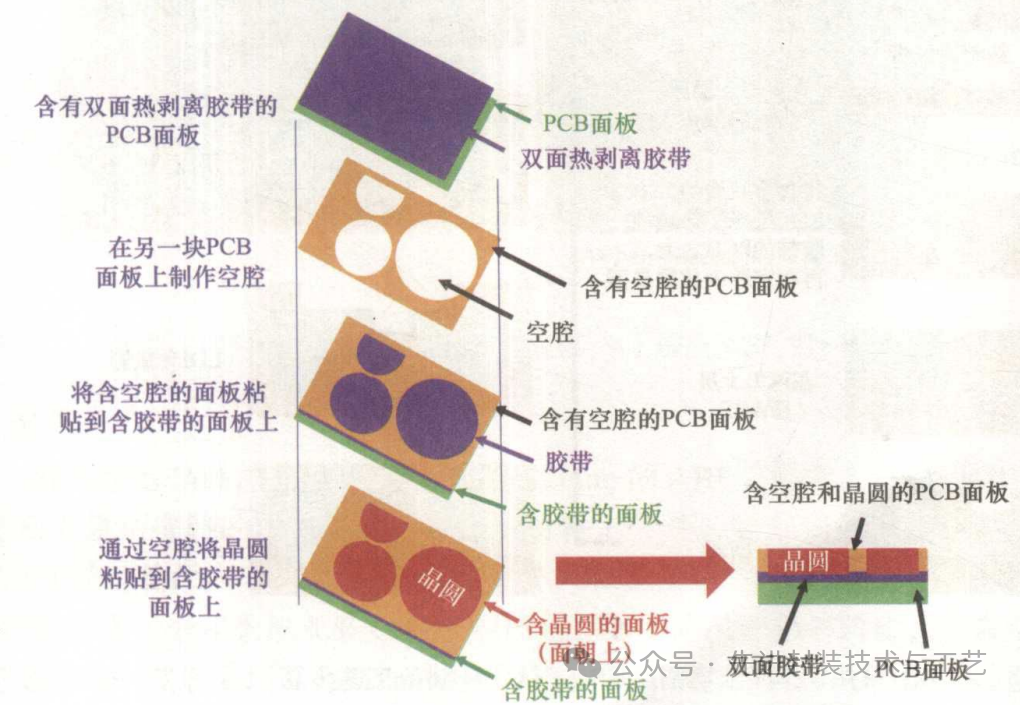

首先,芯片的封裝需要進(jìn)行外觀設(shè)計(jì)和尺寸測(cè)量,以確保符合產(chǎn)品規(guī)格要求。接著,將芯片通過焊接、線纜連接等方式固定在封裝材料內(nèi),并進(jìn)行封裝膠的注入和硬化處理。

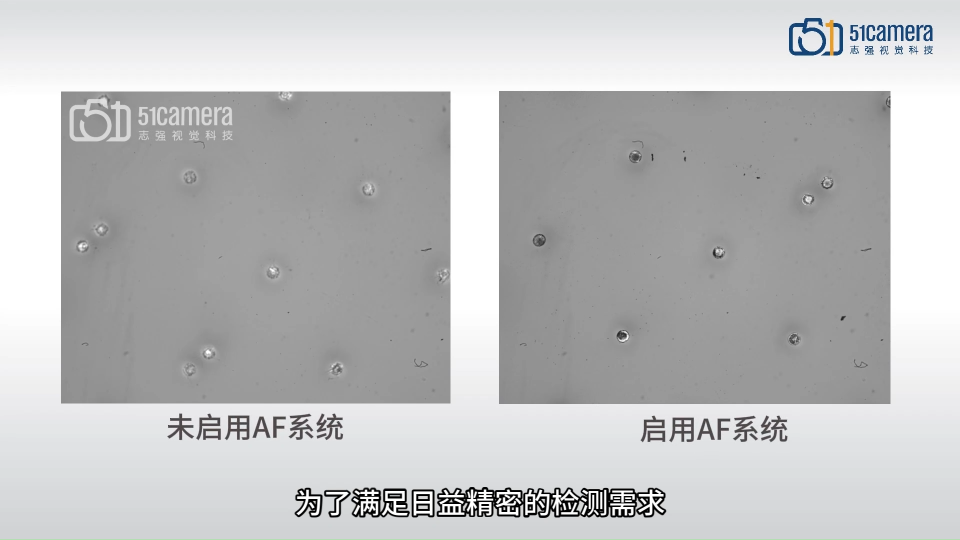

其次,芯片封裝完成后,需要進(jìn)行測(cè)試來驗(yàn)證其性能是否符合標(biāo)準(zhǔn)。這個(gè)過程主要分為功能測(cè)試和可靠性測(cè)試兩個(gè)部分。其中,功能測(cè)試通過模擬各種使用場(chǎng)景對(duì)芯片進(jìn)行測(cè)試,檢查其電氣特性、信號(hào)傳輸、功耗等方面的表現(xiàn)。而可靠性測(cè)試則是對(duì)芯片進(jìn)行高溫、低溫、振動(dòng)、沖擊等復(fù)雜環(huán)境下的長(zhǎng)時(shí)間測(cè)試,以驗(yàn)證其使用壽命和穩(wěn)定性。

最后,在測(cè)試完成后,需要對(duì)芯片進(jìn)行數(shù)據(jù)分析和記錄,以便制定優(yōu)化措施和精益生產(chǎn)策略。通過不斷優(yōu)化封裝和測(cè)試流程,可以提升芯片封裝質(zhì)量和測(cè)試效率,從而滿足市場(chǎng)對(duì)高性能、高品質(zhì)芯片的需求。

審核編輯黃宇

-

測(cè)試

+關(guān)注

關(guān)注

9文章

6201瀏覽量

131345 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30725瀏覽量

264032 -

封裝

+關(guān)注

關(guān)注

128文章

9248瀏覽量

148610

發(fā)布評(píng)論請(qǐng)先 登錄

晶圓級(jí)扇出型封裝的三大核心工藝流程

「聚焦半導(dǎo)體分立器件綜合測(cè)試系統(tǒng)」“測(cè)什么?為什么測(cè)!用在哪?”「深度解讀」

半導(dǎo)體行業(yè)知識(shí)專題九:半導(dǎo)體測(cè)試設(shè)備深度報(bào)告

革新半導(dǎo)體清洗工藝:RCA濕法設(shè)備助力高良率芯片制造

半導(dǎo)體“封裝過程”工藝技術(shù)的詳解;

BW-4022A半導(dǎo)體分立器件綜合測(cè)試平臺(tái)---精準(zhǔn)洞察,卓越測(cè)量

半導(dǎo)體設(shè)備防震基座生產(chǎn)制造全工藝流程介紹-江蘇泊蘇系統(tǒng)集成有限公司

TGV視覺檢測(cè) 助力半導(dǎo)體封裝行業(yè)# TGV檢測(cè)# 自動(dòng)聚焦系統(tǒng)# 半導(dǎo)體封裝

半導(dǎo)體封裝清洗工藝有哪些

半導(dǎo)體行業(yè)案例:晶圓切割工藝后的質(zhì)量監(jiān)控

晶圓蝕刻擴(kuò)散工藝流程

半導(dǎo)體行業(yè)芯片封裝與測(cè)試的工藝流程

半導(dǎo)體行業(yè)芯片封裝與測(cè)試的工藝流程

評(píng)論