三星電子晶圓代工事業部在國際互連技術大會(IITC, International Interconnect Technology Conference)上發表了一篇主題為“EUV Minimum Pitch Single Patterning(EUV單圖案最小節距)”的論文。我們為此特別準備了這篇博文,希望將論文內容和EUV(極紫光外刻)技術的特點分享給更多人。

1. 用更細的筆即可畫出更細的線!

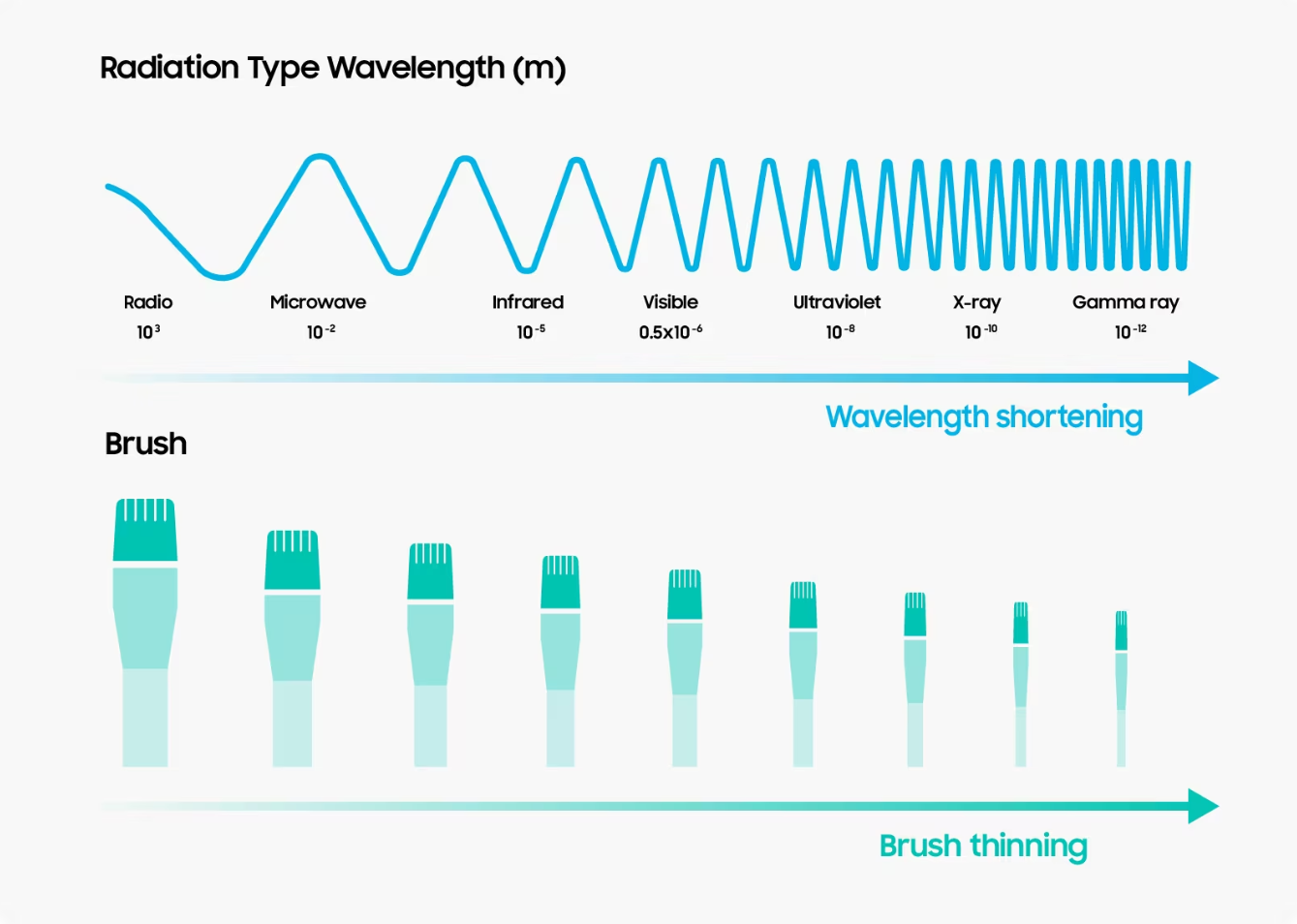

在上一篇博文中,我們了解了光刻技術(Photolithography)所面臨的阻礙,并在文章結尾處提到了如何從根本上解決光的性質帶來的局限性,即縮短波長,因為不同的波長會帶來不同程度的衍射現象。而短波長,能夠縮小衍射的擴散角度,最終克服光刻工藝的局限性。如圖[1]所示,正如想要畫出細線就需要細毛筆一樣,想要突破繪制的局限,用波長更短的光即可。

圖[1] 波長 (Wavelength) 變短類似于畫圖的毛筆變細。

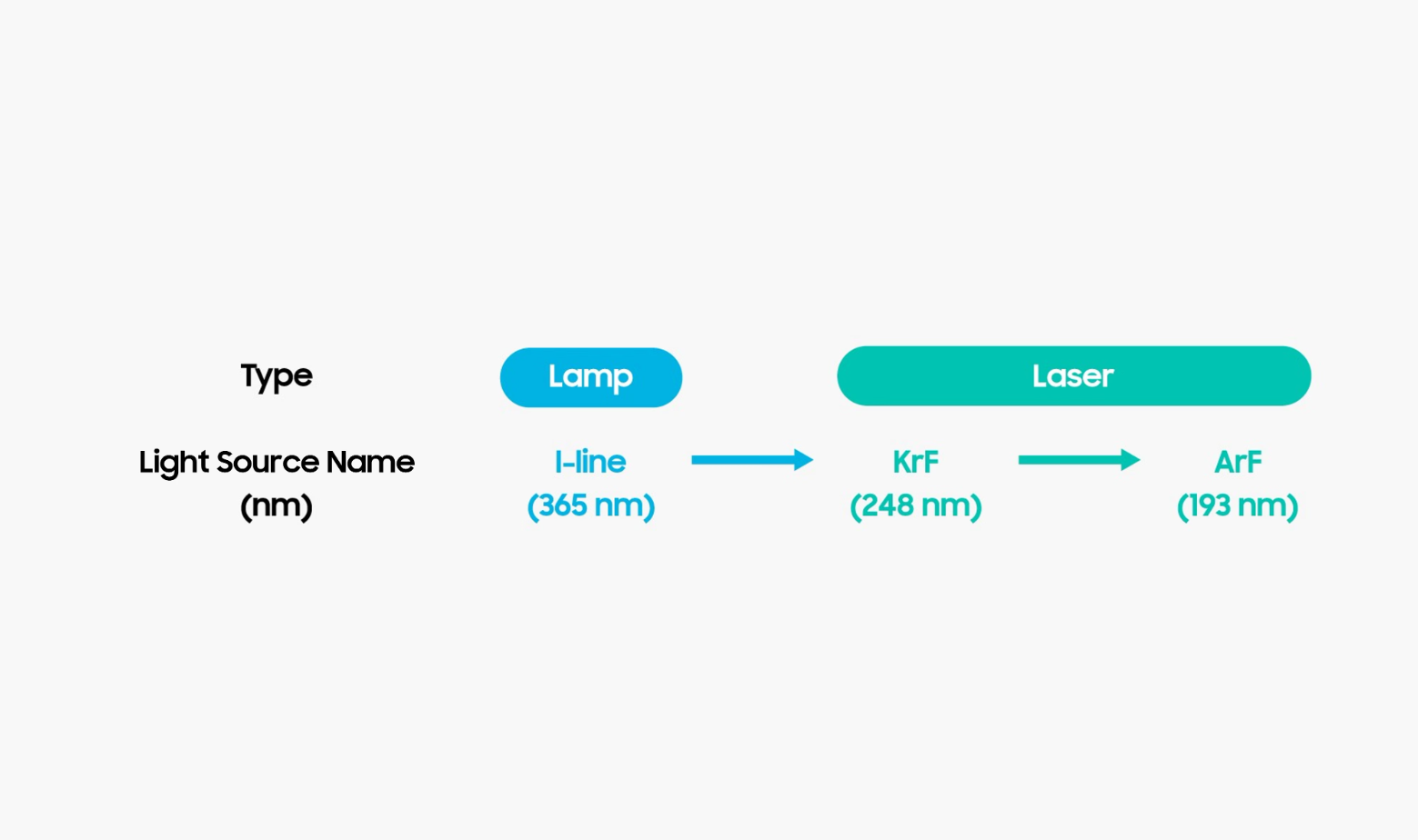

因此,如圖[2]所示,為了繪制更小的圖案,光刻工藝經歷了繪制所用光的波長逐漸變短的發展歷程。

圖[2] 大體來說,光刻工藝使用的光從燈泡光照變為了激光。具體到激光,則是從利用 Kr(氪,Krypton)的 KrF (氟化氪)激光發展到利用 Ar(氬,Argon)的 ArF (氟化氬)激光來改變光源,達到縮短波長的目的。

然而,為了滿足制作更小晶體管的需求,ArF (193 nm) 的波長也不夠短。于是,EUV (極紫光,Extreme Ultra Violet) 應運而生了。

2. EUV (極紫光,Extreme Ultra Violet) 的出師表

為了打破波長的局限性,EUV 解決方案如同彗星一般登場!

EUV 最大的特點就是波長短。為了達到精密繪制的目的,我們需要短的波長,從而需要引入 EUV。

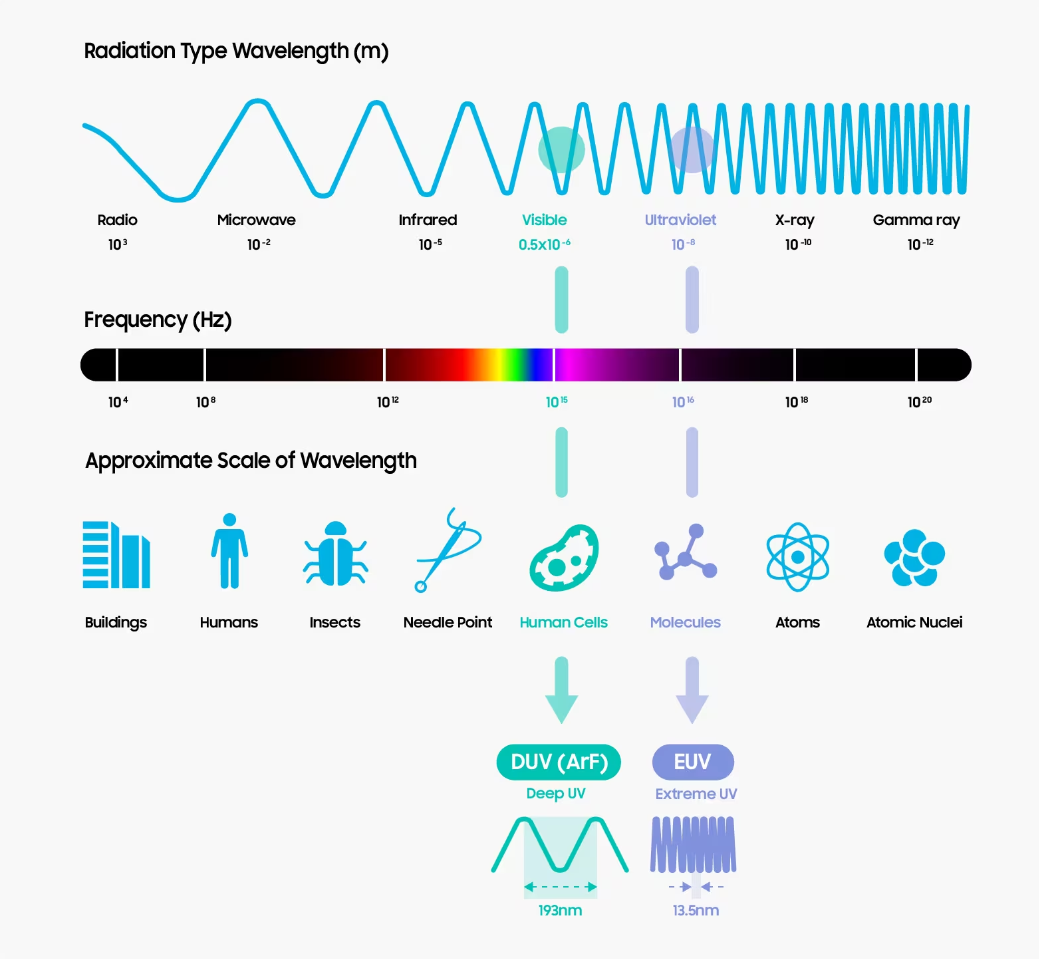

正如圖[3]所示,我們使用的是波長極短的 EUV,只有 13.5 nm。

圖[3] 將波長與我們所熟知物體的大小進行類比。先前使用的 ArF 是波長為 193 nm的一種 DUV (深紫外光,Deep UV),而波長為 13.5 nm的 EUV 甚至比分子更小。

先前使用的 ArF 的波長為 193 nm,而 EVU 的波長僅為 13.5 nm,就波長的差異而言,EUV 本身可以說是一個巨大的變化。那么,光刻工藝在應用了這一巨大變化的主角 EUV 之后,又具備了什么特點呢?讓我們來仔細了解一下。

A. 強大的等離子體發出的短波

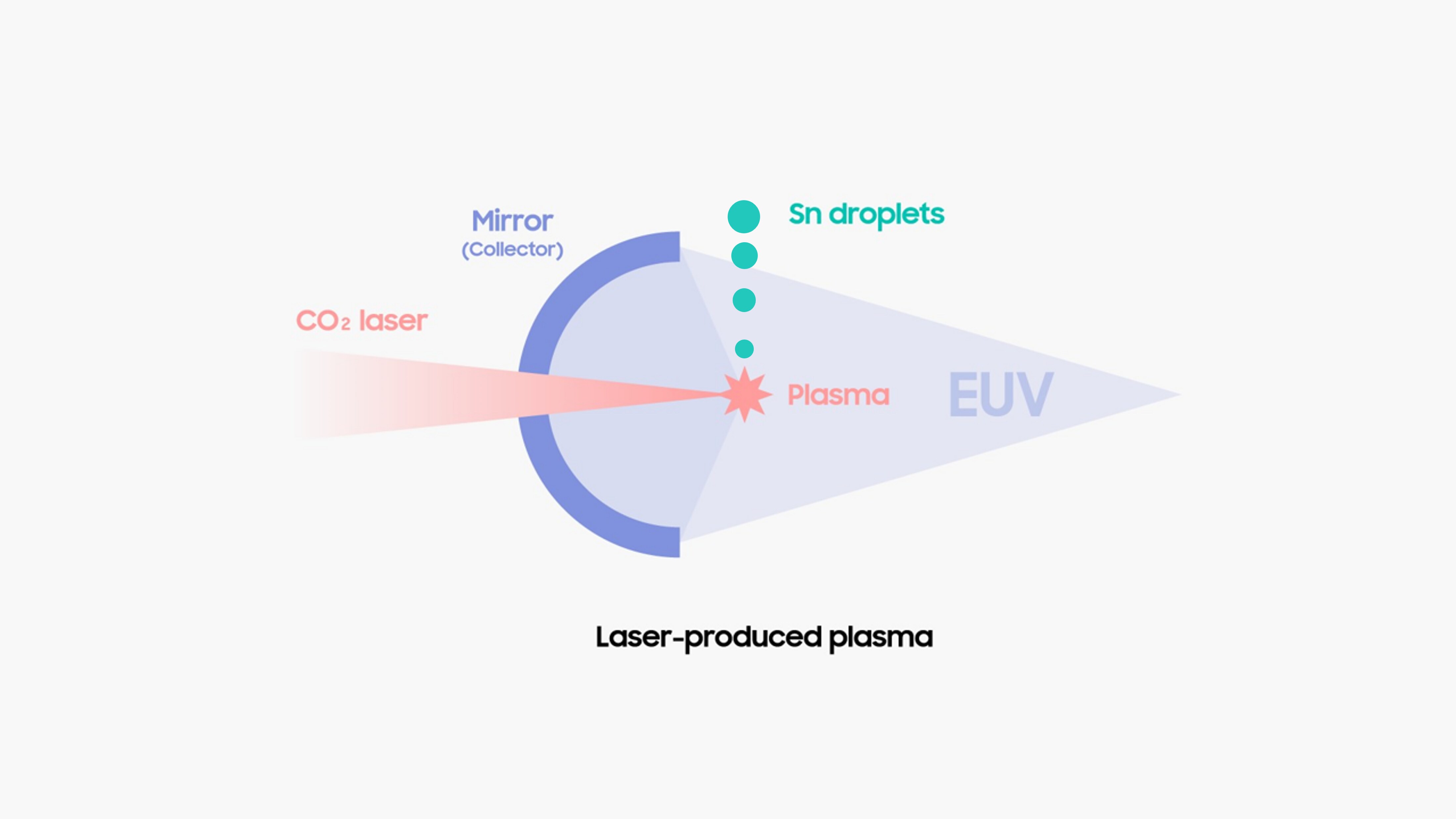

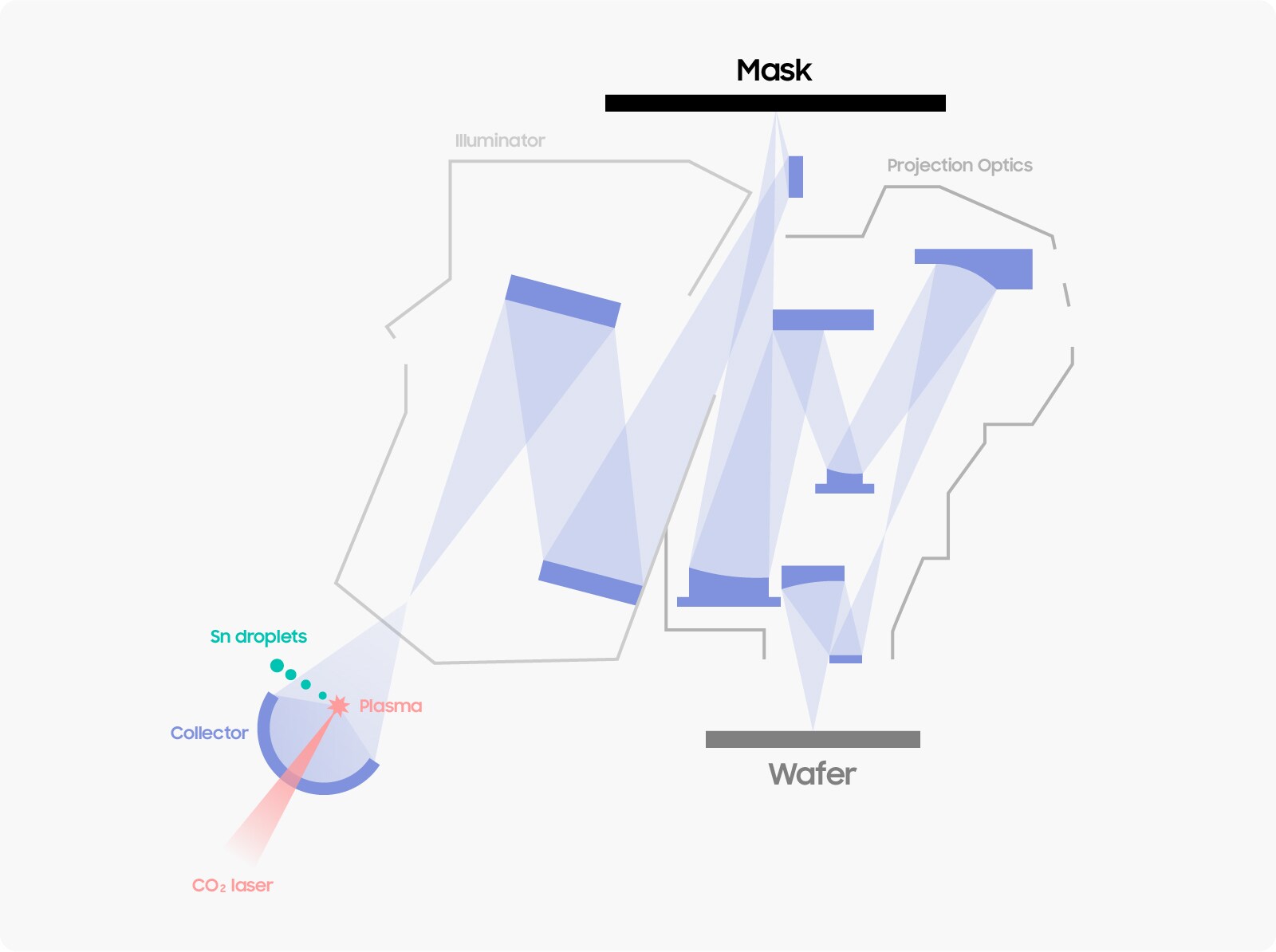

在上方的圖[3]中,可以看到組成彩虹顏色的光的范圍。按照波長由長到短的順序,依次羅列了能夠燒傷人們皮膚的紫外線、可穿透肌肉的 X 射線,還有強大到能夠殺死癌細胞的伽瑪射線。我們也可由此看出,波長越短的光,所蘊含的能量就越大。而相應地,在發射更短波長的光時,需要的能量也通常會更多。做個類比,想要打出全壘打,棒球就要飛得更遠、更快,那么揮舞棒球棒的力度也要更大。然而,先前用于發射 DUV 光的激光,不具備足夠的能量,無法發出我們所需的短波。因此,如圖[4]所示,EUV 使用了處于極高能量狀態的等離子體(Plasma),即氣體被分離為電子和離子的狀態,是固體、液體、氣體之外的另外一種物質狀態,具有很高的能量。

圖[4] 讓 CO2 激光(Laser)與掉落的 Sn(錫)準確碰撞來產生等離子體,并使用鏡子將等離子體生成的光集合起來,最終產生 EUV。

如圖[4]所示,產生 EUV 必須使用一種特制的工具:集合光的鏡子! 鏡子,不僅可用來產生 EUV,更是使用 EUV 的整個工藝流程中不可或缺的重要因素。下面就讓我們來了解一下 EUV 技術中的核心要素:鏡子。

B. 反射光學 - 使用鏡子而非放大鏡

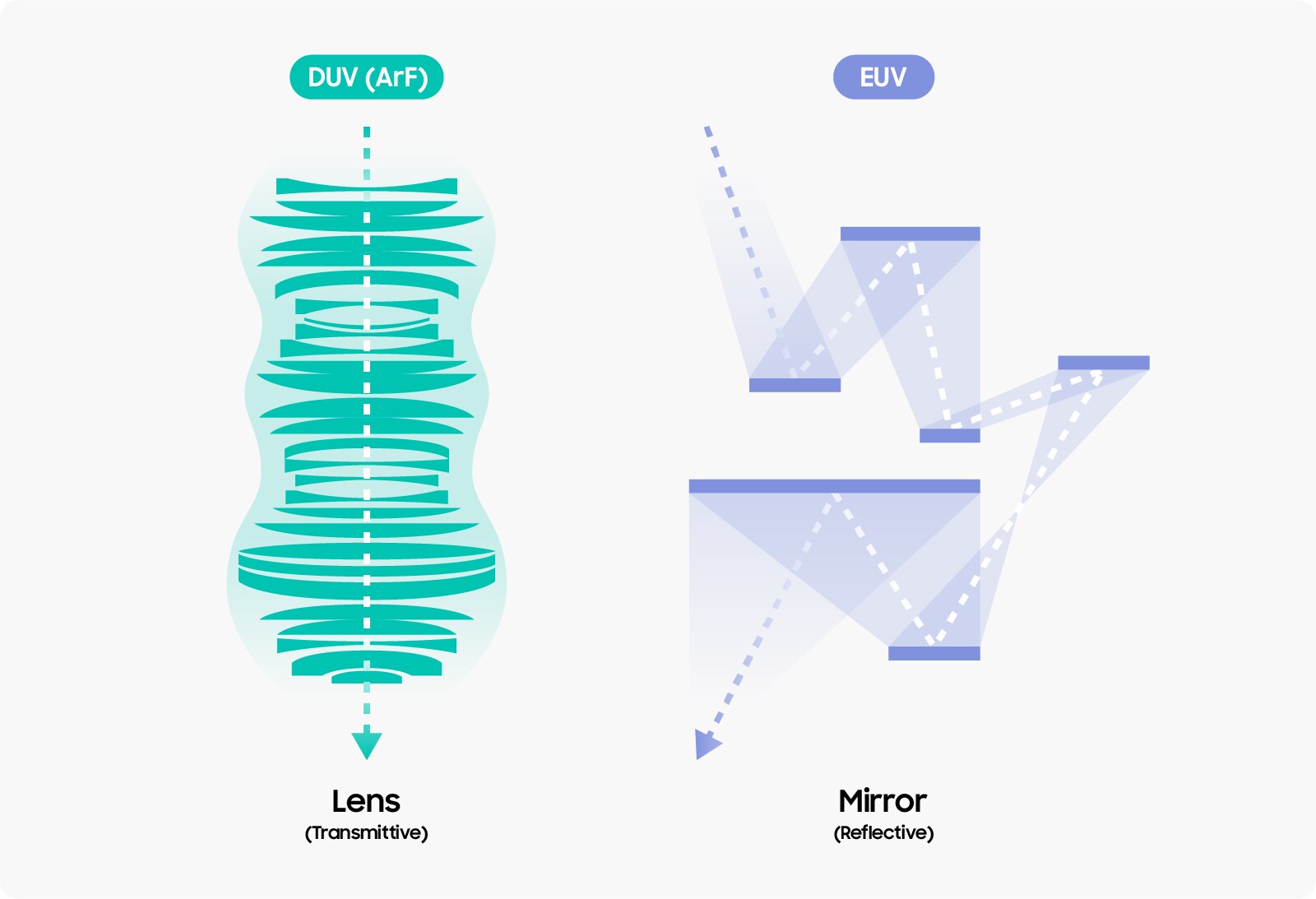

光的特點是波長越短,就越容易被其它物質吸收。EUV 的波長極短,甚至能被大氣吸收。而為防止這種情況出現,EUV 設備(使用了 EUV 的光刻工藝設備)在工序開始前,先將內部進行了真空處理。在操作 EUV 工藝時使用鏡子,也是為了減少光被吸收的類似情況:假如讓波長極短的 EUV 通過透鏡,則會被透鏡大量吸收。因此,通過用鏡子替代先前的透鏡,讓光進行反射而非透射,則可以減少吸收量。只有極大降低吸收量從而讓光像圖[5]一樣安全地到達光刻膠,才能進行完整的繪制。

圖[5] 直到 DUV,光刻技術都一直在使用透鏡,而 EUV 波長較短,使用透鏡會加大吸收率。為改善這一問題,我們使用了吸收率相對較低的反射模式,即通過鏡子來實現。

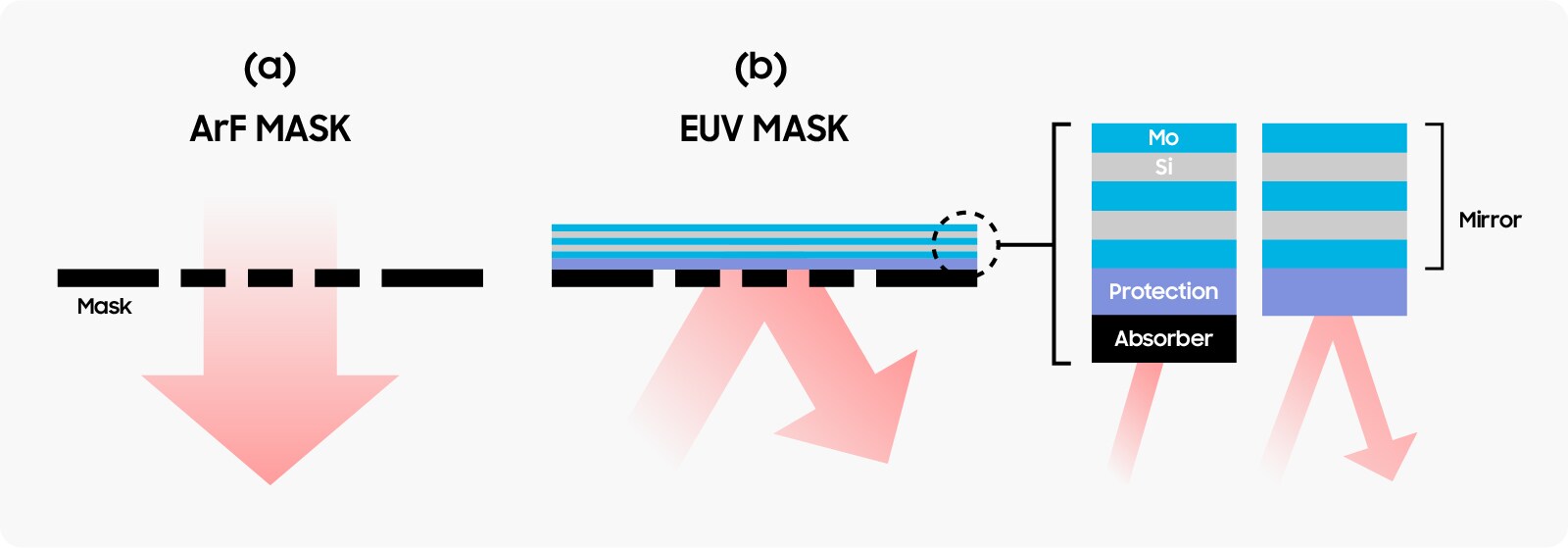

講到這里,大家可能會產生一個疑問。用來透射光的掩膜怎么辦? 利用 EUV 的光刻工藝中所用的掩膜同樣是運用反射原理制成的。如圖[6]所示,將原本(a)形式,遮擋和透射光的掩膜,換成像 (b) 形式,反射和吸收光的掩膜。

圖[6] 為了盡可能降低吸收率,EUV 掩膜使用了 Mo(鉬)和 Si(硅)多層疊加結構的反射鏡,并通過充當保護膜角色的保護層(Protection)來保護鏡子。不應出現反射現象的區域,則使用吸收層(Absorber)(TaN)來吸收光。

通過圖[7],可以直觀地了解以上關于 EUV 光刻工藝的解釋。

圖[7] 展示了 EUV 光刻工藝的整個曝光(向晶片上照射光的)過程。

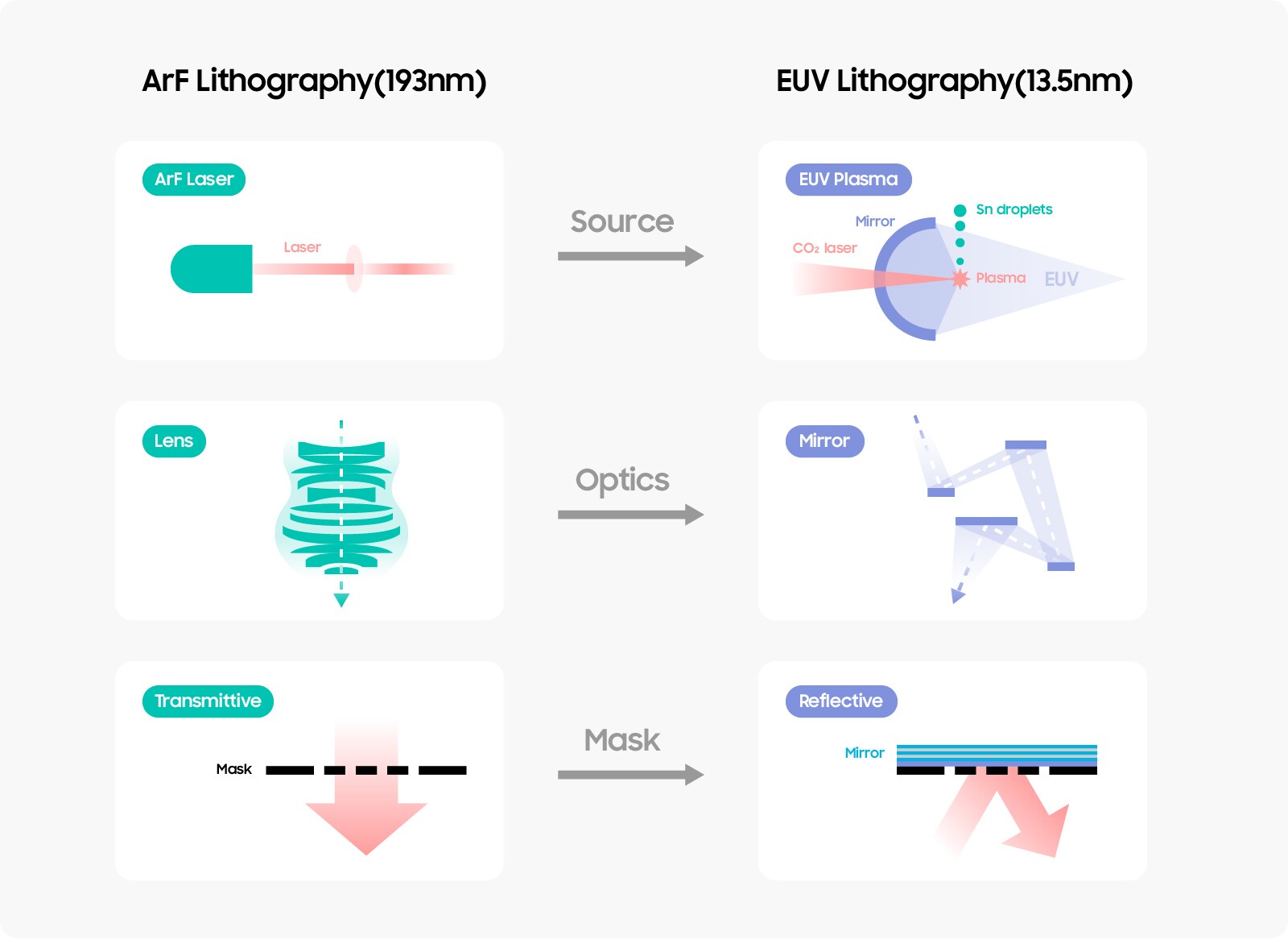

下面再對 EUV 和 ArF 進行簡單的比較,對比內容如圖[8]所示。

圖[8] ArF 光刻工藝利用激光產生光,并使用透鏡(Lens)和透射型(Transmittive)掩膜。EUV 則與之不同,它利用等離子體產生光,并使用鏡子 (Mirror) 和反射型(Reflective)掩膜。

如圖[8]所示,EUV 光刻工藝與先前的工藝完全不同,可以畫出之前無法畫出的更小圖案。然而, EUV 的優勢,并不僅僅在于能夠畫出更小的圖案。

3. 畫出以前難以實現的圖案,省去反復繪制的麻煩,一次搞定!

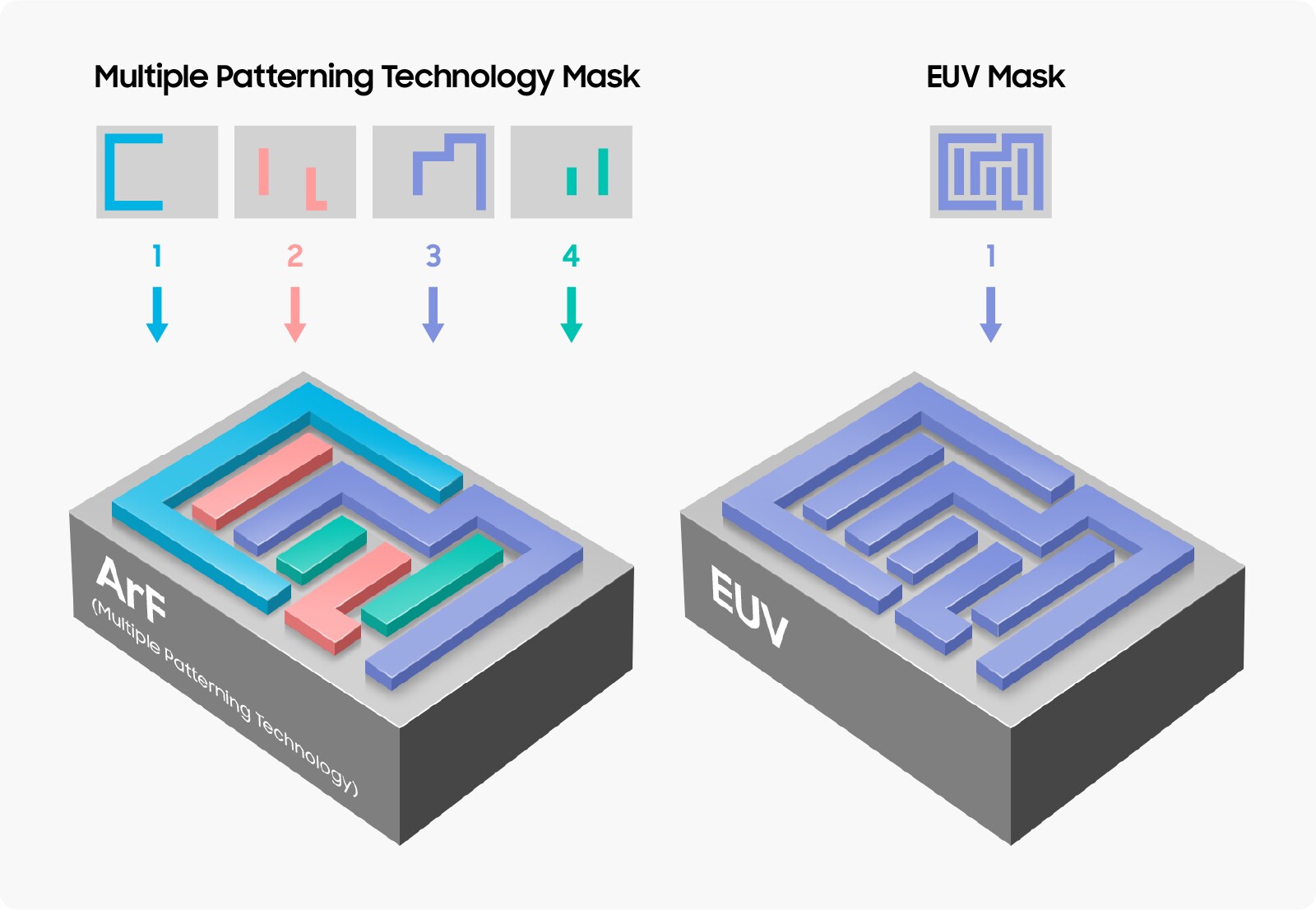

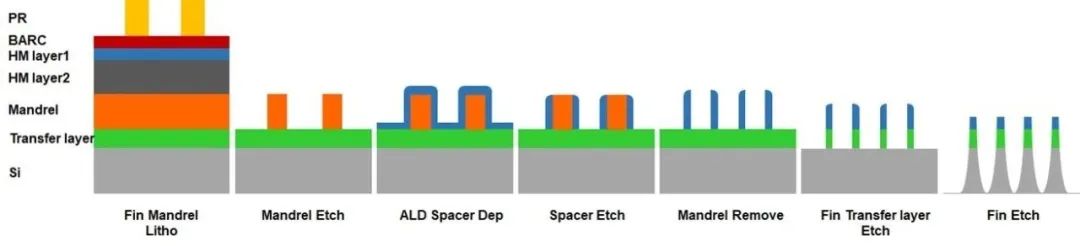

在前面的第一章博文中,我們介紹到,為了打破波長的局限性,一個圖案不得不分成幾次進行繪制。這就是 MPT (多重圖案技術,Multiple Patterning Technology)。MPT 技術雖然具有繪制小圖案的優勢,但如圖[9](a)所示,它的缺點是需要多個掩膜,而且需要進行多次工序操作。然而使用波長較短的 EUV 時,就可以像圖[9](b)一樣,僅通過一個掩膜和一次工序,便繪制出圖案。

圖[9] 使用四個相同掩膜進行繪制的 ArF 和僅使用一個掩膜進行繪制的 EUV。

這種改進具有時間、良率和費用上的優勢。

A. 時間 - 縮短了工序時間

在獲取結果的過程中,如果步驟增多,相應地,耗時也會變長。舉個簡單的例子來說明,圖[9]的(a)工廠做出一個面包需要四個小時,(b)工廠做一個面包則只需要一個小時。這是因為步驟的精簡大大提升了工序的速度。

B. 良率 - 降低污染,提高良率

多個步驟,就意味著相應存在多次污染的可能。比如白色黏土,反復揉捏,就容易變臟。在半導體工藝中,污染是導致良率降低的原因,而 EUV 可減少污染,從而起到提高良率的作用。

C. 費用 - 降低掩膜制作成本

制作掩膜也需要成本。原本的工藝需要制作多張掩膜,但使用 EUV 后,所需的掩膜會減少到一張,制作成本也相應減少。

4. 工欲善其事,必先利其器

如上所述,EUV 的出現給光刻工藝帶來了很大優勢,如今我們要做的,就是努力去探索如何才能更加有效地利用這一利器。

審核編輯黃宇

-

晶圓

+關注

關注

53文章

5415瀏覽量

132336 -

光刻

+關注

關注

8文章

364瀏覽量

31346 -

EUV

+關注

關注

8文章

615瀏覽量

88819

發布評論請先 登錄

光刻機的“精度錨點”:石英壓力傳感器如何守護納米級工藝

決戰納米級缺陷!東亞合成IXEPLAS納米離子捕捉劑如何助力先進封裝?

毫米行程柔性驅動壓電納米定位臺:超大行程,納米級精度

晶圓級MOSFET的直接漏極設計

在毫米級晶圓上,繪制納米級圖案

在毫米級晶圓上,繪制納米級圖案

評論