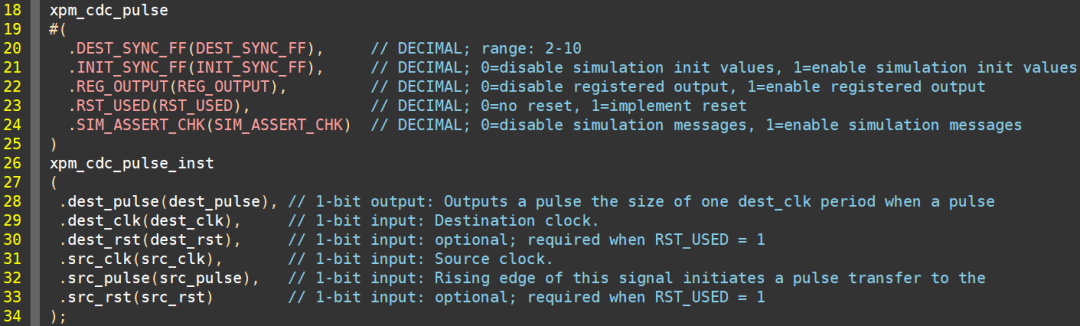

對于脈沖信號跨時鐘域,XPM_CDC提供了模塊xpm_cdc_pulse,如下圖所示。該模塊有5個參數(shù),其中參數(shù)DEST_SYNC_FF用于確定級聯(lián)觸發(fā)器的個數(shù);INIT_SYNC_FF用于確定仿真時是否使用觸發(fā)器初始值;

參數(shù)REG_OUTPUT用于確定是否對最終輸出信號寄存;參數(shù)RST_USED用于確定是否使用復位信號;參數(shù)SIM_ASSERT_CHK則用于確定是否顯示仿真信息。從輸入/輸出端口來看,源端時鐘域的輸入信號為src_pulse和src_rst;

目的端時鐘域的輸入信號為dest_rst,輸出信號為dest_pulse(src_pulse跨時鐘域后的結(jié)果)。

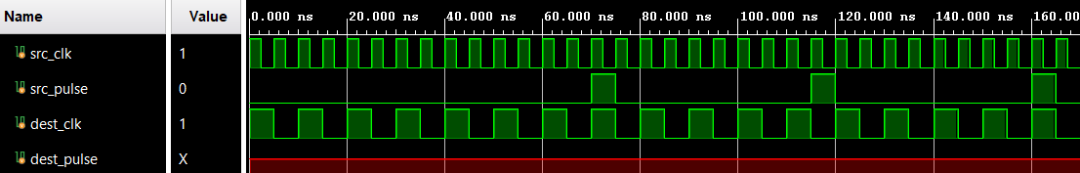

這些參數(shù)對仿真以及實際電路都有較大影響。如果參數(shù)INIT_SYNC_FF為0,同時RST_USED也為0,這就表明了仿真時不能使用同步寄存器鏈路的初始值,同時也沒有復位信號對其復位,這樣仿真時就會出現(xiàn)未知態(tài),如下圖所示。

審核編輯 :李倩

-

模塊

+關(guān)注

關(guān)注

7文章

2837瀏覽量

53283 -

電路設計

+關(guān)注

關(guān)注

6741文章

2702瀏覽量

219504 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2056瀏覽量

63397 -

脈沖信號

+關(guān)注

關(guān)注

6文章

408瀏覽量

38505 -

時鐘域

+關(guān)注

關(guān)注

0文章

53瀏覽量

10042

原文標題:跨時鐘域電路設計(4):單周期脈沖信號如何跨時鐘域

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

跨時鐘域電路設計:多位寬數(shù)據(jù)通過FIFO跨時鐘域

從處理單bit跨時鐘域信號同步問題來入手

如何處理跨時鐘域這些基礎問題

跨時鐘域電路設計:單周期脈沖信號如何跨時鐘域

跨時鐘域電路設計:單周期脈沖信號如何跨時鐘域

評論