3D IC 提供了一種實(shí)用的方法來保證全新水平的功率、性能、面積和功能。

隨著設(shè)計(jì)團(tuán)隊(duì)繼續(xù)開發(fā)新一代變革性產(chǎn)品,對(duì)計(jì)算的需求依然強(qiáng)勁。現(xiàn)代工作負(fù)載將封裝技術(shù)帶到了創(chuàng)新的前沿,并在產(chǎn)品性能、功能和成本方面突破了硅產(chǎn)品設(shè)計(jì)的界限。不久前,封裝技術(shù)還被認(rèn)為是不方便的后端流程。但時(shí)代變了,人工智能、大數(shù)據(jù)、云計(jì)算和自動(dòng)駕駛汽車的不斷進(jìn)步推動(dòng)了前所未有的計(jì)算極限(以及對(duì)封裝技術(shù)的需求)。

這種計(jì)算演進(jìn)導(dǎo)致了芯片的縮小和多芯片架構(gòu)的出現(xiàn),為 3D 硅堆疊和先進(jìn)封裝創(chuàng)新創(chuàng)造了前景廣闊的前景,以優(yōu)化系統(tǒng)性能。3D IC 提供了一種實(shí)用的方法來保證全新水平的功率、性能、面積和功能。

然而,正確的封裝選擇取決于許多因素,設(shè)計(jì)師需要幫助在無數(shù)可用的選項(xiàng)和方法中找到最佳路徑。為了加快未來 3D IC 的采用和生產(chǎn),半導(dǎo)體行業(yè)需要一個(gè)精簡的協(xié)作生態(tài)系統(tǒng),以在系統(tǒng)級(jí)提供一流的優(yōu)化。

仔細(xì)觀察 3D 堆疊

傳統(tǒng)上,半導(dǎo)體行業(yè)的主要參與者,如EDA、IP、基板、內(nèi)存和測試供應(yīng)商將專注于專業(yè)知識(shí)的支柱——而不會(huì)深入了解他們的工作如何影響芯片的整體集成和兼容性。這意味著團(tuán)隊(duì)不僅需要在前端使用不同的工具,還需要一個(gè)聯(lián)合的產(chǎn)品路線圖和所有相關(guān)方之間定義明確的溝通渠道。這種基本的前端和后端低效率增加了設(shè)計(jì)的復(fù)雜性,需要參與者之間進(jìn)行更多協(xié)作以減少后期集成,提高生產(chǎn)力水平并加強(qiáng)系統(tǒng)產(chǎn)品創(chuàng)新。

就堆疊本身而言,將多層晶體管封裝在不同尺寸的芯片上需要極高的精度。與過去不同的是,當(dāng)團(tuán)隊(duì)可以在系統(tǒng)測試階段拆焊印刷電路板上的故障芯片并用新芯片替換它(即使是堆疊的)時(shí),團(tuán)隊(duì)無法訪問組裝在 3D IC 結(jié)構(gòu)中的芯片。萬一出現(xiàn)錯(cuò)誤,就需要將成品放棄開始重建。

假設(shè)一家代工廠向其客戶發(fā)布了新的設(shè)計(jì)更新。當(dāng)客戶收到更新并將其發(fā)布給其 IP 供應(yīng)商時(shí),已經(jīng)浪費(fèi)了有意義的時(shí)間。火上澆油的是,相應(yīng)的IP準(zhǔn)備就緒大約需要六個(gè)月到一年的時(shí)間。在此過程中,如果相應(yīng)的 EDA 供應(yīng)商不知道代工廠的最新設(shè)計(jì)規(guī)則,則 EDA 工具最終對(duì)最新的設(shè)計(jì)更新無效——這對(duì)所有相關(guān)人員來說都是一個(gè)困難的局面。

EDA 工具依賴于互操作性,需要具有完整的端到端工具才能實(shí)現(xiàn)有效的 3D 多芯片系統(tǒng)集成。雖然這可能相對(duì)容易迎合單芯片設(shè)計(jì),但在 3D IC 架構(gòu)中相互堆疊的芯片之間的交互以及 EDA 工具識(shí)別芯片是否為 3D 堆疊都不是那么簡單。

加速設(shè)計(jì)成功

利用先進(jìn)的封裝技術(shù)實(shí)現(xiàn)異構(gòu)芯片集成已成為許多應(yīng)用的明顯趨勢(shì)。隨著不同行業(yè)計(jì)算密集型應(yīng)用的持續(xù)增長,3D IC 正在推動(dòng) HPC、汽車、物聯(lián)網(wǎng)和移動(dòng)用例的創(chuàng)新。

特定領(lǐng)域的小芯片為行業(yè)提供了難以置信的價(jià)值,盡管它們需要先進(jìn)的封裝讓團(tuán)隊(duì)有足夠的選擇來將晶圓堆疊在晶圓上或芯片堆疊在晶圓上以獲得更高的密度、更多的功能和更好的性能——同時(shí)保持相同或更小的占地面積。

這個(gè)機(jī)會(huì)拓寬了行業(yè)發(fā)展的可能性,同時(shí)應(yīng)對(duì)日益增加的芯片復(fù)雜性和設(shè)計(jì)尺寸。無論供應(yīng)商是否改變其商業(yè)模式,具有多層、多種芯片尺寸和多種功能的小芯片的集成和封裝對(duì)于釋放具有高計(jì)算能力和小尺寸的最終設(shè)計(jì)靈活性至關(guān)重要。

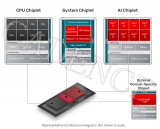

作為 3D 硅堆疊和先進(jìn)封裝技術(shù)的綜合系列,TSMC 3DFabric 補(bǔ)充了公司的先進(jìn)半導(dǎo)體技術(shù),以釋放系統(tǒng)級(jí)創(chuàng)新。臺(tái)積電的前端技術(shù)或 TSMC-SoIC(集成芯片系統(tǒng))提供當(dāng)今 3D 硅堆疊要求所需的精度和方法。為此,臺(tái)積電客戶在解決計(jì)算障礙方面有著獨(dú)特的見解。

AMD 是 3D 硅堆疊的先驅(qū),它就是這樣的客戶之一,它從巨大的性能改進(jìn)中受益。該公司通過與臺(tái)積電及其開放式創(chuàng)新平臺(tái) (OIP) 合作伙伴合作,率先推出了全球首款基于臺(tái)積電 SoIC 的 CPU,為下一代高性能、高能效芯片加速了強(qiáng)大的小芯片堆疊生態(tài)系統(tǒng)的開發(fā)。

轉(zhuǎn)變協(xié)作

沒有任何客戶或合作伙伴可以單槍匹馬地實(shí)現(xiàn)所需規(guī)模的系統(tǒng)級(jí)創(chuàng)新。生態(tài)系統(tǒng)(EDA、IP、DCA/VCA、內(nèi)存、OSAT、基板和測試)中所有芯片公司、設(shè)計(jì)合作伙伴和代工廠之間的有效協(xié)作對(duì)于開啟系統(tǒng)集成和產(chǎn)品創(chuàng)新的下一步至關(guān)重要。

臺(tái)積電認(rèn)識(shí)到加速 3D IC 生態(tài)系統(tǒng)創(chuàng)新和簡化執(zhí)行的必要性,于 2022 年 10 月推出了臺(tái)積電 3DFabric 聯(lián)盟,作為現(xiàn)有臺(tái)積電 OIP 的一部分。客戶和設(shè)計(jì)公司現(xiàn)在可以訪問該平臺(tái),以協(xié)作開發(fā)一流的 3D IC 解決方案,并通過更清晰的產(chǎn)品路線圖在第一時(shí)間獲得正確的設(shè)計(jì)。

與設(shè)計(jì)更大的單片芯片相比,這使更廣泛的生態(tài)系統(tǒng)能夠開發(fā)質(zhì)量更好的 3D IC 系統(tǒng)設(shè)計(jì)并實(shí)現(xiàn)更快的上市時(shí)間——最終大大加速 3D IC 客戶采用和生態(tài)系統(tǒng)準(zhǔn)備就緒。

隨著工作負(fù)載的發(fā)展,封裝技術(shù)和半導(dǎo)體的共同進(jìn)步非常重要。這種協(xié)作計(jì)劃的誕生為一個(gè)新的、可行的時(shí)代奠定了基礎(chǔ),這個(gè)時(shí)代可以處理復(fù)雜的工藝節(jié)點(diǎn),并為各種應(yīng)用和領(lǐng)域提供先進(jìn)的 3D IC 設(shè)計(jì)解決方案。

展望未來,臺(tái)積電希望看到公司從只專注于設(shè)計(jì)芯片轉(zhuǎn)變?yōu)閲@系統(tǒng)級(jí)集成實(shí)施全面、全面的方法,以實(shí)現(xiàn)新水平的產(chǎn)品創(chuàng)新。與此同時(shí),我們將繼續(xù)盡一切努力為行業(yè)打開新的大門,在這個(gè)充滿希望的空間繼續(xù)創(chuàng)新。

審核編輯:劉清

-

TSMC

+關(guān)注

關(guān)注

3文章

179瀏覽量

86983 -

EDA工具

+關(guān)注

關(guān)注

5文章

276瀏覽量

34109 -

VoIP

+關(guān)注

關(guān)注

1文章

146瀏覽量

42995 -

HPC

+關(guān)注

關(guān)注

0文章

348瀏覽量

25056

原文標(biāo)題:3D IC生態(tài)系統(tǒng)協(xié)作的重要性

文章出處:【微信號(hào):ICViews,微信公眾號(hào):半導(dǎo)體產(chǎn)業(yè)縱橫】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

愛立信攜手蘋果和聯(lián)發(fā)科技加速構(gòu)建6G生態(tài)系統(tǒng)

3D IC設(shè)計(jì)中的信號(hào)完整性與電源完整性分析

IC引腳失效模式和影響分析(FMEA)的重要性

米爾RK3576成功上車!ROS2 Humble生態(tài)系統(tǒng)體驗(yàn)

探索HD3SS460:USB Type-C生態(tài)系統(tǒng)的高性能復(fù)用解決方案

Ceva 添加 Sensory 的 TrulyHandsfree 語音激活功能, 增強(qiáng) NeuPro-Nano NPU 生態(tài)系統(tǒng)

Cadence推出全新完整小芯片生態(tài)系統(tǒng)

HD3SS460:USB Type - C 生態(tài)系統(tǒng)的多功能復(fù)用解決方案

一文掌握3D IC設(shè)計(jì)中的多物理場效應(yīng)

威宏科技加入Arm Total Design生態(tài)系統(tǒng),攜手推動(dòng)AI與HPC芯片創(chuàng)新

BPI-AIM7 RK3588 AI與 Nvidia Jetson Nano 生態(tài)系統(tǒng)兼容的低功耗 AI 模塊

使用OpenUSD實(shí)現(xiàn)可互操作3D工作流(下)

使用OpenUSD實(shí)現(xiàn)可互操作3D工作流(上)

3D打印設(shè)備為何需要專用濾波器?一文讀懂其重要性

如何借助大語言模型打造人工智能生態(tài)系統(tǒng)

淺析3D IC生態(tài)系統(tǒng)協(xié)作的重要性

淺析3D IC生態(tài)系統(tǒng)協(xié)作的重要性

評(píng)論