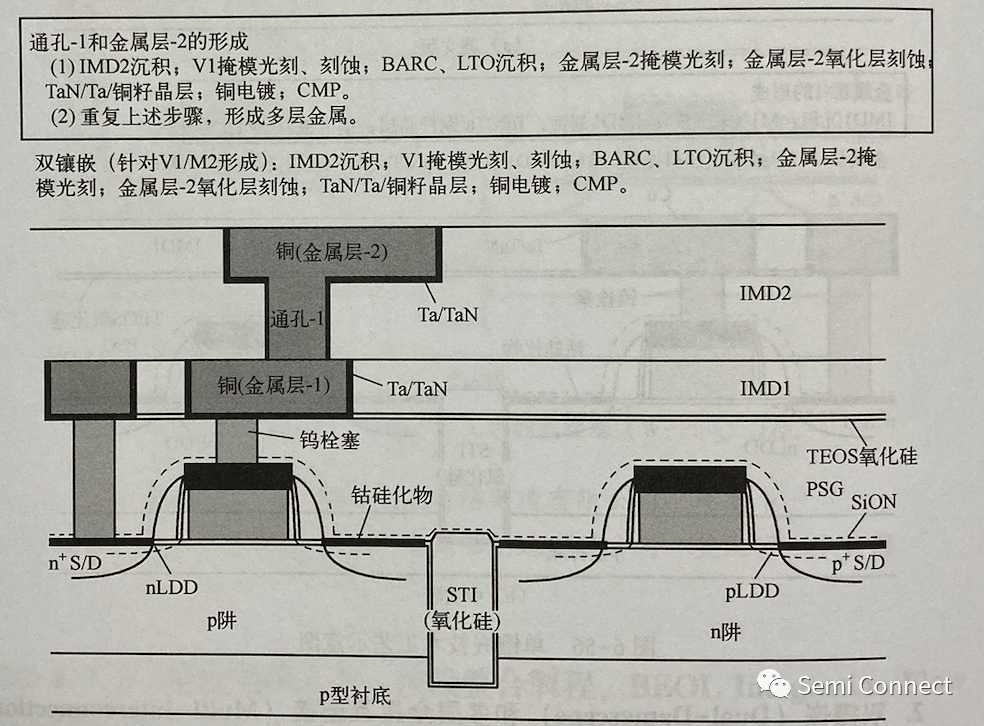

雙鑲嵌 (Dual-Damascene)和多層金屬互連接 (Multi-Interconnection)通孔-1(V1)和金屬-2 (M2)互連的形成是通過雙鑲嵌 (Dual -Damascene)工藝實現的,如圖所示。

雙鑲嵌工藝分為先通孔 (Via-First) 和先溝槽(Trench-First)兩種技術。以先通孔技術為例,首先沉積IMD2層(如 SiCN層,厚度約為 50nm,含碳低kPECVD 氧化硅黑金剛石層厚度約為 600nm),然后形成V1的圖形并進行刻蝕。多層IMD1 的主要作用是提供良好的密封和覆蓋更加多孔的低k介質。 為了平坦化,需要在通孔中填充底部抗反射涂層 (Bottom-Ani-Rellective Coatings, BARC),并沉積一層 LTO (Low Temperature Oxide)。隨后形成M2 的圖形并刻蝕氧化物,去除 BARC 并清洗后,沉積 Ta / TaN 阻擋層和 Cu 籽晶層,隨后進行 Cu 填充(使用 ECP 法),并進行 CMP 平坦化,這樣 M2 互連就形成了。 通過重復上述步驟,可以實現多層銅互連。相應的,先溝槽技術的雙鑲嵌工藝就是先實施 M2 溝槽制備再形成 V1 的圖形并刻蝕氧化物,然后沉積阻擋層和籽晶層,最后進行 Cu 填充和 CMP 平坦化。

審核編輯 :李倩

-

工藝

+關注

關注

4文章

713瀏覽量

30252 -

金屬

+關注

關注

1文章

621瀏覽量

25129

原文標題:后段集成工藝(BEOL Integration Flow)- 2

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

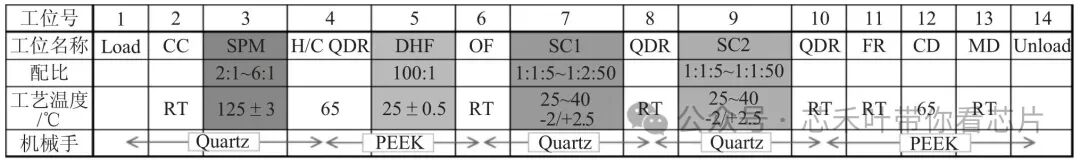

集成電路制造中常用濕法清洗和腐蝕工藝介紹

芯片引腳成型與整形:電子制造中不可或缺的兩種精密工藝

鋰電池制造:電芯后段處理中的除氣工藝

FLOW Digital Infrastructure宣布在東京市中心新建數據中心

半導體分層工藝的簡單介紹

半導體封裝工藝流程的主要步驟

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

CMOS集成電路的基本制造工藝

后段集成工藝(BEOL Integration Flow)- 2

后段集成工藝(BEOL Integration Flow)- 2

評論