自UCIe產業聯盟這一推進Chiplet互聯生態的組織成立以來,采用Chiplet這種新興設計方式的解決方案就迎來了井噴的趨勢。根據Omdia的預計,全球Chiplet市場將在2024年增長至58億美元,并在2035年達到570億美元。

在這個潛力十足的市場面前,相關標準也在不斷出爐,近日,國內集成電路相關企業及專家共同主導制定的《小芯片接口總線技術要求》團隊標準在完成意見征求后,也正式通過了工信部中國電子工業標準化技術協會的審定。

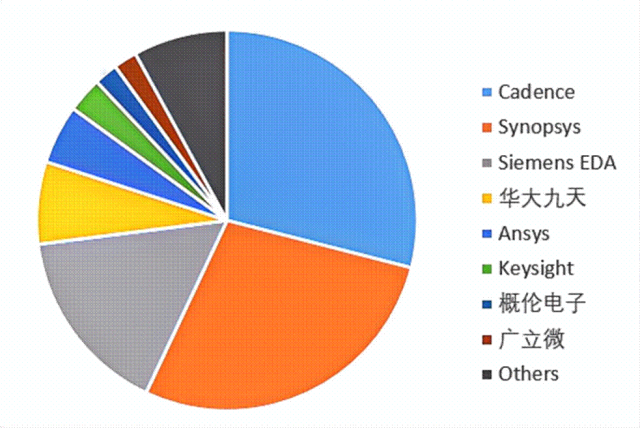

而在推進Chiplet普及的努力中,不僅有微軟、Meta和谷歌這類促進者成員,還有IP廠商和EDA廠商作為貢獻營收的主力軍。除了快速布局的國際IP和EDA廠商以外,國內廠商也紛紛開啟了自己的Chiplet進程。

IP廠商紛紛開啟了Chiplet轉型

芯原作為大陸排名第一、全球排名第7的半導體IP供應商,自然也不會錯過這股Chiplet大潮。早在2021年,芯原科技在接受機構調研時,就表示他們已經開始與全球頂尖的晶圓廠開啟基于5nmChiplet的項目合作,基于Arm架構的CPU IP Chiplet已經進入了芯片設計階段,而用于AI運算的NPU IP Chiplet也已經進入了設計與實現階段。

?

?

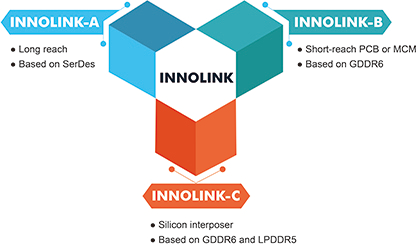

InnolinkChiplet方案/ 芯動科技

在Chiplet標準化道路上走得比較靠前的國內IP廠商當屬芯動科技,早在2020年,芯動科技就和清華交叉院、紫光存儲等企業共同發起了Chiplet產業聯盟,同時推出了自己的InnolinkChiplet。根據芯動科技的描述,其InnolinkPHY和ControllerChiplet方案在物理層上可兼容UCIe協議,而且已經獲得了Silicon驗證,最高可支持3.4Tbps/mm2的帶寬效率密度,以低功率小面積實現更大的互聯帶寬,非常適合用于高性能ASIC/FPGA硬件設計中。

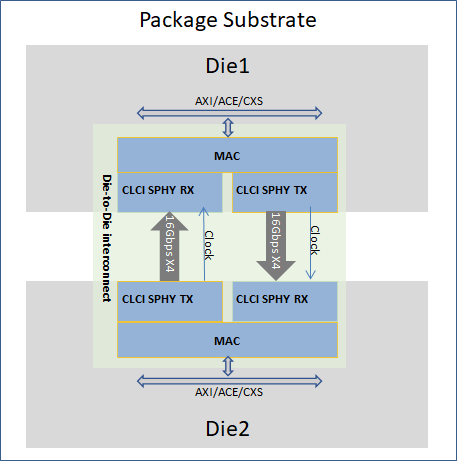

同樣加入UCIe產業聯盟的IP企業還有超摩科技,超摩科技的錦雷3200是專為Chiplet互聯打造的die-to-dieSPHY IP,這也是超摩科技第一代Chiplet互聯IP產品。參數上來看,錦雷3200可以做到每通道16Gbps的數據速率,在沒有ECC的情況下做到小于10到15的BER。

?

?

錦雷3200 Chiplet架構/ 超摩科技

錦雷3200選擇了臺積電N12這一工藝節點,其ChipletD2D互聯樣片已經流片并完成了初步測試。從應用場景上來看,超摩科技給錦雷3200的定位包括云端計算、人工智能、數據通信和自動駕駛,都是需要高傳輸速率的場景。在超摩科技自己推出的企業級高性能CPU觀云9000中,也用到了Chiplet的設計方法。

追求先進封裝的EDA廠商開始發力Chiplet

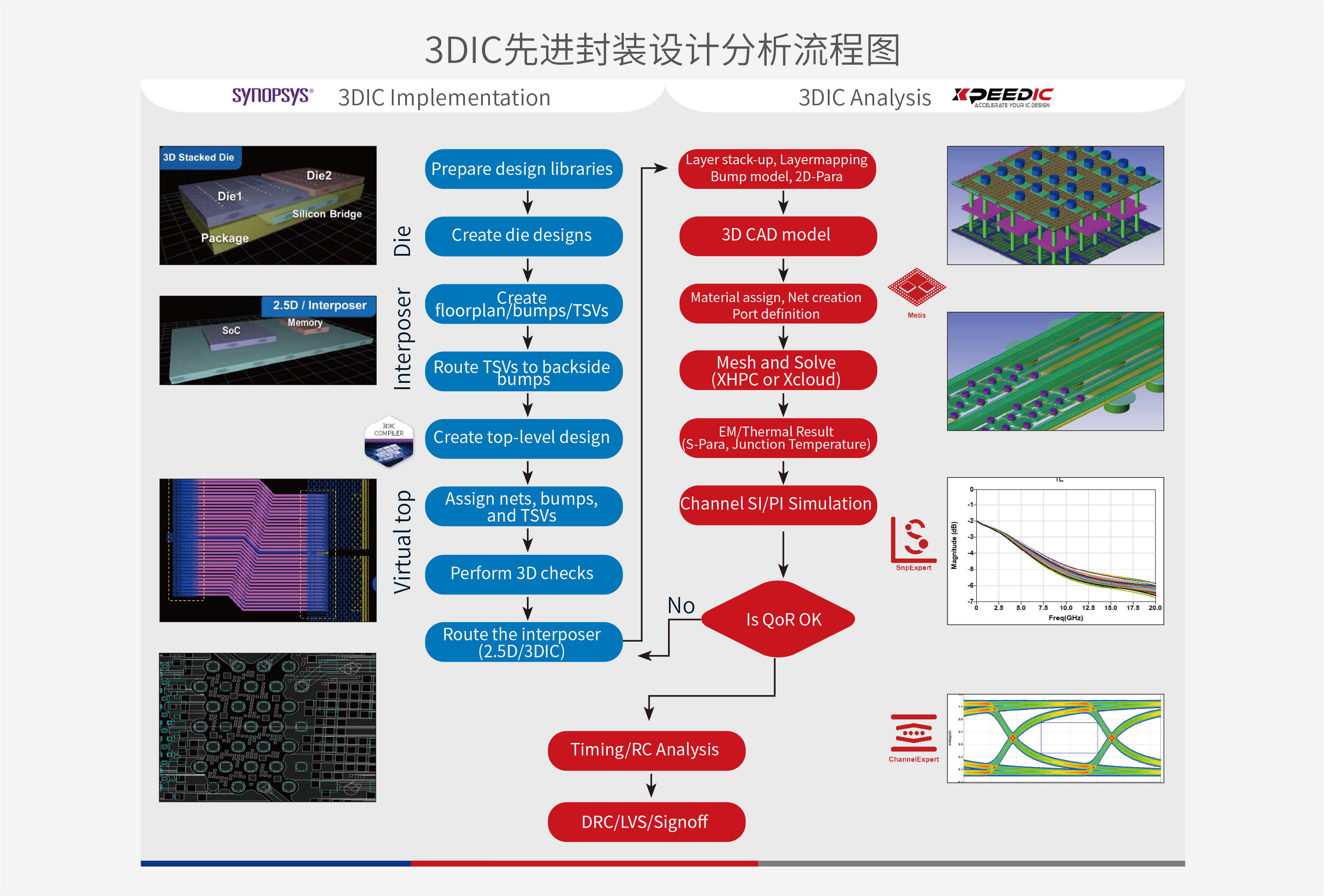

為了實現Chiplet的設計,同樣需要EDA廠商出力,在設計工具層面上支持Chiplet。芯和半導體作為擁有3DIC先進封裝設計分析全流程EDA的企業,也成了首家加入UCIe產業聯盟的國產EDA廠商。

?

?

3DIC先進封裝設計分析全流程EDA平臺/ 芯和半導體

芯和半導體的3DIC先進封裝設計分析全流程EDA平臺,是業界首個用于3DIC多芯片系統設計分析的統一平臺,集成了新思科技3DIC Complier和芯和半導體的Metis,做到了2.5D/3D先進封裝的系統設計和仿真分析,全面支持2.5D Interposer、3DIC和Chiplet設計,也支持臺積電和三星的先進封裝工藝節點。

同樣開始發力Chiplet的EDA廠商還有合見工軟。要應對Chiplet在先進封裝的挑戰,必須打破在復雜多維空間系統級設計互連,實現數據的一致性和信號、電源、熱、應力的完整性。為此合見工軟在去年發布了先進封裝協同設計環境(UniVistaIntegrator,簡稱UVI)之后,又在今年6月推出了UVI功能增強版。

UVI功能增強版首次真正意義上實現了系統級Sign-off功能,可在同一設計環境中導入多種格式的IC、Interposer、Package和PCB數據,支持全面的系統互連一致性檢查(System-Level LVS),同時在檢查效率、圖形顯示、靈活度與精度上都有大幅提升。

小結

除了以上提到的這些廠商之外,還有芯云凌、牛芯半導體、長鑫存儲等企業也都紛紛加入了UCIe產業聯盟。可以看出,對于國內專注于高速接口等高性能IP廠商和先進3D封裝的EDA廠商來說,Chiplet的出現是一個不可多得的機遇。

芯片設計公司為了進一步減少成本加快上市時間,重復利用Chiplet的頻率會逐步提高。但目前Chiplet仍主要用于復雜的高端芯片設計中,所用工藝也基本在5nm到16nm之間,隨著未來制造成本進一步降低的話,相信會有更多的IP授權廠商完成Chiplet供應商的轉型。

-

IP

+關注

關注

5文章

1850瀏覽量

155036 -

eda

+關注

關注

72文章

3079瀏覽量

181671 -

chiplet

+關注

關注

6文章

485瀏覽量

13528

發布評論請先 登錄

英諾達ELPC榮登國產EDA“口碑榜”

【書籍評測活動NO.69】解碼中國”芯“基石,洞見EDA突圍路《芯片設計基石——EDA產業全景與未來展望》

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

合見工軟與紫光同創合作推動國產EDA和FPGA產業快速發展

智多晶EDA工具HqFpga軟件的主要重大進展

國產EDA又火了,那EDA+AI呢?國產EDA與AI融合發展現狀探析

國產EDA的AI進程究竟到哪一步了

Chiplet與先進封裝全生態首秀即將登場!匯聚產業鏈核心力量共探生態協同新路徑!

創造歷史,首家獲得工博會CIIF大獎的國產EDA誕生

創造歷史,芯和半導體成為首家獲得工博會CIIF大獎的國產EDA

九霄智能國產EDA工具的突圍之路

突發!全球三大家EDA斷供大陸,國產EDA崛起?

從技術封鎖到自主創新:Chiplet封裝的破局之路

Chiplet與先進封裝設計中EDA工具面臨的挑戰

從IP到EDA,國產Chiplet生態進展如何?

從IP到EDA,國產Chiplet生態進展如何?

評論