RMK-7-81+是一款性價(jià)比高的X7倍頻器,它采用了特別選擇的硅肖特基二極管濾波器電路以實(shí)現(xiàn)低轉(zhuǎn)換損耗,但在其F7輸出附近具有對(duì)不希望的諧波的高抑制。它使RMK-7-81+是廣泛應(yīng)用的理想選擇。小塑料盒,0.25“x 0.31”x 0.16“高,可水洗符合RoHS。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

濾波器

+關(guān)注

關(guān)注

162文章

8411瀏覽量

185679 -

乘法器

+關(guān)注

關(guān)注

9文章

221瀏覽量

38803

原文標(biāo)題:RMK-7-81+7X SMT乘法器,輸出頻率52.5-80.5 MHz

文章出處:【微信號(hào):兆億微波,微信公眾號(hào):兆億微波】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

CDCVF25084:高性能時(shí)鐘乘法器的深度剖析

(PLL)時(shí)鐘乘法器。它利用PLL技術(shù),能精確地將輸出時(shí)鐘的頻率和相位與輸入時(shí)鐘信號(hào)對(duì)齊,并且具有四倍的乘法因子。該器件的標(biāo)稱電源

LMK04906:超低噪聲時(shí)鐘抖動(dòng)清理器與乘法器的深度剖析

LMK04906:超低噪聲時(shí)鐘抖動(dòng)清理器與乘法器的深度剖析 在電子設(shè)計(jì)領(lǐng)域,時(shí)鐘抖動(dòng)清理器與乘法器對(duì)于確保系統(tǒng)時(shí)鐘信號(hào)的穩(wěn)定性和準(zhǔn)確性至關(guān)重要。今天,我們就來(lái)深入探討德州儀器(TI

低成本模擬乘法器AD633:特性、應(yīng)用與設(shè)計(jì)指南

到各種應(yīng)用場(chǎng)景,為大家呈現(xiàn)一個(gè)全面的設(shè)計(jì)指南。 文件下載: AD633.pdf 一、AD633 概述 AD633是一款功能完備的四象限模擬乘法器,它集成了高阻抗差分X和Y輸入,以及高阻抗求和輸入(Z)。其低阻抗輸出電壓由一個(gè)埋入

高性能模擬乘法器AD834:特點(diǎn)、應(yīng)用與設(shè)計(jì)要點(diǎn)

高性能模擬乘法器AD834:特點(diǎn)、應(yīng)用與設(shè)計(jì)要點(diǎn) 引言 在電子工程師的日常工作中,高性能模擬乘法器是實(shí)現(xiàn)各種復(fù)雜信號(hào)處理和計(jì)算的關(guān)鍵元件。AD834作為一款備受矚目的模擬乘法器,具有高帶寬、低失真等

AD532:高性能單芯片乘法器/除法器的卓越之選

AD532:高性能單芯片乘法器/除法器的卓越之選 在電子設(shè)計(jì)領(lǐng)域,乘法器和除法器是實(shí)現(xiàn)復(fù)雜運(yùn)算和信號(hào)處理的關(guān)鍵組件。而AD532作為一款預(yù)微調(diào)的單芯片

使用Xilinx 7系列FPGA的四位乘法器設(shè)計(jì)

(Shinshu University)研究團(tuán)隊(duì)的最新設(shè)計(jì)中,一個(gè)專為 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了僅 11 個(gè) LUT + 2 個(gè) CARRY4 塊,關(guān)鍵路徑延遲達(dá)到 2.75 ns。這是一次令人印象深刻的工藝優(yōu)化實(shí)踐。

E203在基于wallace樹(shù)+booth編碼的乘法器優(yōu)化后的跑分結(jié)果

和rs2寄存器輸入乘法操作數(shù),乘法器進(jìn)行乘法操作,2th輸出乘法結(jié)果)。

目前優(yōu)化后的乘法器

發(fā)表于 10-27 07:54

E203V2長(zhǎng)周期乘法器核心booth算法解讀

低位部分和從第一次開(kāi)始便從32位寄存器高位開(kāi)始右移兩位,以此類推,進(jìn)行16次加法運(yùn)算后,高位部分和已經(jīng)算出來(lái)了,而低位部分和剛好右移到寄存器的最低位,最后還需一個(gè)時(shí)鐘周期輸出乘法器的運(yùn)算結(jié)果。

同時(shí)

發(fā)表于 10-24 09:33

改進(jìn)wallance樹(shù)乘法器優(yōu)化方法

周期復(fù)用加法器的部分積加和算法,我們采用了改進(jìn)的wallance樹(shù)結(jié)構(gòu)進(jìn)行部分積的快速壓縮,實(shí)現(xiàn)了單周期的乘法計(jì)算。

經(jīng)過(guò)時(shí)序分析,我們的單周期乘法器時(shí)鐘頻率可以提高至140Hz,對(duì)比

發(fā)表于 10-23 06:37

關(guān)于E203內(nèi)核高性能乘法器優(yōu)化(一)

。而采用線性陣列乘法器壓縮9個(gè)部分積需要7級(jí)CSA壓縮,消耗7個(gè)延時(shí)單位,且Wallace樹(shù)形乘法器消耗的CSA單元數(shù)量相對(duì)于線性陣列乘法器

發(fā)表于 10-23 06:09

蜂鳥(niǎo)乘法器設(shè)計(jì)分享

蜂鳥(niǎo)的乘法器主體設(shè)計(jì)在ALU模塊的子單元MDV模塊中,MDV模塊包括乘除法器邏輯設(shè)計(jì),它只包含運(yùn)算控制,但并不包含具體運(yùn)算,它們都需要將部分積或者部分余數(shù)傳入數(shù)據(jù)通路(dpath模塊)中,從而實(shí)現(xiàn)

發(fā)表于 10-22 08:21

蜂鳥(niǎo)E203乘法器改進(jìn)

連續(xù)不斷的輸出,不會(huì)像循環(huán)移位那樣,需計(jì)算完才輸出,中間沒(méi)有等待時(shí)間。流水線乘法器

大大提高了計(jì)算效率,但是占用資源也隨即增加。因此將此乘法器用在蜂鳥(niǎo)E203,亦能提高數(shù)據(jù)計(jì)算效率。

發(fā)表于 10-22 07:28

蜂鳥(niǎo)E203內(nèi)核乘法器的優(yōu)化

乘法器的優(yōu)化實(shí)現(xiàn)一般從兩個(gè)方面入手。第一是減少生成的部分積數(shù)量,另外就是減少部分積累加的延時(shí)。

在開(kāi)源的E203源碼中,32*32乘法器是利用radix-4 booth編碼產(chǎn)生部分積,每個(gè)周期做一次

發(fā)表于 10-22 06:11

優(yōu)化boot4乘法器方法

數(shù)據(jù)存儲(chǔ)在片上存儲(chǔ)器中,可以減少輸入/輸出延遲,從而縮短乘法器的運(yùn)算周期。

采用流水線技術(shù):使用流水線技術(shù)將乘法操作分成多個(gè)階段,使每個(gè)階段的操作可以在不同的時(shí)鐘周期內(nèi)完成,從而并行化運(yùn)算流程,提高

發(fā)表于 10-21 12:13

ADL5390 RF矢量乘法器技術(shù)手冊(cè)

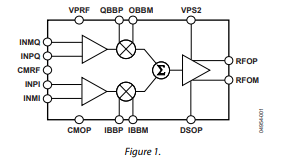

ADL5390矢量乘法器由一對(duì)匹配的寬帶可變?cè)鲆娣糯笃鹘M成,二者輸出相加,每個(gè)放大器具有單獨(dú)的線性幅度增益控制。如果兩個(gè)輸入RF信號(hào)正交,則可以將該矢量乘法器配置為矢量調(diào)制器,或?qū)⒃鲆婵刂埔_用作

RMK-7-81+7X SMT乘法器,輸出頻率52.5-80.5 MHz

RMK-7-81+7X SMT乘法器,輸出頻率52.5-80.5 MHz

評(píng)論