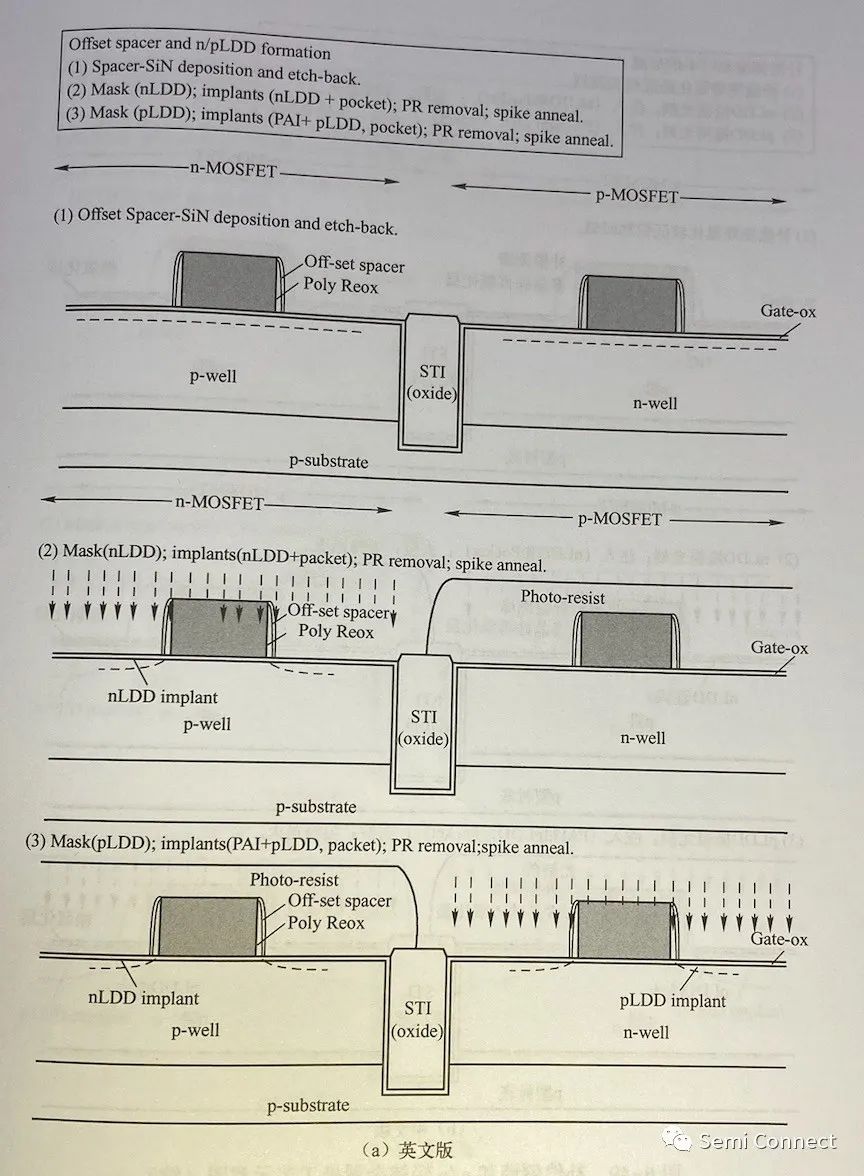

補償側墻 (Offset Spacer)和n/p 輕摻雜漏極 (n/ pLDD)工藝

補償側墻和 n/p 輕摻雜漏極工藝示意圖如圖所示。

首先沉積一薄層氮化硅或氮氧化硅(通常約2nm),然后進行回刻蝕(etch-Back),在柵的側壁上形成一個薄層側墻(Spacer)。在補償側墻刻蝕后,剩下的氧化層厚度約為 2nm。 在硅表面保留的這一層氧化層,在后續每步工藝中將發揮重要的保護作用。補償側墻用于隔開和補償由于 LDD 離子注入(為了減弱短溝道效應)引起的橫向擴散,對于 45nm/28nm 或更先進的節點,這一步是必要的。 然后分別對n-MOS和 p-MOS 進行輕摻雜漏極(LDD)離子注入。完成離子注入后,用尖峰退火(Spike Anneal)技術去除缺陷并激活 LDD 注入的雜質。nLDD 和pLDD離子注入的順序、能量、劑量,以及尖峰退火或 RTA 的溫度,對晶體管的性能都有重要的影響。

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

LDD

+關注

關注

0文章

13瀏覽量

12990 -

氧化層

+關注

關注

0文章

4瀏覽量

5789

原文標題:前段集成工藝(FEOL)-4

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

集成電路制造中薄膜生長工藝的發展歷程和分類

薄膜生長是集成電路制造的核心技術,涵蓋PVD、CVD、ALD及外延等路徑。隨技術節點演進,工藝持續提升薄膜均勻性、純度與覆蓋能力,支撐銅互連、高k柵介質及應變器件發展。未來將聚焦低溫沉積、三維結構適配與新材料集成,實現性能與可靠

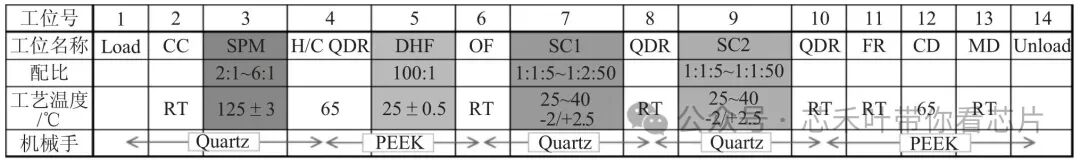

集成電路制造中常用濕法清洗和腐蝕工藝介紹

集成電路濕法工藝是指在集成電路制造過程中,通過化學藥液對硅片表面進行處理的一類關鍵技術,主要包括濕法清洗、化學機械拋光、無應力拋光和電鍍四大類。這些工藝貫穿于芯片制造的多個關鍵環節,直

集成電路制造中薄膜刻蝕的概念和工藝流程

薄膜刻蝕與薄膜淀積是集成電路制造中功能相反的核心工藝:若將薄膜淀積視為 “加法工藝”(通過材料堆積形成薄膜),則薄膜刻蝕可稱為 “減法工藝”(通過材料去除實現圖形化)。通過這一 “減”

半導體外延工藝在哪個階段進行的

半導體外延工藝主要在集成電路制造的前端工藝(FEOL)階段進行。以下是具體說明:所屬環節定位:作為核心步驟之一,外延屬于前端制造流程中的關鍵環節,其目的是在單晶襯底上有序沉積單晶材料以

半導體分層工藝的簡單介紹

在指甲蓋大小的硅片上建造包含數百億晶體管的“納米城市”,需要極其精密的工程規劃。分層制造工藝如同建造摩天大樓:先打地基(晶體管層),再逐層搭建電路網絡(金屬互連),最后封頂防護(封裝層)。這種將芯片分為FEOL(前道工序) 與 BEOL(后道工序) 的智慧,正是半導體工業

半導體封裝工藝流程的主要步驟

半導體的典型封裝工藝流程包括芯片減薄、芯片切割、芯片貼裝、芯片互連、成型固化、去飛邊毛刺、切筋成型、上焊錫、打碼、外觀檢查、成品測試和包裝出庫,涵蓋了前段(FOL)、中段(EOL)、電鍍(plating)、后段(EOL)以及終測(final test)等多個關鍵環節。

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

ME-Pro是概倫電子自主研發的用于聯動集成電路工藝與設計的創新性驗證評估平臺,為集成電路設計、CAD、工藝開發、SPICE模型和PDK專業從業人員提供了一個共用平臺。

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

的工藝模型概況,用流程圖將硅片制造的主要領域連接起來;具體講解每一個主要工藝;集成電路裝配和封裝的后部工藝概況。此外,各章為讀者提供了關于質量測量和故障排除的問題,這些都是會在硅片制造

發表于 04-15 13:52

前段集成工藝(FEOL)-4

前段集成工藝(FEOL)-4

評論